本公开涉及一种多层电子组件。

背景技术:

1、多层陶瓷电容器(mlcc,一种多层电子组件)可以是安装在诸如成像装置(包括液晶显示器(lcd)或等离子体显示面板(pdp))、计算机、智能电话或移动电话的各种电子产品中的任意一种的印刷电路板上以用于在其中充电或从其放电的片式电容器。

2、多层陶瓷电容器具有小尺寸,实现高电容,并且容易安装在电路板上,因此可用作各种电子装置的组件。由于诸如计算机和移动装置的各种类型的电子装置具有更小的尺寸和更高的输出,因此对多层陶瓷电容器具有更小的尺寸和更高的电容的需求不断增加。

3、此外,近年来,随着对电子产品的行业兴趣的增加,需要多层陶瓷电容器具有高可靠性特性以用于汽车和信息娱乐系统。

4、为了实现多层陶瓷电容器的小型化和高电容,需要通过形成薄的内电极和介电层来增加层叠的层数,并且需要显著减小不影响电容形成的部分的体积以增加实现电容所需的有效体积分数。

5、此外,需要显著减小安装空间以在板的有限区域中安装尽可能多的组件。

技术实现思路

1、本公开的一方面在于提供一种具有改善的每单位体积电容的多层电子组件。

2、本公开的一方面在于提供一种能够使安装空间最小化的多层电子组件。

3、本公开的一方面在于提供一种具有改善的可靠性的多层电子组件。

4、然而,本公开的目的不限于上述内容,并且在描述本公开的具体实施例的过程中将更容易理解。

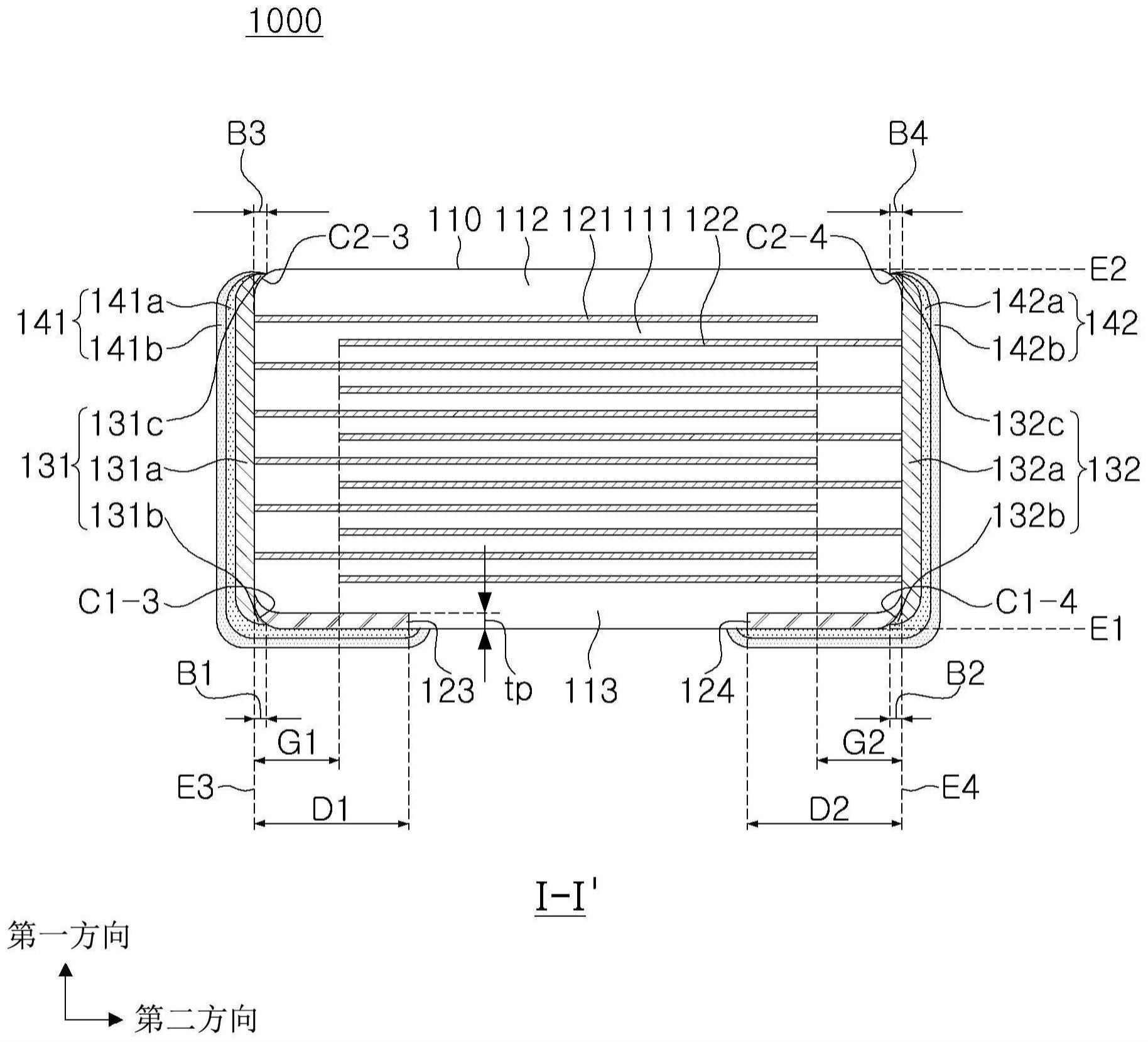

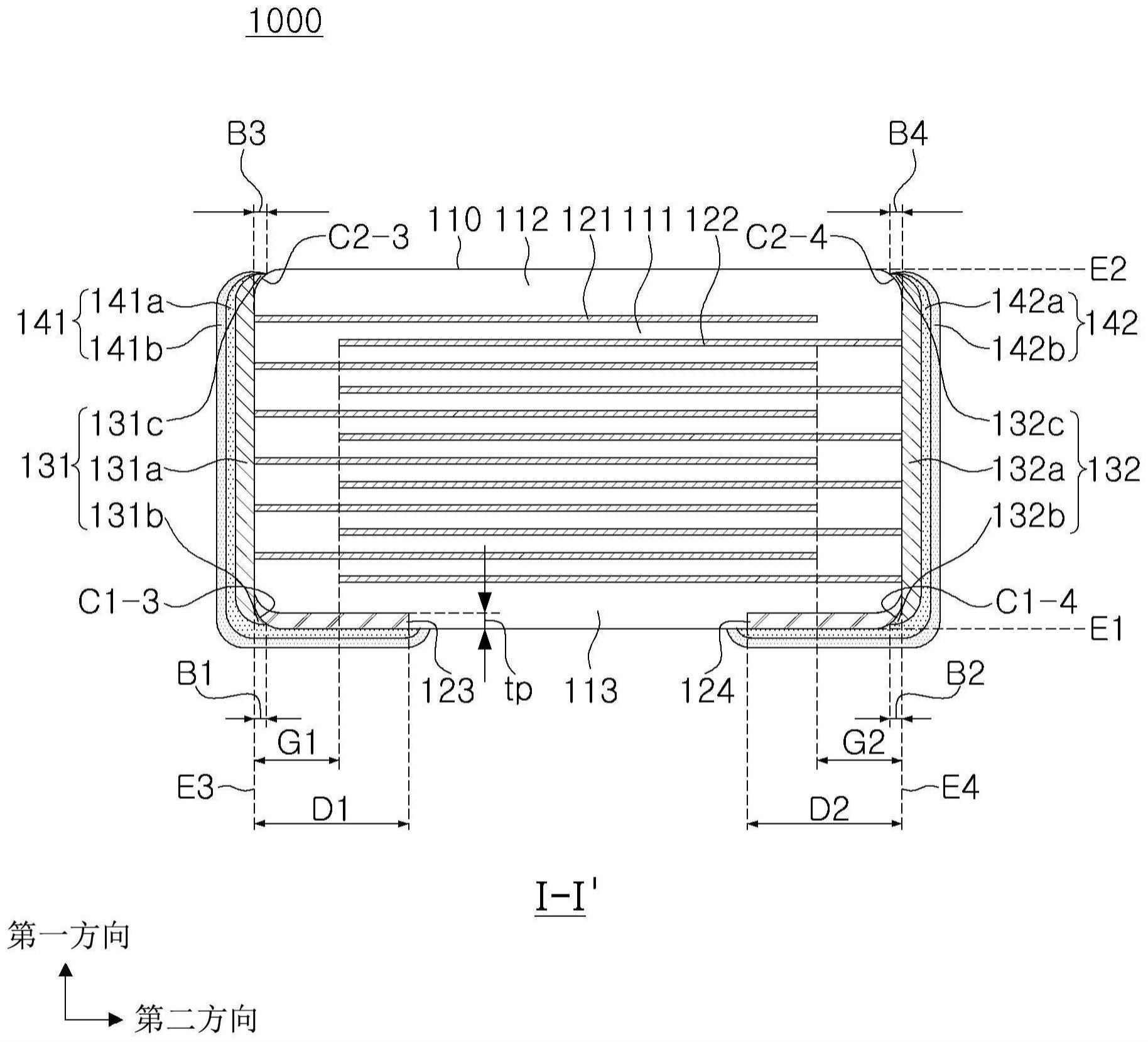

5、根据本公开的一方面,一种多层电子组件可包括:主体,包括介电层以及第一内电极和第二内电极,所述第一内电极和所述第二内电极交替设置且所述介电层介于所述第一内电极和所述第二内电极之间,所述主体具有在第一方向上彼此相对的第一表面和第二表面、连接到所述第一表面和所述第二表面并在第二方向上彼此相对的第三表面和第四表面、以及连接到所述第一表面至所述第四表面并在第三方向上彼此相对的第五表面和第六表面,所述第一表面包括设置为彼此间隔开的第一带电极和第二带电极;第一外电极,设置在所述第三表面上并连接到所述第一内电极和所述第一带电极;第二外电极,设置在所述第四表面上并连接到所述第二内电极和所述第二带电极;第一镀层,设置在所述第一外电极和所述第一带电极上;以及第二镀层,设置在所述第二外电极和所述第二带电极上。

6、根据本公开的一方面,一种多层电子组件可包括:主体,包括介电层以及第一内电极和第二内电极,所述第一内电极和所述第二内电极交替设置且所述介电层介于所述第一内电极和所述第二内电极之间,所述主体具有在第一方向上彼此相对的第一表面和第二表面、连接到所述第一表面和所述第二表面并在第二方向上彼此相对的第三表面和第四表面、以及连接到所述第一表面至所述第四表面并在第三方向上彼此相对的第五表面和第六表面,所述第一表面包括设置为彼此间隔开的第一带电极和第二带电极;第一外电极,设置在所述第三表面上并连接到所述第一内电极和所述第一带电极;第二外电极,设置在所述第四表面上并连接到所述第二内电极和所述第二带电极;第一绝缘层,设置在所述第一外电极上;第二绝缘层,设置在所述第二外电极上;第一镀层,设置在所述第一带电极上;以及第二镀层,设置在所述第二带电极上。

技术特征:1.一种多层电子组件,包括:

2.根据权利要求1所述的多层电子组件,其中,所述第一带电极与所述第三表面相接,并且所述第二带电极与所述第四表面相接。

3.根据权利要求1所述的多层电子组件,其中,所述第一带电极和所述第二带电极具有0.1μm或更大的平均厚度。

4.根据权利要求1所述的多层电子组件,其中,所述第一带电极和所述第二带电极与所述第一表面基本上共面。

5.根据权利要求1所述的多层电子组件,其中,所述第一带电极和所述第二带电极设置为嵌在所述第一表面中。

6.根据权利要求1所述的多层电子组件,其中,所述第一带电极和所述第二带电极包括ni、cr、pd和pt中的至少一种。

7.根据权利要求1所述的多层电子组件,其中,所述第一带电极和所述第二带电极包括batio3、tio2和sio2中的至少一种。

8.根据权利要求1所述的多层电子组件,其中,满足d1≥g1和d2≥g2,其中,d1是在所述第二方向上从所述第三表面的延长线到所述第一带电极的端部的平均尺寸,d2是在所述第二方向上从所述第四表面的延长线到所述第二带电极的端部的平均尺寸,g1是所述第三表面和所述第二内电极彼此间隔开的区域在所述第二方向上的平均尺寸,并且g2是所述第四表面和所述第一内电极彼此间隔开的区域在所述第二方向上的平均尺寸。

9.根据权利要求1所述的多层电子组件,其中,满足0.2≤d1/l≤0.4和0.2≤d2/l≤0.4,其中,l是所述主体在所述第二方向上的平均尺寸,d1是在所述第二方向上从所述第三表面的延长线到所述第一带电极的端部的平均尺寸,并且d2是在所述第二方向上从所述第四表面的延长线到所述第二带电极的端部的平均尺寸。

10.根据权利要求1所述的多层电子组件,其中,所述第一外电极包括第一连接部、第一拐角部和第三拐角部,所述第一连接部设置在所述第三表面上,所述第一拐角部设置为从所述第一连接部延伸到将所述第一表面和所述第三表面连接的拐角上,所述第三拐角部设置为从所述第一连接部延伸到将所述第二表面和所述第三表面连接的拐角上,

11.根据权利要求1所述的多层电子组件,其中,所述第一外电极包括第一连接部、第一带部和第三拐角部,所述第一连接部设置在所述第三表面上,所述第一带部设置为从所述第一连接部延伸到所述第一表面的一部分上,所述第三拐角部设置为从所述第一连接部延伸到将所述第二表面和所述第三表面连接的拐角上,

12.根据权利要求1所述的多层电子组件,其中,所述第二表面包括设置为彼此间隔开的第三带电极和第四带电极,并且

13.根据权利要求12所述的多层电子组件,其中,所述第一镀层还设置在所述第三带电极上,并且所述第二镀层还设置在所述第四带电极上。

14.根据权利要求1所述的多层电子组件,其中,所述多层电子组件在所述第二方向上的最大尺寸为1.1mm或更小,并且所述多层电子组件在所述第三方向上的最大尺寸为0.55mm或更小。

15.根据权利要求1所述的多层电子组件,其中,所述介电层具有0.35μm或更小的平均厚度。

16.根据权利要求1所述的多层电子组件,其中,所述第一内电极和所述第二内电极具有0.35μm或更小的平均厚度。

17.根据权利要求1所述的多层电子组件,其中,所述主体包括电容形成部和覆盖部,所述电容形成部包括交替设置的所述第一内电极和所述第二内电极且所述介电层介于所述第一内电极和所述第二内电极之间,所述覆盖部设置在所述电容形成部的在所述第一方向上的两个表面上,并且

18.根据权利要求1所述的多层电子组件,其中,所述主体包括连接所述第一表面和所述第三表面的1-3拐角、连接所述第一表面和所述第四表面的1-4拐角、连接所述第二表面和所述第三表面的2-3拐角以及连接所述第二表面和所述第四表面的2-4拐角,

19.根据权利要求1所述的多层电子组件,其中,所述第一外电极和所述第二外电极设置为与所述第五表面和所述第六表面间隔开。

20.根据权利要求1所述的多层电子组件,其中,所述第一外电极和所述第二外电极设置为与所述第一表面和所述第二表面间隔开。

21.根据权利要求1所述的多层电子组件,其中,所述第一外电极和所述第二外电极包括ni和ni合金中的至少一种。

22.根据权利要求1所述的多层电子组件,所述多层电子组件还包括:

23.一种多层电子组件,包括:

24.根据权利要求23所述的多层电子组件,其中,所述第一带电极与所述第三表面相接,并且所述第二带电极与所述第四表面相接。

25.根据权利要求23所述的多层电子组件,其中,所述第一带电极和所述第二带电极具有0.1μm或更大的平均厚度。

26.根据权利要求23所述的多层电子组件,其中,所述第一带电极和所述第二带电极与所述第一表面基本上共面。

27.根据权利要求23所述的多层电子组件,其中,所述第一带电极和所述第二带电极设置为嵌在所述第一表面中。

28.根据权利要求23所述的多层电子组件,其中,所述第一带电极和所述第二带电极包括ni、cr、pd和pt中的至少一种。

29.根据权利要求23所述的多层电子组件,其中,所述第一带电极和所述第二带电极包括batio3、tio2和sio2中的至少一种。

30.根据权利要求23所述的多层电子组件,其中,满足d1≥g1和d2≥g2,其中,d1是在所述第二方向上从所述第三表面的延长线到所述第一带电极的端部的平均尺寸,d2是在所述第二方向上从所述第四表面的延长线到所述第二带电极的端部的平均尺寸,g1是所述第三表面和所述第二内电极彼此间隔开的区域在所述第二方向上的平均尺寸,并且g2是所述第四表面和所述第一内电极彼此间隔开的区域在所述第二方向上的平均尺寸。

31.根据权利要求23所述的多层电子组件,其中,满足0.2≤d1/l≤0.4和0.2≤d2/l≤0.4,其中,l是所述主体在所述第二方向上的平均尺寸,d1是在所述第二方向上从所述第三表面的延长线到所述第一带电极的端部的平均尺寸,并且d2是在所述第二方向上从所述第四表面的延长线到所述第二带电极的端部的平均尺寸。

32.根据权利要求23所述的多层电子组件,其中,所述第一外电极包括第一连接部、第一拐角部和第三拐角部,所述第一连接部设置在所述第三表面上,所述第一拐角部设置为从所述第一连接部延伸到将所述第一表面和所述第三表面连接的拐角上,所述第三拐角部设置为从所述第一连接部延伸到将所述第二表面和所述第三表面连接的拐角上,

33.根据权利要求23所述的多层电子组件,其中,所述第一外电极包括第一连接部、第一带部和第三拐角部,所述第一连接部设置在所述第三表面上,所述第一带部设置为从所述第一连接部延伸到所述第一表面的一部分上,所述第三拐角部设置为从所述第一连接部延伸到将所述第二表面和所述第三表面连接的拐角上,

34.根据权利要求23所述的多层电子组件,其中,所述第二表面包括设置为彼此间隔开的第三带电极和第四带电极,并且

35.根据权利要求34所述的多层电子组件,其中,所述第一镀层还设置在所述第三带电极上,并且所述第二镀层还设置在所述第四带电极上。

36.根据权利要求23所述的多层电子组件,其中,所述多层电子组件在所述第二方向上的最大尺寸为1.1mm或更小,并且所述多层电子组件在所述第三方向上的最大尺寸为0.55mm或更小。

37.根据权利要求23所述的多层电子组件,其中,所述介电层具有0.35μm或更小的平均厚度。

38.根据权利要求23所述的多层电子组件,其中,所述第一内电极和所述第二内电极具有0.35μm或更小的平均厚度。

39.根据权利要求23所述的多层电子组件,其中,所述主体包括电容形成部和覆盖部,所述电容形成部包括交替设置的所述第一内电极和所述第二内电极且所述介电层介于所述第一内电极和所述第二内电极之间,所述覆盖部设置在所述电容形成部的在所述第一方向上的两个表面上,并且

40.根据权利要求23所述的多层电子组件,其中,所述主体包括连接所述第一表面和所述第三表面的1-3拐角、连接所述第一表面和所述第四表面的1-4拐角、连接所述第二表面和所述第三表面的2-3拐角以及连接所述第二表面和所述第四表面的2-4拐角,

41.根据权利要求23所述的多层电子组件,其中,满足h1≥h2,其中,h1是在所述第一方向上从所述第一表面到所述第一内电极和所述第二内电极中设置为最靠近所述第一表面的内电极的平均尺寸,h2是在所述第一方向上从所述第一表面的延长线到所述第一镀层和所述第二镀层的设置在所述第一外电极和所述第二外电极上的端部的平均尺寸。

42.根据权利要求23所述的多层电子组件,其中,满足h1<h2,其中,h1是在所述第一方向上从所述第一表面到所述第一内电极和所述第二内电极中设置为最靠近所述第一表面的内电极的平均尺寸,h2是在所述第一方向上从所述第一表面的延长线到所述第一镀层和所述第二镀层的设置在所述第一外电极和所述第二外电极上的端部的平均尺寸。

43.根据权利要求42所述的多层电子组件,其中,满足h2<t/2,其中,t是所述主体在所述第一方向上的平均尺寸。

44.根据权利要求23所述的多层电子组件,其中,所述第一镀层和所述第二镀层设置在与所述第一表面的延长线的水平面相同的水平面或比所述第一表面的延长线的水平面低的水平面上。

45.根据权利要求23所述的多层电子组件,所述多层电子组件还包括:

46.根据权利要求23所述的多层电子组件,其中,所述第一外电极和所述第二外电极包括ni和ni合金中的至少一种。

47.根据权利要求23所述的多层电子组件,其中,所述第一镀层和所述第二镀层的平均厚度比所述第一绝缘层和所述第二绝缘层的平均厚度薄。

48.根据权利要求23所述的多层电子组件,其中,所述第一外电极和所述第二外电极设置为与所述第五表面和所述第六表面间隔开。

49.根据权利要求23所述的多层电子组件,其中,所述第一外电极和所述第二外电极设置为与所述第一表面和所述第二表面间隔开。

50.根据权利要求23所述的多层电子组件,其中,所述第一镀层设置为覆盖所述第一绝缘层的设置在所述第一外电极上的端部,并且所述第二镀层设置为覆盖所述第二绝缘层的设置在所述第二外电极上的端部。

51.根据权利要求23所述的多层电子组件,其中,所述第一绝缘层设置为覆盖所述第一镀层的设置在所述第一外电极上的端部,并且所述第二绝缘层设置为覆盖所述第二镀层的设置在所述第二外电极上的端部。

52.根据权利要求23所述的多层电子组件,其中,所述第一绝缘层和所述第二绝缘层延伸到所述第五表面和所述第六表面并且彼此连接,并且设置为覆盖所述第五表面的一部分和所述第六表面的一部分。

53.根据权利要求23所述的多层电子组件,其中,所述第一绝缘层和所述第二绝缘层延伸到所述第五表面和所述第六表面并且彼此连接,并且设置为覆盖整个所述第五表面和整个所述第六表面。

54.根据权利要求23所述的多层电子组件,其中,所述第一绝缘层和所述第二绝缘层延伸到所述第二表面并且彼此连接。

技术总结本公开提供了一种多层电子组件。所述多层电子组件包括:主体,包括介电层以及第一内电极和第二内电极,所述第一内电极和所述第二内电极交替设置且所述介电层介于所述第一内电极和所述第二内电极之间,所述主体具有彼此相对的第一表面和第二表面、彼此相对的第三表面和第四表面、以及彼此相对的第五表面和第六表面,所述第一表面包括设置为彼此间隔开的第一带电极和第二带电极;第一外电极,设置在所述第三表面上并连接到所述第一内电极和所述第一带电极;第二外电极,设置在所述第四表面上并连接到所述第二内电极和所述第二带电极;第一镀层,设置在所述第一外电极和所述第一带电极上;以及第二镀层,设置在所述第二外电极和所述第二带电极上。

技术研发人员:李冈夏,成佑庆,任珍亨,具信一,李种晧

受保护的技术使用者:三星电机株式会社

技术研发日:技术公布日:2024/1/14