半导体封装的制作方法

本发明构思涉及半导体封装,更具体地涉及堆叠类型的半导体封装。

背景技术:

1、当今电子行业的趋势是以合理的价格制造轻量、紧凑、高速、多功能和高性能的产品。使用多芯片堆叠封装技术或系统级封装技术来满足这些趋势。有关多芯片堆叠封装或系统级封装,一个半导体封装可以执行多个单元半导体器件的功能。虽然多芯片堆叠封装或系统级封装可能比典型的单芯片封装稍厚,但它们具有与单芯片封装的平面尺寸相似的平面尺寸,因此主要用于高端、紧凑和便携式产品,例如移动电话、膝上型计算机、存储卡或便携式摄像机。

技术实现思路

1、本发明构思的一些实施例提供了一种具有提高的结构稳定性的半导体封装及其制造方法。

2、本发明构思的一些实施例提供了一种具有提高的热辐射效率的半导体封装及其制造方法。

3、本发明构思的一些实施例提供了一种具有提高的操作稳定性的半导体封装及其制造方法。

4、本发明构思的目的不限于上述目的,并且根据以下描述,本领域技术人员将清楚地理解上文未提及的其它目的。

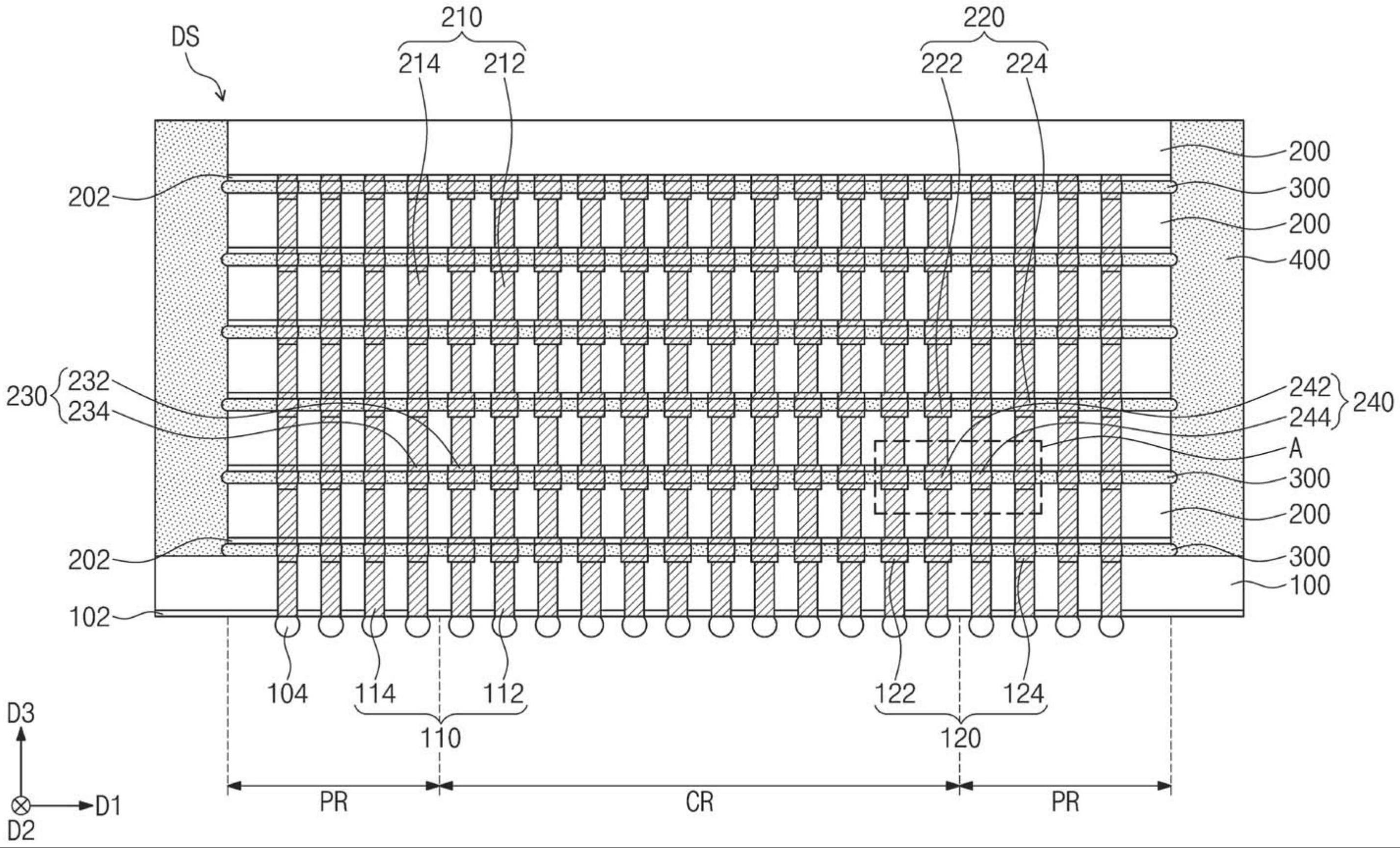

5、根据本发明构思的一些实施例,一种半导体封装包括:第一管芯,具有中心区和围绕所述中心区的外围区;多个贯通电极,穿透第一管芯;多个第一焊盘,在第一管芯的顶表面处,并耦接到贯通电极;第二管芯,在第一管芯上;多个第二焊盘,在第二管芯的底表面处,第二管芯的底表面面对第一管芯的顶表面;多个连接端子,将第一焊盘连接到第二焊盘;以及介电层,填充第一管芯和第二管芯之间的空间,并围绕连接端子。中心区上的每个第一焊盘的第一宽度可以大于外围区上的每个第一焊盘的第二宽度。每个连接端子可以包括在其侧表面处的凸部,该凸部突出超过相应的第一焊盘的侧表面和相应的第二焊盘的侧表面。凸部可以在远离第一管芯的中心的方向上突出。凸部的突出距离可以在从第一管芯的中心朝向第一管芯的外部的方向上增加。

6、根据本发明构思的一些实施例,一种半导体封装包括:第一管芯;多个第二管芯,堆叠在第一管芯上,每个第二管芯包括多个第一焊盘、多个第二焊盘、多个第三焊盘和多个第四焊盘,第一焊盘和第二焊盘在相应的第二管芯的顶表面上,并且第三焊盘和第四焊盘在相应的第二管芯的底表面上;针对每对相邻的第二管芯的多个第一连接端子,将该对相邻的第二管芯中的下第二管芯的第一焊盘连接到该对相邻的第二管芯中的上第二管芯的第三焊盘,第一焊盘和第三焊盘在该对相邻的第二管芯之间彼此竖直地重叠;针对每对相邻的第二管芯的多个第二连接端子,将该对相邻的第二管芯中的下第二管芯的第二焊盘连接到该对相邻的第二管芯中的上第二管芯的第四焊盘,第二焊盘和第四焊盘在该对相邻的第二管芯之间彼此竖直地重叠;针对每对相邻的第二管芯的介电层,填充该对相邻的第二管芯之间的空间;以及多个外部端子,在第一管芯下方,并将第一管芯连接到衬底。第一焊盘和第三焊盘可以在第二管芯的中心区中。第二焊盘和第四焊盘可以在第二管芯的外围区中,该外围区在中心区的外部。每个第一焊盘在第一水平方向上的最大宽度与第一焊盘在第一水平方向上的布置周期的第一比率可以大于每个第二焊盘在第一水平方向上的最大宽度与第二焊盘在第一水平方向上的布置周期的第二比率。

7、根据本发明构思的一些实施例,一种半导体封装包括:衬底;多个管芯,堆叠在衬底上,每个管芯包括在该管芯的顶表面上的多个第一焊盘和在该管芯的底表面上的多个第二焊盘;多个连接端子,将第一焊盘连接到第二焊盘;以及介电层,填充管芯之间的空间,并且围绕连接端子。管芯可以具有中心区和围绕中心区的外围区。中心区上的每个第一焊盘的第一面积可以大于外围区上的每个第一焊盘的第二面积。每个连接端子可以包括在该连接端子的第一侧上的凸部,并且在该连接端子的相对的第二侧上可以不包括凸部。该第一侧可以指向管芯的外部。

技术特征:

1.一种半导体封装,包括:

2.根据权利要求1所述的半导体封装,其中,所述中心区上的每个第一焊盘的第一宽度是所述外围区上的每个第一焊盘的第二宽度的约1.01倍至约1.5倍。

3.根据权利要求1所述的半导体封装,其中,所述中心区上的每个第一焊盘在第一方向上的所述第一宽度与所述中心区上的第一焊盘在所述第一方向上的布置周期的第一比率大于所述外围区上的每个第一焊盘在所述第一方向上的所述第二宽度与所述外围区上的第一焊盘在所述第一方向上的布置周期的第二比率。

4.根据权利要求1所述的半导体封装,其中,所述中心区上的每个第一焊盘的面积大于所述外围区上的每个第一焊盘的面积。

5.根据权利要求1所述的半导体封装,其中,

6.根据权利要求5所述的半导体封装,其中,所述凹部的凹入深度在从所述第一管芯的中心朝向所述第一管芯的外部的方向上增加。

7.根据权利要求1所述的半导体封装,还包括:

8.一种半导体封装,包括:

9.根据权利要求8所述的半导体封装,其中,每个第一焊盘在所述第一水平方向上的最大宽度和每个第三焊盘在所述第一水平方向上的最大宽度大于每个第二焊盘在所述第一水平方向上的最大宽度和每个第四焊盘在所述第一水平方向上的最大宽度中的每一个。

10.根据权利要求9所述的半导体封装,其中,每个第一焊盘在所述第一水平方向上的最大宽度和每个第三焊盘在所述第一水平方向上的最大宽度是每个第二焊盘在所述第一水平方向上的最大宽度和每个第四焊盘在所述第一水平方向上的最大宽度的约1.01倍至约1.5倍。

11.根据权利要求8所述的半导体封装,其中,所述第一焊盘的布置周期与所述第二焊盘的布置周期相同。

12.根据权利要求8所述的半导体封装,其中,所述第一比率是所述第二比率的约1.01倍至约1.5倍。

13.根据权利要求8所述的半导体封装,其中,

14.根据权利要求13所述的半导体封装,其中,

15.根据权利要求8所述的半导体封装,其中,

16.一种半导体封装,包括:

17.根据权利要求16所述的半导体封装,其中,所述中心区上的每个第一焊盘在第一方向上的最大宽度大于所述外围区上的每个第一焊盘在所述第一方向上的最大宽度。

18.根据权利要求17所述的半导体封装,其中,所述中心区上的每个第一焊盘在所述第一方向上的最大宽度是所述外围区上的每个第一焊盘在所述第一方向上的最大宽度的约1.01倍至约1.5倍。

19.根据权利要求16所述的半导体封装,其中,所述中心区上的每个第一焊盘在第一方向上的最大宽度与所述中心区上的第一焊盘在所述第一方向上的布置周期的第一比率大于所述外围区上的每个第一焊盘在所述第一方向上的最大宽度与所述外围区上的第一焊盘在所述第一方向上的布置周期的第二比率。

20.根据权利要求16所述的半导体封装,其中,所述凸部的突出距离在从所述管芯的中心朝向所述管芯的外部的方向上增加。

技术总结

公开了一种半导体封装,包括:第一管芯,具有中心区和围绕中心区的外围区;多个贯通电极,穿透第一管芯;多个第一焊盘,在第一管芯的顶表面处,并耦接到贯通电极;第二管芯,在第一管芯上;多个第二焊盘,在第二管芯的底表面处,第二管芯的底表面面对第一管芯的顶表面;多个连接端子,将第一焊盘连接到第二焊盘;以及介电层,填充第一管芯和第二管芯之间的空间,并围绕连接端子。中心区上的每个第一焊盘的第一宽度可以大于外围区上的每个第一焊盘的第二宽度。每个连接端子可以包括在其侧表面处的凸部,该凸部突出超过相应的第一焊盘的侧表面和相应的第二焊盘的侧表面。凸部可以在远离第一管芯的中心的方向上突出。凸部的突出距离可以在从第一管芯的中心朝向第一管芯的外部的方向上增加。

技术研发人员:金宣敎,姜芸炳,金珉秀,朴商植,郑胜允

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!