一种半导体器件的外延结构及其制备方法、半导体器件与流程

本发明实施例涉及半导体,尤其涉及一种半导体器件的外延结构及其制备方法、半导体器件。

背景技术:

1、半导体材料gan由于具有禁带宽度大、电子饱和漂移速度高、击穿场强高、导热性能好等特点,比si和gaas更适合于制备高温、高频、高压和大功率器件。

2、由于外延结构中缺少gan衬底,gan外延技术都生长在异质衬底上,gan与异质衬底之间存在晶格失配,导致gan材料存在较多的穿透位错,同时异质衬底会对gan产生应力,生长过程中衬底会产生形变,从而影响衬底表面温度的均匀性,导致gan生长的均匀性变差。

技术实现思路

1、有鉴于此,本发明实施例提供一种半导体器件的外延结构及其制备方法、半导体器件,通过设置插入结构能够控制外延层生长过程中产生的压应力,如此可以降低生长过程中衬底的翘曲,提高缓冲层厚度均匀性,进而提升外延结构的质量以及半导体器件的质量。

2、第一方面,本发明实施例提供了一种半导体器件的外延结构,包括:

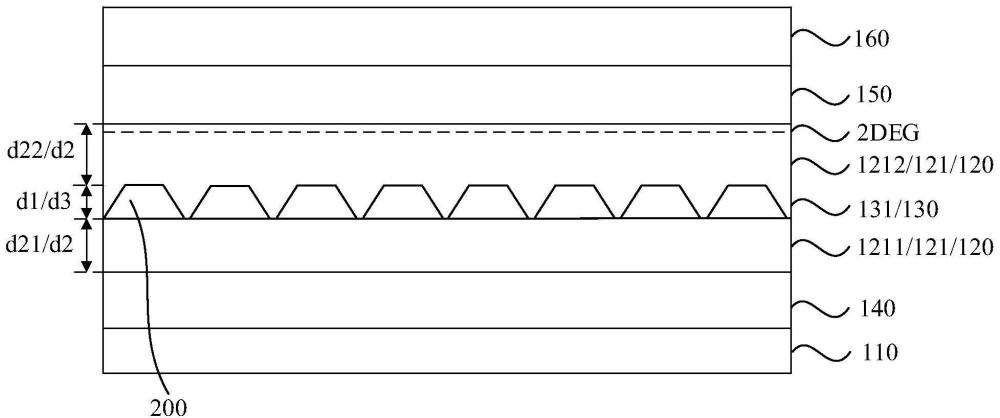

3、衬底、缓冲结构和插入结构;

4、所述缓冲结构包括至少两层缓冲层,所述插入结构包括至少一层插入层,所述缓冲层与所述插入层交替叠层设置,且任一所述插入层位于相邻两层所述缓冲层之间;

5、至少一层所述插入层包括多个岛状结构,位于所述岛状结构远离所述衬底一侧的所述缓冲层覆盖所述岛状结构。

6、可选的,所述插入结构包括多层所述插入层;

7、任一所述插入层中包括多个所述岛状结构。

8、可选的,多层所述插入层包括第一插入层和第二插入层,所述第一插入层包括多个第一岛状结构,所述第二插入层包括多个第二岛状结构;

9、沿所述外延结构的厚度方向,存在至少一个所述第一岛状结构与相邻两个所述第二岛状结构的间隙交叠。

10、可选的,所述插入层包括in原子。

11、可选的,所述插入层中所述in原子的原子数量占比a满足0<a≤50%。

12、可选的,所述插入层的厚度d1满足5nm≤d1≤50nm。

13、可选的,所述缓冲结构的厚度为d2,所述插入结构的厚度为d3;

14、其中,40≤d3/d2≤400。

15、可选的,所述外延结构还包括:

16、成核层,位于所述衬底与所述缓冲结构之间;

17、沟道层,位于所述缓冲结构远离所述衬底的一侧;

18、势垒层,位于所述沟道层远离所述衬底的一侧,所述势垒层与所述沟道层形成异质结结构;

19、帽层,位于所述势垒层远离所述衬底的一侧。

20、第二方面,本发明实施例还提供了一种半导体器件的外延结构的制备方法,包括:

21、提供衬底;

22、在所述衬底一侧制备缓冲结构和插入结构;所述缓冲结构包括至少两层缓冲层,所述插入结构包括至少一层插入层,所述缓冲层与所述插入层交替叠层设置,且任一所述插入层位于相邻两层所述缓冲层之间;至少一层所述插入层包括多个岛状结构,位于所述岛状结构远离所述衬底一侧的所述缓冲层覆盖所述岛状结构。

23、可选的,所述插入层包括in原子;

24、在所述衬底一侧制备缓冲结构和插入结构,包括:

25、在第一制备温度下,打开in源,制备插入层;

26、关闭in源,在第二制备温度下,保持预设时间后,制备缓冲层;所述第二制备温度大于所述第一制备温度。

27、可选的,所述缓冲结构包括多层所述缓冲层,所述插入结构包括多层所述插入层;

28、在所述衬底一侧制备缓冲结构和插入结构,包括:

29、在所述衬底一侧依次交替制备所述缓冲层和所述插入层。

30、可选的,制备缓冲结构之前,还包括:

31、制备成核层,所述成核层位于所述衬底与所述缓冲结构之间;

32、制备缓冲结构之后,还包括:

33、制备沟道层,所述沟道层位于所述缓冲结构远离所述衬底的一侧;

34、制备势垒层,所述势垒层位于所述沟道层远离所述衬底的一侧,所述势垒层与所述沟道层形成异质结结构;

35、制备帽层,所述帽层位于所述势垒层远离所述衬底的一侧。

36、第三方面,本发明实施例还提供了一种半导体器件,包括第一方面任一实施例所述的半导体器件的外延结构;

37、所述外延结构还包括位于所述衬底与所述缓冲结构之间的成核层;位于所述缓冲结构远离所述衬底一侧的沟道层;位于所述沟道层远离所述衬底一侧的势垒层,所述势垒层与所述沟道层形成异质结结构;位于所述势垒层远离所述衬底一侧的帽层;

38、所述半导体器件还包括:

39、位于所述势垒层远离所述衬底一侧的源极和漏极,以及位于所述帽层远离所述衬底一侧的栅极,所述栅极位于所述源极和所述漏极之间。

40、本发明实施例提供的半导体器件的外延结构包括衬底、缓冲结构和插入结构。通过在相邻两层缓冲层之间增设至少一层插入层,且缓冲层与插入层交替叠层设置,随着缓冲层生长厚度的增加,插入层中多个岛状结构会逐渐合并成完整的缓冲层,在合并的过程中产生的张应力,能够抵消外延层生长过程中产生的压应力,进而能够中和生长过程中衬底的翘曲,提高缓冲层厚度均匀性,可以提升外延结构的质量以及半导体器件的质量。

技术特征:

1.一种半导体器件的外延结构,其特征在于,包括衬底、缓冲结构和插入结构;

2.根据权利要求1所述的外延结构,其特征在于,所述插入结构包括多层所述插入层;

3.根据权利要求2所述的外延结构,其特征在于,多层所述插入层包括第一插入层和第二插入层,所述第一插入层包括多个第一岛状结构,所述第二插入层包括多个第二岛状结构;

4.根据权利要求1所述的外延结构,其特征在于,所述插入层包括in原子。

5.根据权利要求4所述的外延结构,其特征在于,所述插入层中所述in原子的原子数量占比a满足0<a≤50%。

6.根据权利要求1所述的外延结构,其特征在于,所述插入层的厚度d1满足5nm≤d1≤50nm。

7.根据权利要求1所述的外延结构,其特征在于,所述缓冲结构的厚度为d2,所述插入结构的厚度为d3;

8.根据权利要求1所述的外延结构,其特征在于,所述外延结构还包括:

9.一种半导体器件的外延结构的制备方法,其特征在于,包括:

10.根据权利要求9所述的制备方法,其特征在于,所述插入层包括in原子;

11.根据权利要求9所述的制备方法,其特征在于,所述缓冲结构包括多层所述缓冲层,所述插入结构包括多层所述插入层;

12.根据权利要求9所述的制备方法,其特征在于,制备缓冲结构之前,还包括:

13.一种半导体器件,其特征在于,包括权利要求1-8任一项所述的外延结构;

技术总结

本发明实施例提供了一种半导体器件的外延结构及其制备方法、半导体器件,所述外延结构包括衬底、缓冲结构和插入结构;所述缓冲结构包括至少两层缓冲层,所述插入结构包括至少一层插入层,所述缓冲层与所述插入层交替叠层设置,且任一所述插入层位于相邻两层所述缓冲层之间;至少一层所述插入层包括多个岛状结构,位于所述岛状结构远离所述衬底一侧的所述缓冲层覆盖所述岛状结构。采用上述技术方案,通过设置插入结构能够控制外延层生长过程中产生的压应力,如此可以降低生长过程中衬底的翘曲,提高缓冲层厚度的均匀性,进而提升外延结构的质量以及半导体器件的质量。

技术研发人员:孔苏苏,张晖

受保护的技术使用者:苏州能讯高能半导体有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!