一种N+源区内陷的沟槽型SiCMOSFET结构

一种n+源区内陷的沟槽型sic mosfet结构

技术领域

1.本发明涉及半导体领域,具体涉及一种n+源区内陷的沟槽型sic mosfet结构。

背景技术:

2.sic mosfet以其高压、高频、低损耗以及高温等优越性能,显著提高电力装置的效率和功率密度,是高功率电子领域的有力竞争者。目前已有多家半导体公司相继推出商用sic mosfet产品并得到广泛应用,在电动汽车、光伏逆变等领域逐渐开始替代si基电力电子器件。为进一步降低传统平面栅sic mosfet器件的导通电阻,部分厂商研发了沟槽型sic mosfet器件。通过减小器件元胞尺寸提高功率密度,显著提升了sic mosfet器件开关特性。研究功率半导体器件的可靠性,对提高电力电子系统的整体可靠性具有重要的意义。由于沟槽型sic mosfet消除了平面型sic mosfet的寄生jfet效应,从而大大降低了导通电阻,但由于其自身结构中的寄生三极管(bjt)效应,其短路耐受能力通常弱于平面型sic mosfet。

技术实现要素:

3.针对提高沟槽型sic mosfet短路耐受能力的需求,本发明提供了一种n+源区内陷的沟槽型sic mosfet结构。

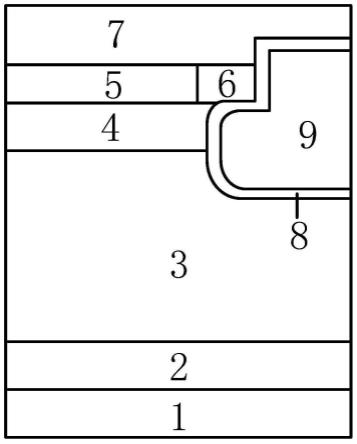

4.本发明解决上述技术问题所采用的技术方案是:一种n+源区内陷的沟槽型sic mosfet结构,其元胞结构包括金属漏极(1),位于金属漏极(1)上方的n+衬底(2)和n型漂移区(3),所述漂移区(3)中设有多晶硅栅极(9)及栅极氧化层(8)、金属源极(7)、p型基区(4),所述p型基区(4)上设有p+重掺杂区(5)和n+源区(6),其特征在于,所述n+源区(6)向栅极方向内陷。

5.本发明的技术方案相对常规沟槽型sic mosfet结构,将p基区上方的n+源区向栅极侧移动,一方面增加了沟道长度,从而降低器件的饱和电流。另一方面,传统沟槽型sic mosfet中寄生三极管的导通受n+源区下方p基区中的空穴电流影响,而本结构中n+源区下方p基区被栅极结构占据,p基区中的空穴电流直接从源极接触流走,从而实现了抑制寄生三极管导通,提高器件短路耐受能力的效果。

6.进一步地所述n+源区(6)的内陷深度为自身宽度的80%;典型宽度为0.3μm。

附图说明

7.图1为本发明的结构示意图;

8.图2为常规沟槽型sic mosfet结构示意图;

9.图3为常规沟槽型sic mosfet与本发明结构的短路电流仿真图。

具体实施方式

10.下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发

明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

11.本发明提出了一种n+源区内陷的沟槽型sic mosfet结构,其元胞结构包括金属漏极(1),位于金属漏极(1)上方的n+衬底(2)和n型漂移区(3),所述漂移区(3)中设有多晶硅栅极(9)及栅极氧化层(8)、金属源极(7)、p型基区(4),所述p型基区(4)上设有p+重掺杂区(5)和n+源区(6),其中n+源区(6)向栅极方向内陷。

12.本发明的方案相比于图2所示的常规沟槽型sic mosfet结构,将p基区上方的n+源区向栅极侧内陷移动,可以抑制器件寄生三极管的导通,同时降低器件饱和电流,提高器件的短路耐受能力。

13.在一次实施例中,对常规沟槽型sic mosfet与本发明的结构在短路过程中器件的漏极电流仿真测试。如图3所示与常规沟槽型sic mosfet相比本发明的结构器件短路耐受时间有明显提升。

14.综上所述,本发明公开了一种n+源区内陷的沟槽型sic mosfet结构,该结构在常规沟槽型sic mosfet结构的基础上,将p基区上方的n+源区向右移动,使得n+源区下方的p基区被栅极结构占据,抑制了器件的寄生三极管效应,同时增加了器件导通时的沟道长度,从而降低饱和电流,实现了在不影响器件基本特性的条件下,提高器件短路耐受能力的效果。

技术特征:

1.一种n+源区内陷的沟槽型sic mosfet结构,其元胞结构包括金属漏极(1),位于金属漏极(1)上方的n+衬底(2)和n型漂移区(3),所述漂移区(3)中设有多晶硅栅极(9)及栅极氧化层(8)、金属源极(7)、p型基区(4),所述p型基区(4)上设有p+重掺杂区(5)和n+源区(6),其特征在于,所述n+源区(6)向栅极方向内陷。2.根据权利要求1所述的n+源区内陷的沟槽型sic mosfet结构,其特征在于n+源区(6)内陷深度为自身宽度的80%。3.根据权利要求1所述的n+源区内陷的沟槽型sic mosfet结构,其特征在于,n+源区(6)的典型宽度为0.3μm。

技术总结

本发明公开了一种N+源区内陷的沟槽型SiC MOSFET结构,该结构在常规沟槽型SiC MOSFET结构的基础上,将P基区上方的N+源区向右移动,使得N+源区下方的P基区被栅极结构占据,抑制了器件的寄生三极管效应,同时增加了器件导通时的沟道长度,从而降低饱和电流,实现了在不影响器件基本特性的条件下,提高器件短路耐受能力的效果。力的效果。力的效果。

技术研发人员:伍伟 高崇兵 喻明康

受保护的技术使用者:电子科技大学

技术研发日:2022.11.21

技术公布日:2023/3/6

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1