通孔制造方法与流程

本公开一般涉及电子器件及其制造方法,更具体地,涉及通孔及其制造方法。

背景技术:

1、通孔,特别是导电通孔的制造是存在于大多数电子器件制造方法中的元素。

2、电子器件具有越来越小的尺寸。这就需要更小的通孔,从而需要更准确的制造方法。

3、在本领域中需要已知通孔制造方法的全部或部分缺点。

技术实现思路

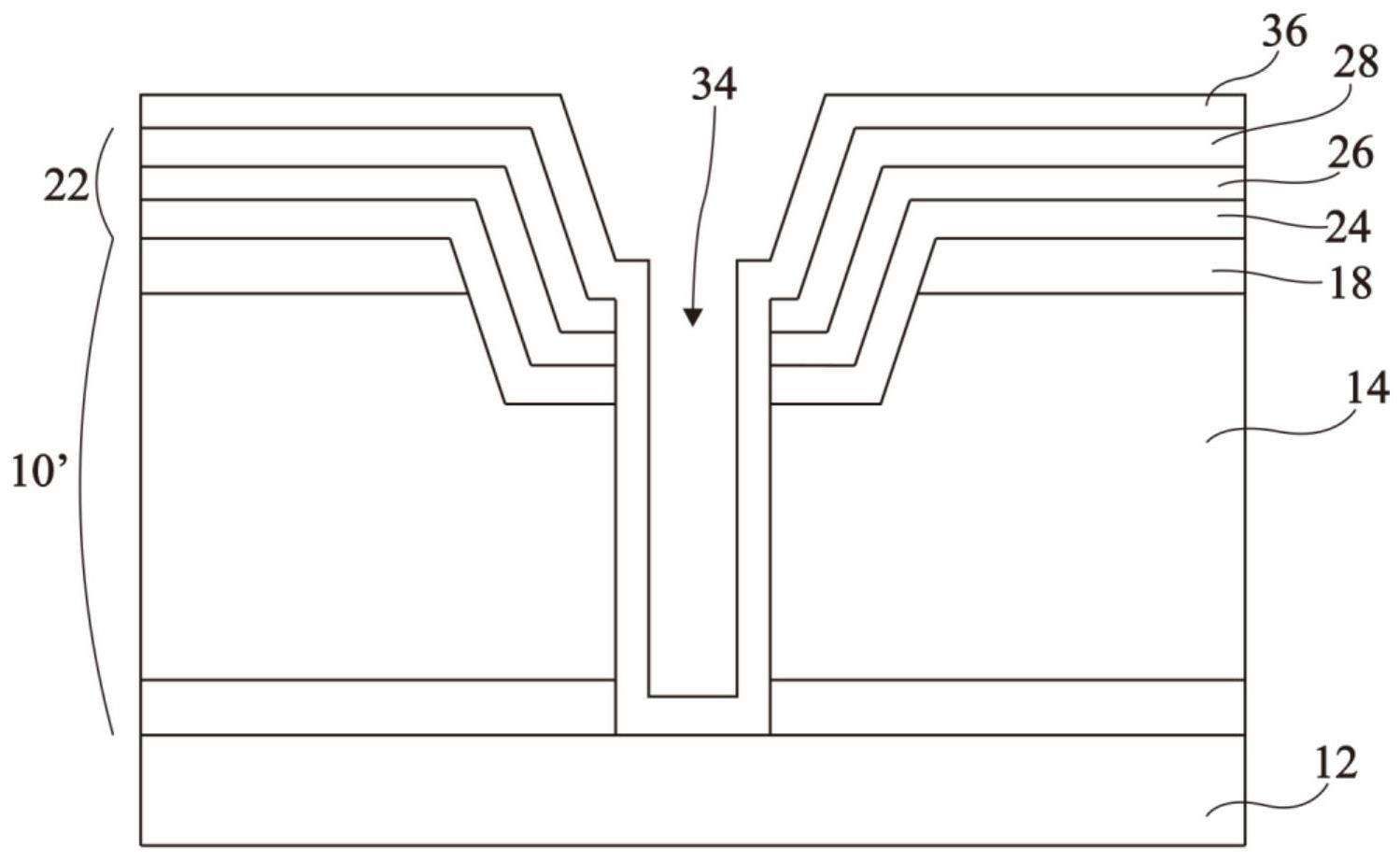

1、在一个实施例中,提出了一种用于制造穿过层的第一堆叠到达第一层的绝缘导电通孔的方法。第一堆叠至少包括第二导电或半导体层。该方法包括:a)在所述第一堆叠中形成第一腔体,所述第一腔体部分地穿过所述第二层;b)形成第二堆叠,所述第二堆叠包括在所述第一堆叠的上表面上以及在所述第一腔体的壁和底部上覆盖有第四绝缘层的第三蚀刻停止层;c)蚀刻穿过所述第一和第二堆叠的第二腔体,所述第二腔体在所述第一腔体的底部和所述第一层之间延伸;d)形成覆盖所述第二堆叠以及所述第二腔体的壁和底部的第五绝缘层;e)各向异性蚀刻所述第五层以在所述第二腔体的壁上形成所述通孔的绝缘护套,所述蚀刻是选择性地在所述第三层的材料上蚀刻所述第五层的材料;以及f)用导电材料填充第二腔体以形成通孔的导电芯。

2、根据一个实施例,步骤f)还包括用导电材料填充第一腔体。

3、根据实施例,第一层由导电材料或半导体材料制成。

4、根据一个实施例,步骤c)包括光刻。

5、根据实施例,第四层的材料和第五层的材料在第一层的材料上能够被选择性地蚀刻。

6、根据一个实施例,第四层和第五层由氧化硅制成,第二层由硅制成。

7、根据实施例,该方法在步骤e)和f)之间包括去除第三层的步骤。

8、根据实施例,第三层由在第一层的材料上能够选择性蚀刻的材料制成。

9、根据一个实施例,第三层由非晶碳制成。

10、根据实施例,第一堆叠具有大于或等于6μm的厚度。

11、根据实施例,第一堆叠包括在第一层和第二层之间的由绝缘材料制成的至少一个第六层。

12、根据一个实施例,第二堆叠包括在第三层和第一堆叠之间的由绝缘材料制成的第七层。

13、根据一实施例,第三层的材料在第七层上能够被选择性地蚀刻。

14、根据一个实施例,第一堆叠包括位于第二层和第二堆叠之间的至少一个第八层。

技术特征:

1.一种制造方法,包括:

2.根据权利要求1所述的方法,其中步骤f)还包括用导电材料填充所述第一腔体。

3.根据权利要求1所述的方法,其中所述第一层由导电材料或半导体材料制成。

4.根据权利要求1所述的方法,其中步骤c)包括在蚀刻之前以光刻方式限定所述第二腔体的位置。

5.根据权利要求1所述的方法,其中所述第一绝缘层的材料和所述第二绝缘层的材料在所述第一层的材料之上能够被选择性地蚀刻。

6.根据权利要求1所述的方法,其中所述第一绝缘层和所述第二绝缘层由氧化硅制成,并且其中所述至少一个导电或半导体层由硅制成。

7.根据权利要求1所述的方法,在步骤e)和步骤f)之间还包括去除所述蚀刻停止层。

8.根据权利要求1所述的方法,其中所述蚀刻停止层由在所述第一层的材料之上能够被选择性蚀刻的材料制成。

9.根据权利要求1所述的方法,其中所述蚀刻停止层由非晶碳制成。

10.根据权利要求1所述的方法,其中所述层的第一堆叠具有大于或等于6μm的厚度。

11.根据权利要求1所述的方法,其中所述层的第一堆叠包括在所述第一层与所述至少一个导电或半导体层之间的至少一个绝缘层。

12.根据权利要求1所述的方法,其中所述第二堆叠包括位于所述蚀刻停止层与所述第一堆叠之间的另一绝缘层。

13.根据权利要求12所述的方法,其中所述蚀刻停止层的材料在所述另一绝缘层之上能够被选择性地蚀刻。

14.根据权利要求1所述的方法,其中所述层的第一堆叠包括至少一个层,所述至少一个层由绝缘材料制成、或者由导电或半导体材料制成,所述至少一个层位于所述至少一个导电或半导体层与所述层的第二堆叠之间。

15.一种制造绝缘导电通孔的方法,包括:

16.根据权利要求15所述的方法,进一步包括在各向异性蚀刻之后、并且在填充所述第二腔体之前,移除所述层的第二堆叠的所述蚀刻停止层。

17.根据权利要求15所述的方法,其中所述蚀刻停止层由在所述基底导电或半导体层之上能够被选择性蚀刻的材料制成。

18.根据权利要求15所述的方法,其中所述蚀刻停止层由非晶碳制成。

技术总结

本公开的实施例涉及通孔制造方法。提出了一种用于制造绝缘导电通孔的方法。该通孔穿过层的第一堆叠到达第一层。形成部分延伸到层的第一堆叠中的第一腔体。在层的第一堆叠之上和第一腔体中形成层的第二堆叠。层的第二堆叠包括蚀刻停止层和绝缘层。然后形成完全延伸穿过第一层的堆叠和第二层的堆叠到达第一层的第二腔体。然后,绝缘衬套覆盖第二腔体的壁和底部。然后各向异性地蚀刻绝缘衬套,并且用形成通孔的芯的导电材料填充第二腔体。

技术研发人员:M·巴拉斯,P·古劳德

受保护的技术使用者:意法半导体(克洛尔2)公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!