新型SiCMOSFET器件及其制造方法与流程

本发明涉及半导体功率器件,特别涉及一种sic mosfet器件及其制造方法。

背景技术:

1、第三代半导体材料碳化硅(sic)有着宽禁带、高热导率、高载流子饱和迁移率以及临界击穿电场高等优越性能,使其在高功率、高频率、高电压等领域有着独特优势及广泛前景。目前sic mosfet已在汽车电子、光伏及储能等方面取得了广泛地应用。

2、传统的sic mosfet在性能上存在一个较大的问题,就是其击穿电压与导通电阻之间存在相互制约的关系,不能够同时实现提高击穿电压和降低导通电阻。目前,传统的sicmosfet为突破硅限,会引入超结结构(super junction),以有效降低导通电阻,使sicmosfet得到进一步的广泛应用。但随着研究的不断深入,sic mosfet的各种技术已经很成熟,硅基底功率器件的各项性能已十分接近极限。虽然将超结结构应用于sic mosfet能突破其击穿电压与导通电阻之间的制约关系,但是实现超结结构由于需形成交替的p柱区和n柱区来保持电荷平衡,因此其制备工艺较为复杂且困难,制备得到的sic mosfet的比导通电阻值(ron.sp)较大,生产成本较高。

3、因此,本发明的主要目的在于提供一种sic mosfet器件及其制造方法,以解决上述问题。

4、需要说明的是,公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明针对现有技术的问题,提供一种新型sic mosfet器件及其制造方法,通过在两个p型基区间注入离子形成n+区,使n+区与p型基区保持电荷平衡,形成高压超结结构,这样不仅不会增加制造工艺上的难度,还能保持需求的耐压水平,最终相较于传统sicmosfet能够有效的降低比导通电阻值(ron.sp),进而大幅度缩小芯片面积,降低生产成本。

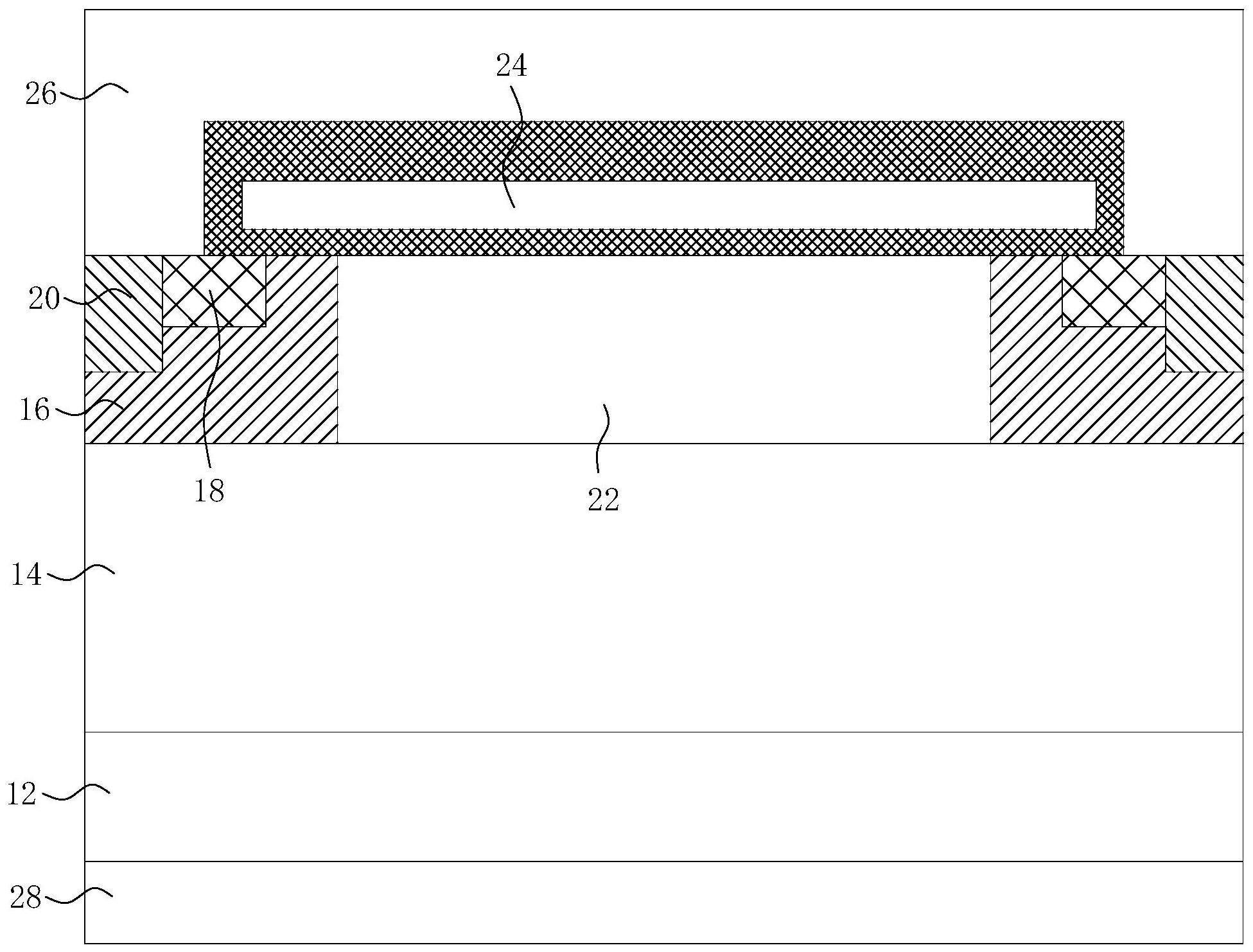

2、本发明的一实施例提供一种新型sic mosfet器件的制造方法,其包括下列步骤:提供一n+衬底,n+衬底具有相对的正面和背面;在n+衬底的正面生长n型漂移区;在n型漂移区上设置至少二个彼此独立的p型基区;在p型基区上设置n+源区;在p型基区上设置p+欧姆接触区,p+欧姆接触区连接n+源区;在二个p型基区之间设置超结n层。

3、在一些实施例中,在设置完超结n层之后还可以包括下列步骤:在超结n层、p型基区和n+源区上设置栅极;在栅极和p+欧姆接触区上设置源极;在n+衬底的背面设置漏极。

4、在一些实施例中,超结n层是采用离子注入的方式所形成。优选地,注入的离子是氮离子。

5、在一些实施例中,超结n层中的离子注入深度范围为1~1.5μm。

6、在一些实施例中,n型漂移区的厚度范围为10~12μm。

7、本发明的一实施例还提供一种新型sic mosfet器件,其包括n+衬底、n型漂移区、至少二个p型基区、n+源区、p+欧姆接触区和超结n层。n+衬底具有相对的正面和背面;n型漂移区设置在n+衬底的正面;至少二个p型基区设置在n型漂移区上,各p型基区彼此独立;n+源区设置在p型基区上;p+欧姆接触区设置在p型基区上且连接n+源区;超结n层设置在二个p型基区之间。

8、在一些实施例中,新型sic mosfet器件还包括栅极、源极和漏极,栅极设置在超结n层、p型基区和n+源区上,源极设置在栅极和p+欧姆接触区上,漏极设置在n+衬底的背面。

9、本发明一实施例提供的一种新型sic mosfet器件及其制造方法,通过在二个p型基区间注入离子形成n+区,使n+区与p型基区保持电荷平衡,形成高压超结结构,这样不仅不会增加制造工艺上的难度,还能保持需求的耐压水平,最终相较于传统sic mosfet能够有效的降低比导通电阻值(ron.sp),进而大幅度缩小芯片面积,降低生产成本。

10、本发明的其它特征和有益效果将在随后的说明书中阐述,并且,部分地特征和有益效果可以从说明书中显而易见地的得出,或者是通过实施本发明而了解。本发明的目的和其他有益效果可通过在说明书等内容中所特别指出的结构来实现和获得。

技术特征:

1.一种新型sic mosfet器件的制造方法,其特征在于:所述新型sic mosfet器件的制造方法包括下列步骤:

2.根据权利要求1所述的新型sic mosfet器件的制造方法,其特征在于:在设置完所述超结n层之后还可以包括下列步骤:

3.根据权利要求1所述的新型sic mosfet器件的制造方法,其特征在于:所述超结n层是采用离子注入的方式所形成。

4.根据权利要求3所述的新型sic mosfet器件的制造方法,其特征在于:注入的离子是氮离子。

5.根据权利要求1所述的新型sic mosfet器件的制造方法,其特征在于:所述超结n层中的离子注入深度范围为1~1.5μm。

6.根据权利要求1所述的新型sic mosfet器件的制造方法,其特征在于:所述n型漂移区的厚度范围为10~12μm。

7.一种新型sic mosfet器件,其特征在于:所述新型sic mosfet器件包括:

8.根据权利要求7所述的新型sic mosfet器件,其特征在于:所述新型sic mosfet器件还包括栅极、源极和漏极,所述栅极设置在所述超结n层、所述p型基区和所述n+源区上,所述源极设置在所述栅极和所述p+欧姆接触区上,所述漏极设置在所述n+衬底的背面。

9.根据权利要求7所述的新型sic mosfet器件,其特征在于:所述超结n层是采用离子注入的方式所形成。

10.根据权利要求9所述的新型sic mosfet器件,其特征在于:注入的离子是氮离子。

技术总结

本发明涉及半导体功率器件技术领域,本发明提供一种新型SiC MOSFET器件的制造方法,其包括下列步骤:提供一N+衬底,N+衬底具有相对的正面和背面;在N+衬底的正面生长N型漂移区;在N型漂移区上设置至少二个彼此独立的P型基区;在P型基区上设置N+源区;在P型基区上设置P+欧姆接触区,P+欧姆接触区连接N+源区;在二个P型基区之间设置超结N层。借此,能够在不增加制造工艺难度的基础上,有效的降低新型SiC MOSFET器件的比导通电阻值(Ron.sp),进而大幅度缩小芯片面积,降低生产成本。

技术研发人员:徐守一,涂国华,蔡铭进

受保护的技术使用者:厦门芯达茂微电子有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!