一种高压芯片的封装结构的制作方法

1.本实用新型涉及半导体封装技术领域,尤其涉及一种高压芯片的封装结构。

背景技术:

2.半导体封装是指将通过测试的晶圆按照产品型号及功能需求加工得到独立芯片的过程。封装过程为:来自晶圆前道工艺的晶圆通过划片工艺后被切割为小的晶片(die),然后将切割好的晶片用胶水贴装到相应的基板架(引线框架)的小岛上,再利用超细的金属(金、锡、铜、铝等)导线或者导电性树脂将晶片的接合焊盘(bond pad)连接到基板的相应引脚(lead),并构成所要求的电路;然后再对独立的晶片用塑料外壳加以封装保护,塑封之后还要进行一系列操作,封装完成后进行成品测试,通常经过入检incoming、测试test和包装packing等工序,最后入库出货。

3.现有技术中,高压芯片的结构比较特殊,如图1所示,图1为现有技术中的高压芯片的结构示意图,高压芯片的有源面四周的边沿处和背面四周的边沿处均设有一圈凹陷区域,将其结构设计成这种形状,是为了使芯片能够耐高压。

4.在将芯片背面粘贴到与引脚连接的第一铜垫片上时,通常芯片都是通过采用点胶的方式贴装到第一铜垫片上,但是这种方式胶水很容易从芯片的四周溢出,并到达芯片背面四周的凹陷环形区域,甚至在胶水过量的时候,或者贴装压力过大时,很容易将胶水挤出,并接触到芯片的侧壁以及有源面上,如图2和图3所示,图2为少剂量胶水溢出的结构示意图,图3为多剂量胶水溢出的结构示意图,当胶水接触到芯片的侧壁以及有源面上时,容易导致芯片的有源面或侧壁与背面导通,容易导致芯片漏电的现象发生,从而导致芯片失效。

技术实现要素:

5.本实用新型提供了一种避免导致高压芯片漏电导致失效的高压芯片的封装结构。

6.本实用新型所采取的技术方案如下:

7.所述一种高压芯片的封装结构,包括高压芯片,与所述高压芯片的背面连接的第一铜垫,与第一铜垫连接的第一外引脚,与所述高压芯片的有源面连接的第二外引脚,所述高压芯片与所述第一铜垫之间设有铜薄膜层,所述高压芯片通过所述铜薄膜层与所述第一铜垫连接;设置一包封体,所述高压芯片、第一铜垫、第一外引脚、第二外引脚、铜薄膜层均设置于一包封体内,且所述第一外引脚与所述第二外引脚裸露在所述包封体外表面。

8.进一步的,所述铜薄膜层是通过电镀的方式电镀到所述高压芯片的背面。

9.进一步的,所述高压芯片的有源面与第二外引脚之间通过金属线连接。

10.进一步的,所述高压芯片的有源面上设有重布线层,所述高压芯片与第二外引脚之间通过所述重布线层连接。

11.进一步的,所述第二外引脚与重布线层之间通过设置金属通道连接。

12.进一步的,所述包封体上的第二外引脚与重布线层之间通过激光通孔的方式形成

通道,在所述通道的内壁上通过电镀的方式形成所述金属通道。

13.进一步的,所述金属通道与所述第二外引脚之间设有第二铜垫,所述金属通道通过所述第二铜垫与所述第二外引脚连接。

14.本实用新型与现有技术相比较,本实用新型的有益效果如下:通过将高压芯片的背面连接的第一铜垫,与第一铜垫连接的第一外引脚,与高压芯片的有源面连接的第二外引脚,将高压芯片与第一铜垫之间设置铜薄膜层,高压芯片通过铜薄膜层与第一铜垫连接,能够有效避免芯片漏电的现象发生,安全可靠,提高芯片封装体的质量和可靠性,高压芯片通过铜薄膜层压合到第一铜垫上,不会使铜薄膜层被挤压到芯片的侧壁以及有源面上,有效避免芯片的有源面或侧壁与背面导通,从而避免了芯片漏电的现象发生。

附图说明

15.图1为现有技术中一种高压芯片的结构示意图;

16.图2为现有技术中少剂量胶水溢出的结构示意图;

17.图3为现有技术中多剂量胶水溢出的结构示意图;

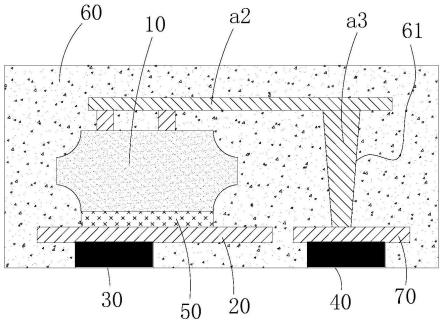

18.图4为本实用新型一种高压芯片的一实施例的封装结构示意图;

19.图5为本实用新型一种高压芯片的另一实施例的封装结构示意图。

具体实施方式

20.下面将结合具体的实施方式来说明本实用新型的内容,所述实施方式的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的组件或具有相同或类似功能的组件。

21.本实用新型所提到的方向用语,例如:上、下、左、右、前、后、内、外、正面、背面、侧面等,仅是参考附图的方向,以下通过参考附图描述的实施方式及使用的方向用语是示例性的,仅用于解释本实用新型,而不能理解为对本实用新型的限制。此外,本实用新型提供的各种特定的工艺和材料的例子,都是本领域普通技术人员可以意识到其他工艺的应用和/或其他材料的使用。

22.请参阅图4为本实用新型一种高压芯片的一实施例的封装结构示意图。

23.一种高压芯片的封装结构,包括高压芯片10,与高压芯片10的背面连接的第一铜垫20,与第一铜垫20连接的第一外引脚30,与高压芯片10的有源面连接的第二外引脚40,高压芯片10与第一铜垫20之间设有铜薄膜层50,铜薄膜层50是通过电镀的方式电镀到高压芯片10的背面。

24.高压芯片10通过铜薄膜层50与第一铜垫20连接;设置一包封体60,高压芯片10、第一铜垫20、第一外引脚30、第二外引脚40、铜薄膜层50均设置于一包封体60内,且第一外引脚30与第二外引脚40裸露在包封体60外表面。

25.在本实施例中,高压芯片10的有源面上设有重布线层a2,高压芯片10与第二外引脚40之间通过重布线层a2连接。在其他实施例中,高压芯片10的有源面与第二外引脚40之间通过设置金属线a1连接,如图5,图5为本实用新型一种高压芯片的另一实施例的封装结构示意图。

26.在本实施例中,第二外引脚40与重布线层a2之间通过设置金属通道a3连接,包封

体60上的第二外引脚40与重布线层a2之间通过激光通孔的方式形成通道61,在通道61的内壁上通过电镀的方式形成金属通道a3,金属通道a3与第二外引脚40之间设有第二铜垫70,金属通道a3通过第二铜垫70与第二外引脚40连接。

27.通过将高压芯片10的背面连接的第一铜垫20,与第一铜垫20连接的第一外引脚30,与高压芯片10的有源面连接的第二外引脚40,将高压芯片10与第一铜垫20之间设置铜薄膜层50,高压芯片10通过铜薄膜层50与第一铜垫20连接,能够有效避免芯片漏电的现象发生,安全可靠,提高芯片封装体的质量和可靠性,高压芯片10通过铜薄膜层50压合到第一铜垫20上,不会使铜薄膜层50被挤压到芯片的侧壁以及有源面上,有效避免芯片的有源面或侧壁与背面导通,从而避免了芯片漏电的现象发生。

28.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

技术特征:

1.一种高压芯片的封装结构,其特征在于,包括高压芯片(10),与所述高压芯片(10)的背面连接的第一铜垫(20),与第一铜垫(20)连接的第一外引脚(30),与所述高压芯片(10)的有源面连接的第二外引脚(40),所述高压芯片(10)与所述第一铜垫(20)之间设有铜薄膜层(50),所述高压芯片(10)通过所述铜薄膜层(50)与所述第一铜垫(20)连接;设置一包封体(60),所述高压芯片(10)、第一铜垫(20)、第一外引脚(30)、第二外引脚(40)、铜薄膜层(50)均设置于一包封体(60)内,且所述第一外引脚(30)与所述第二外引脚(40)裸露在所述包封体(60)外表面。2.根据权利要求1所述的一种高压芯片的封装结构,其特征在于,所述铜薄膜层(50)是通过电镀的方式电镀到所述高压芯片(10)的背面。3.根据权利要求1所述的一种高压芯片的封装结构,其特征在于,所述高压芯片(10)的有源面与第二外引脚(40)之间通过金属线(a1)连接。4.根据权利要求1所述的一种高压芯片的封装结构,其特征在于,所述高压芯片(10)的有源面上设有重布线层(a2),所述高压芯片(10)与第二外引脚(40)之间通过所述重布线层(a2)连接。5.根据权利要求4所述的一种高压芯片的封装结构,其特征在于,所述第二外引脚(40)与重布线层(a2)之间通过设置金属通道(a3)连接。6.根据权利要求5所述的一种高压芯片的封装结构,其特征在于,所述包封体(60)上的第二外引脚(40)与重布线层(a2)之间通过激光通孔的方式形成通道(61),在所述通道(61)的内壁上通过电镀的方式形成所述金属通道(a3)。7.根据权利要求6所述的一种高压芯片的封装结构,其特征在于,所述金属通道(a3)与所述第二外引脚(40)之间设有第二铜垫(70),所述金属通道(a3)通过所述第二铜垫(70)与所述第二外引脚(40)连接。

技术总结

本实用新型提供的一种高压芯片的封装结构,包括高压芯片,与所述高压芯片的背面连接的第一铜垫,与第一铜垫连接的第一外引脚,与所述高压芯片的有源面连接的第二外引脚,所述高压芯片与所述第一铜垫之间设有铜薄膜层,所述高压芯片通过所述铜薄膜层与所述第一铜垫连接;设置一包封体,所述高压芯片、第一铜垫、第一外引脚、第二外引脚、铜薄膜层均设置于一包封体内,且所述第一外引脚与所述第二外引脚裸露在所述包封体外表面。裸露在所述包封体外表面。裸露在所述包封体外表面。

技术研发人员:张光耀 谭小春

受保护的技术使用者:合肥矽迈微电子科技有限公司

技术研发日:2022.03.09

技术公布日:2022/7/4

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1