一种半导体封装结构的制作方法

本申请的实施例涉及一种半导体封装结构。

背景技术:

1、随着对半导体封装件的功能以及性能需求的提高,扇出芯片(fo die) 中芯片的整合程度越来越大,承载的重布线层(rdl)的层数也越来越多。而rdl层数越多,以及芯片的密集度越高,在芯片与芯片交界处的应力将会越大。如图1a所示的扇出型基板上芯片(focos)10,专用集成电路 (asic)20与高带宽存储器(hbm)30主要通过位于asic 20和hbm30 之间的芯片间隙(die gap)40下方的rdl 50中的重布线层迹线(rdl trace) 52进行信号沟通。由于hbm 30为复合3d封装元件,结构复杂并且内含大量高分子材料,因此在受热升温时,该元件较易受到热影响产生较大的膨胀量,并产生变形翘曲(如图1b所示),使得位于芯片间隙40下方的重布线层迹线52容易受损。

2、另外,芯片间的应力也导致底胶/底部填充物(under-fill)无法承受变形而破裂。多芯片模块(mcm)中模块芯片系统的复杂化,应力累积问题较为严重,也是导致底胶破裂的原因。而目前依照工程实验方向可以找到的底胶,无一可以有效解决底胶破裂的问题。因此半导体封装件的底胶破裂问题无法有效解决,其良率也处于较低水平(小于20%)。hbm 30所面向asic 20的角部(corner)32处集中有最大的应力应变,导致该处底部填充物(underfill)60具有分层(delamination)以及破裂(crack)的问题,如图1c-图1d所示(图1d为图1c中角部32处的局部放大图)。并且在实际应用中,温度越高,hbm 30的变形膨胀越严重,在角部32处产生的分层以及破裂越严重。而底部填充物60由于热膨胀系数(cte)较低,无法保持和hbm 30一致的变形,因此无法有效的平衡翘曲问题。并且目前hbm 30的内部材料无法更换成非高分子材料来改善上述问题。

3、rdl 50的层数较多,并且材质较软,无法有效承受多芯片模块造成的应力集中。角部32处由于应力应变集中发生分层及破裂后,会继续往rdl 50方向扩张导致芯片间隙40下方的rdl迹线52断线。rdl 50的层数无法降低,应力应变集中的问题无法缓解,因此由应力应变集中产生的翘曲 (warpage)也难以控制。

4、目前通常通过增大asic 20与hbm 30之间的距离(例如将二者之间的距离增加至200μm)来缓解底部填充物60的应力问题,但是间隔距离的增加又会降低二者之间信号的传输速度。并且当focos 10的横向尺寸超过例如830mm2以上时,即使增大asic 20与hbm 30之间的距离也难以解决底部填充物60容易断裂的问题。

技术实现思路

1、针对相关技术中存在的问题,本申请的目的在于提供一种半导体封装结构,以至少解决第一导线结构中迹线的损坏问题。

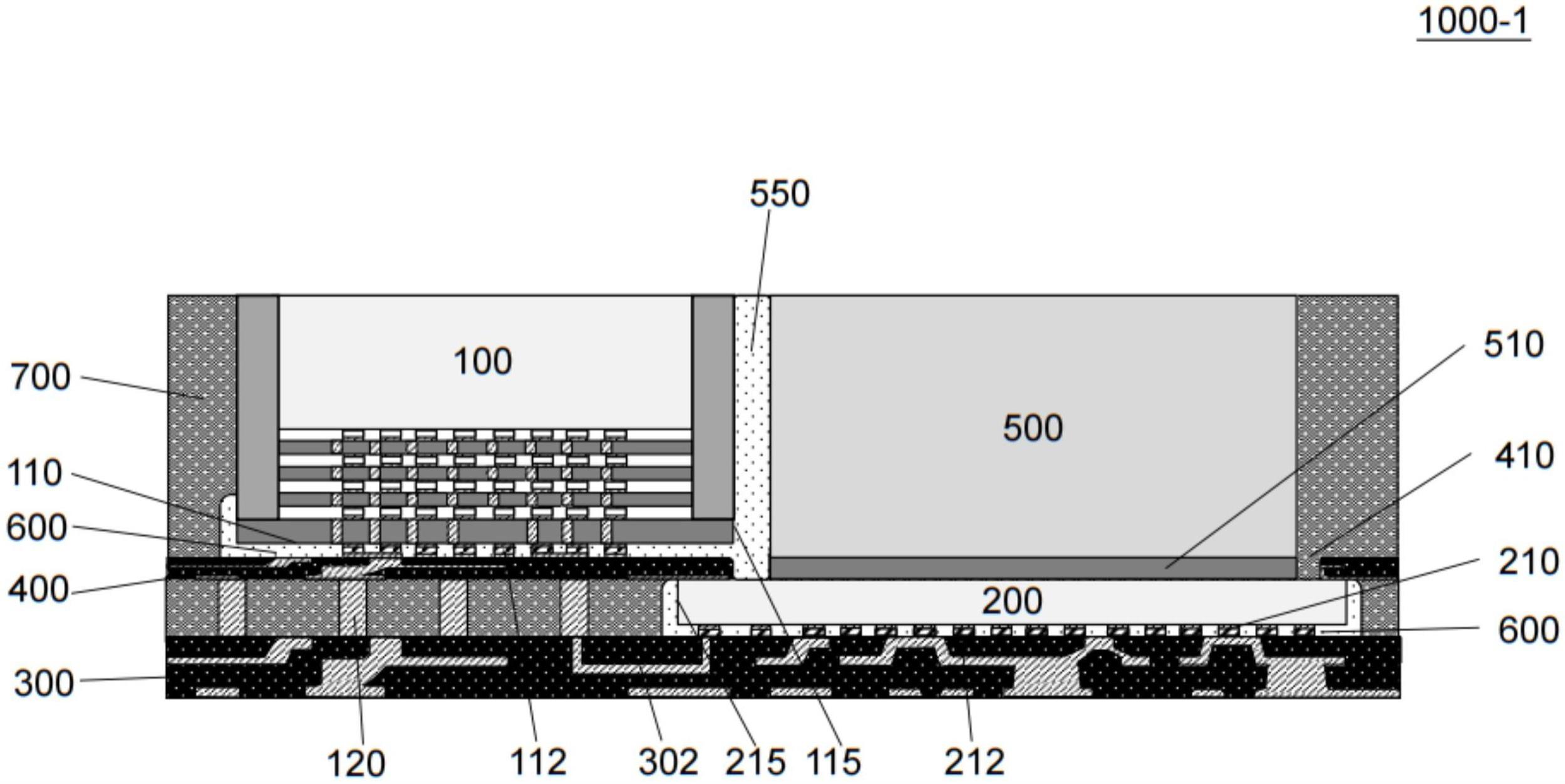

2、为实现上述目的,本申请提供了一种半导体封装结构,包括第一导线结构、第一电子元件和第二电子元件;其中,第一电子元件位于第一导线结构上,第一电子元件的第一有源面面向第一导线结构;第二电子元件位于第一导线结构上并且与第一电子元件隔开,第二电子元件的第二有源面面向第一导线结构;第一导线结构包括位于第一有源面和第二有源面下方的迹线,迹线电连接第一电子元件和第二电子元件,迹线在纵向上的全部的投影位于第一有源面的边缘内。

3、在一些实施例中,还包括散热元件,散热元件位于第二电子元件上,并且位于第一电子元件在水平方向上的一侧。

4、在一些实施例中,还包括底部填充层,底部填充层包封第二电子元件。

5、在一些实施例中,底部填充层还包封第一电子元件的至少一部分,底部填充层填充第一电子元件与散热元件之间的空间。

6、在一些实施例中,还包括模制化合物,模制化合物封装底部填充层、第一电子元件以及第二电子元件并覆盖迹线,模制化合物的刚性大于底部填充层的刚性。

7、在一些实施例中,第一电子元件在第一有源面上具有多个电连接第一导线结构的第一互连件,第一互连件的顶面高于第二电子元件的顶面。

8、在一些实施例中,还包括第一导电柱,第一导电柱位于第二电子元件的一侧以及位于第一互连件下方,第一导电柱电连接第一连接件,第一导电柱的厚度大于第二电子元件的厚度。

9、在一些实施例中,还包括第二导线结构,第二导线结构位于第一导电柱和第二电子元件上方,第二导线结构位于第一电子元件与第一导电柱之间。

10、在一些实施例中,第二导线结构包括暴露第二电子元件的上表面的开口,散热元件贴附在第二电子元件的上表面上。

11、在一些实施例中,还包括引线,引线位于第一导电柱与第二电子元件之间,引线电连接第二导线结构和第一导线结构,引线和第一导线结构之间不包括晶种层。

技术特征:

1.一种半导体封装结构,其特征在于,包括:

2.根据权利要求1所述的半导体封装结构,其特征在于,还包括:

3.根据权利要求2所述的半导体封装结构,其特征在于,还包括:

4.根据权利要求3所述的半导体封装结构,其特征在于,所述底部填充层还包封所述第一电子元件的至少一部分,所述底部填充层填充所述第一电子元件与所述散热元件之间的空间。

5.根据权利要求3或4所述的半导体封装结构,其特征在于,还包括:

6.根据权利要求2所述的半导体封装结构,其特征在于,所述第一电子元件在所述第一有源面上具有多个电连接所述第一导线结构的第一互连件,所述第一互连件的顶面高于所述第二电子元件的顶面。

7.根据权利要求6所述的半导体封装结构,其特征在于,还包括:

8.根据权利要求7所述的半导体封装结构,其特征在于,还包括:

9.根据权利要求8所述的半导体封装结构,其特征在于,所述第二导线结构包括暴露所述第二电子元件的上表面的开口,所述散热元件贴附在所述第二电子元件的所述上表面上。

10.根据权利要求8所述的半导体封装结构,其特征在于,还包括:

技术总结

本申请的实施例提供了一种半导体封装结构,包括第一导线结构、第一电子元件和第二电子元件;其中,第一电子元件位于第一导线结构上,第一电子元件的第一有源面面向第一导线结构;第二电子元件位于第一导线结构上并且与第一电子元件间隔开,第二电子元件的第二有源面面向第一导线结构;第一导线结构包括位于第一有源面和第二有源面下方的迹线,迹线电连接第一电子元件和第二电子元件,迹线在纵向上的全部的投影位于第一有源面的边缘内。本申请的目的在于提供一种半导体封装结构,以至少解决半导体封装结构中第一导线结构的迹线损坏问题。

技术研发人员:闵繁宇,谢孟伟

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20220905

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!