单片多通道保护设备的制作方法

本公开总体上涉及半导体器件领域,并且特别地,涉及单片多通道(例如,双通道)保护设备。

背景技术:

1、瞬态电压抑制(tvs)二极管是设计用于保护敏感电子器件免受高压瞬态影响的电子组件。tvs二极管可以比大多数其他类型的电路保护器件更快地响应过电压事件,并且可用各种表面贴装和通孔电路板安装形式。tvs二极管通常被用于防止电气过应力(electrical overstress),诸如由雷击(lightning strike)、感应负载切换和与数据线和电子电路上的传输相关联的静电放电(electrostatic discharge,esd)引起的过应力。现有的半导体技术无法以有效的方式为电子电路组件提供多通道保护设备。

技术实现思路

1、下面的

技术实现要素:

被提供来以简化形式引入概念的选择,这些概念在下面的具体实施方式中被进一步描述。本实用新型内容不旨在确定所要求保护的主题的关键或本质特征,也不旨在作为辅助确定所要求保护的主题的范围。

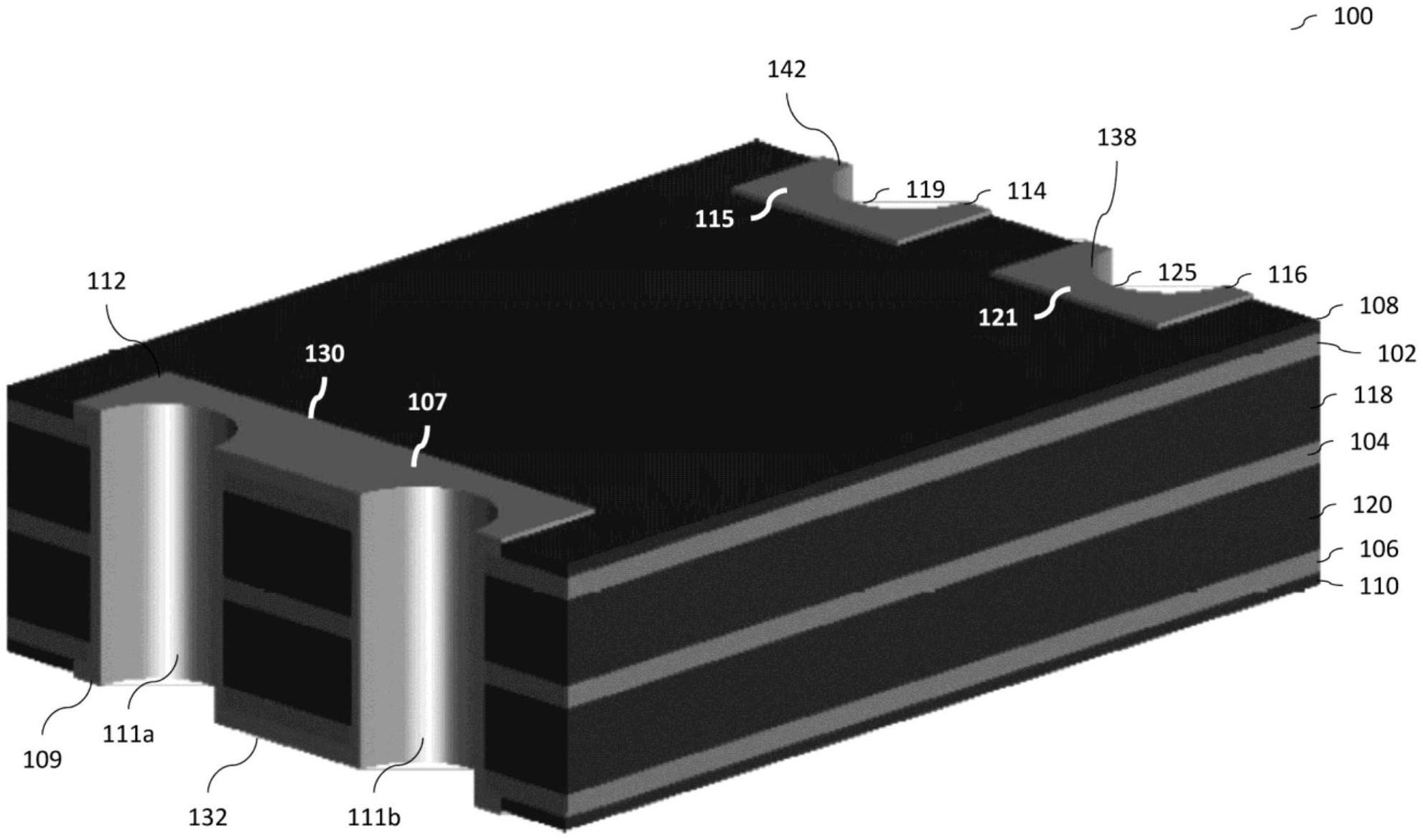

2、在一些实施方式中,当前的主题涉及多通道保护设备/装置。该设备可以包括具有第一芯片附接部分和第二芯片附接部分的第一引线、具有第三芯片附接部分的第二引线、以及具有第四芯片附接部分的第三引线。第一半导体芯片可以被配置为被导电地耦合到第一芯片附接部分和第三芯片附接部分。第二半导体芯片可以被配置为被导电地耦合到第二芯片附接部分和第四芯片附接部分。

3、在一些实施方式中,当前主题可以包括以下可选特征中的一个或多个。该装置可以包括定位在第三芯片附接部分和第一半导体芯片上方的第一基板层。其还可以包括夹在第一芯片附接部分和第二芯片附接部分之间的第二基板层。第三基板层可以被定位在第四芯片附接部分和第二半导体芯片上方。

4、在一些实施方式中,第二引线可以与第三引线导电地分离。

5、在一些实施方式中,该装置可以包括导电地耦合第一引线、第一芯片附接部分、第一半导体芯片、第三芯片附接部分和第二引线的第一导电通道。其还可以包括导电地耦合第一引线、第二芯片附接部分、第二半导体芯片、第四芯片附接部分和第三引线的第二导电通道。

6、在一些实施方式中,第一引线、第一芯片附接部分、第二芯片附接部分、第二引线、第三芯片附接部分、第三引线和第四芯片附接部分中的至少一个可以包括以下中的至少一个:锌、铜、银、铝、金属、其合金和/或其任何组合

7、在一些实施方式中,第一半导体芯片和第二半导体芯片中的至少一个可以包括一个或多个相应的工作区域。第一芯片附接部分、第二芯片附接部分、第三芯片附接部分和第四芯片附接部分中的至少一个可以被配置为导电地耦合到对应的第一半导体芯片和第二半导体芯片的一个或多个相应的工作区域。

8、在一些实施方式中,第一引线、第二引线和第三引线中的至少一个可以被配置为被耦合到以下中的至少一个:基板、印刷电路板及其任何组合。

9、在一些实施方式中,第一填充层可以被配置为被形成用于封装第一半导体芯片、第一芯片附接部分和第三芯片附接部分。第二填充层可以被配置为被形成用于封装第二半导体芯片、第二芯片附接部分和第四芯片附接部分。第一填充层和第二填充层中的至少一个可以由以下中的至少一个制造:环氧化合物、塑料及其任何组合。

10、在一些实施方式中,该设备可以被配置为是表面贴装装置。在一些实施方式中,第一半导体芯片和第二半导体芯片中的至少一个可以包括至少一个瞬态电压抑制器件。

11、在一些实施方式中,当前的主题涉及用于组装和/或制造上述多通道保护设备的方法。该方法可包括提供一个或多个基板层,一个或多个基板层被耦合到一个或多个芯片连接部分;提供一个或多个半导体芯片;将一个或多个半导体芯片中的至少一个耦合到一个或多个芯片连接部分中的至少一个;形成一个或多个填充层以封装耦合的一个或多个半导体芯片中的至少一个和一个或多个芯片连接部分中的至少一个;向形成的一个或多个填充层中的至少一个涂覆一个或多个涂层;以及在封装的一个或多个半导体芯片中的至少一个和一个或多个芯片连接部分中的至少一个中形成一个或多个引线,一个或多个引线被连接到一个或多个芯片连接部分中的至少一个。

12、本文描述的主题的一个或多个变型的细节在附图和下面的描述中被阐述。本文描述主题的其它特征和优点将从描述和附图以及从权利要求书中是显而易见的。

技术特征:

1.一种单片多通道保护设备,其特征在于,包括:

2.根据权利要求1所述的单片多通道保护设备,其特征在于,还包括定位在所述第三芯片附接部分和所述第一半导体芯片上方的第一基板层。

3.根据权利要求2所述的单片多通道保护设备,其特征在于,还包括夹在所述第一芯片附接部分和所述第二芯片附接部分之间的第二基板层。

4.根据权利要求3所述的单片多通道保护设备,其特征在于,还包括定位在所述第四芯片附接部分和所述第二半导体芯片上方的第三基板层。

5.根据权利要求1所述的单片多通道保护设备,其特征在于,所述第二引线与所述第三引线导电地分离。

6.根据权利要求1所述的单片多通道保护设备,其特征在于,还包括导电地耦合所述第一引线、所述第一芯片附接部分、所述第一半导体芯片、所述第三芯片附接部分和所述第二引线的第一导电通道。

7.根据权利要求6所述的单片多通道保护设备,其特征在于,还包括导电地耦合所述第一引线、所述第二芯片附接部分、所述第二半导体芯片、所述第四芯片附接部分和所述第三引线的第二导电通道。

8.根据权利要求1所述的单片多通道保护设备,其特征在于,所述第一半导体芯片和所述第二半导体芯片中的至少一个包括一个或多个相应的工作区域,其中,所述第一芯片附接部分、所述第二芯片附接部分、所述第三芯片附接部分和所述第四芯片附接部分中的至少一个被配置为被导电地耦合到对应的第一半导体芯片和第二半导体芯片的一个或多个相应的工作区域。

9.根据权利要求1所述的单片多通道保护设备,其特征在于,所述第一引线、所述第二引线和所述第三引线中的至少一个被配置为被耦合到以下中的至少一个:基板、印刷电路板及其任何组合。

10.根据权利要求1所述的单片多通道保护设备,其特征在于,第一填充层被配置为被形成用于封装所述第一半导体芯片、所述第一芯片附接部分和所述第三芯片附接部分。

11.根据权利要求10所述的单片多通道保护设备,其特征在于,第二填充层被配置为被形成用于封装所述第二半导体芯片、所述第二芯片附接部分和所述第四芯片附接部分。

12.根据权利要求1所述的单片多通道保护设备,其特征在于,所述单片多通道保护设备被配置为是表面贴装装置。

13.根据权利要求1所述的单片多通道保护设备,其特征在于,所述第一半导体芯片和所述第二半导体芯片中的至少一个包括至少一个瞬态电压抑制器件。

技术总结

一种单片多通道保护设备。该设备包括具有第一芯片附接部分和第二芯片附接部分的第一引线,具有第三芯片附接部分的第二引线,以及具有第四芯片附接部分的第三引线。第一半导体芯片被配置为被导电地耦合到第一芯片附接部分和第三芯片附接部分。第二半导体芯片被配置为被导电地耦合到第二芯片附接部分和第四芯片附接部分。

技术研发人员:张环,石磊,高超

受保护的技术使用者:力特半导体(无锡)有限公司

技术研发日:20221014

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!