一种芯片封装结构的制作方法

本申请涉及芯片封装,具体涉及一种芯片封装结构。

背景技术:

1、随着半导体及集成电路技术的进步,系统集成要求进一步提升,当前的电子电路设计和制造,都朝着尺寸更小、集成密度更高的方向发展,相当大的工作都集中在多芯片封装领域。在先进的封装形式中,通过sip或soc技术,将多个功率芯片、多个逻辑芯片等组装在基板上,然后集成于一个封装体中,形成相应的芯片封装结构。

2、目前,传统的芯片封装结构中,其内部功率芯片与逻辑芯片之间的数据连接,一般是通过外围电路来实现的,导致其数据传输效率无法得到进一步提升,且导致其外围电路的复杂度大大增加。

技术实现思路

1、本申请实施例提供一种芯片封装结构,以改善传统的芯片封装结构中通过外围电路实现其功率芯片与逻辑芯片之间的数据连接,导致其数据传输效率不高、外围电路复杂的技术问题。

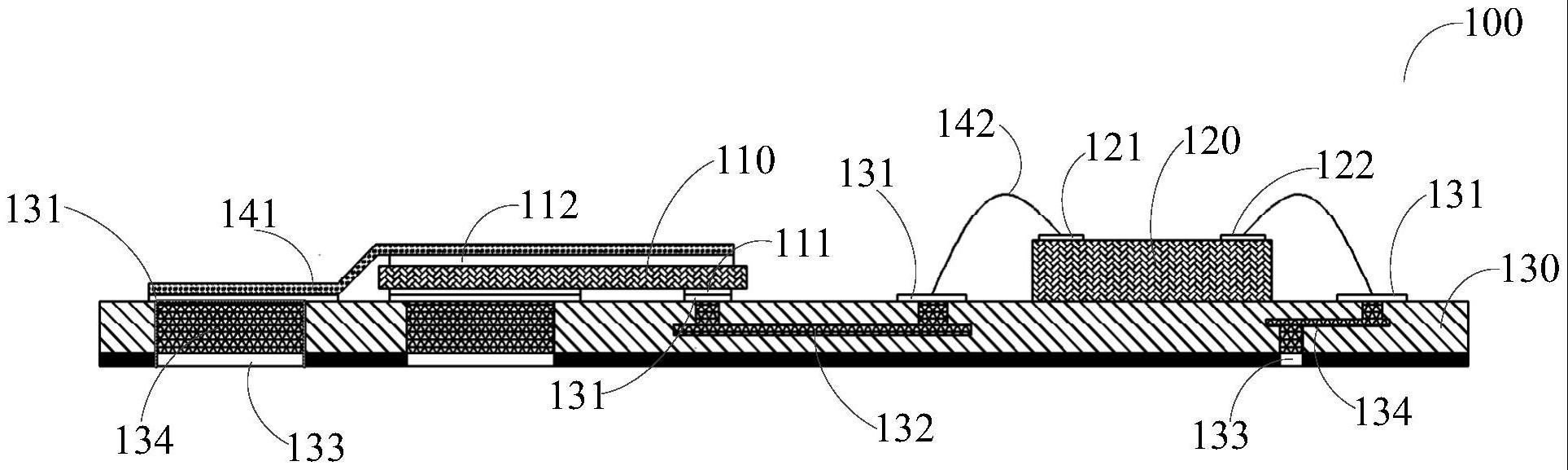

2、为此,本申请提供一种芯片封装结构,包括至少一个功率芯片、至少一个逻辑芯片以及基板,所述基板的一侧表面分布有若干焊盘,所述功率芯片上设置有第一数据传输焊脚,所述逻辑芯片上设置有第二数据传输焊脚,所述功率芯片及所述逻辑芯片分别封装固定在所述基板设置有所述若干焊盘的一侧表面上,且所述第一数据传输焊脚及所述第二数据传输焊脚均对应与一个所述焊盘键合连接,所述基板内还设置有数据传输布线层,所述数据传输布线层的一端与键合连接所述第一数据传输焊脚的所述焊盘连接,所述数据传输布线层的另一端与键合连接所述第二数据传输焊脚的所述焊盘连接。

3、可选的,在一些实施例中,所述功率芯片上还设置有第一电路传输焊脚,所述逻辑芯片上还设置第二电路传输焊脚,且所述第一电路传输焊脚及所述第二电路传输焊脚均对应与一个所述焊盘键合连接;

4、所述基板的另一侧表面还分布有若干金属触点,所述基板内还设置有电路布线层,所述若干金属触点通过所述电路布线层连接除与所述数据传输布线层连接的所述焊盘之外的其余所有焊盘。

5、可选的,在一些实施例中,所述第二数据传输焊脚及所述第二电路传输焊脚分别凸设于所述逻辑芯片面向所述基板的一侧表面上,且所述第二数据传输焊脚及所述第二电路传输焊脚分别与对应的所述焊盘进行抵接键合连接,以使得所述逻辑芯片倒装在所述基板上。

6、可选的,在一些实施例中,所述第二数据传输焊脚的四周及所述第二电路传输焊脚的四周还分别填充有填充胶。

7、可选的,在一些实施例中,所述基板上罩设有罩设所述功率芯片或所述逻辑芯片的电磁屏蔽罩。

8、可选的,在一些实施例中,所述功率芯片的上表面或所述逻辑芯片的上表面与上方的所述电磁屏蔽罩间隔预设距离,或所述功率芯片的上表面或所述逻辑芯片的上表面与上方的所述电磁屏蔽罩之间夹设有绝缘胶。

9、可选的,在一些实施例中,所述电磁屏蔽罩与所述基板接触的表面填充有粘黏胶。

10、可选的,在一些实施例中,所述基板的一侧表面还填充有封装胶,以封装密封所述功率芯片及所述逻辑芯片。

11、可选的,在一些实施例中,所述封装胶的上表面固设有散热鳍片。

12、可选的,在一些实施例中,所述封装胶为散热胶体,所述封装胶的上表面呈鳍片状或固设有散热鳍片。

13、在本申请中,芯片封装结构中的功率芯片及逻辑芯片分别封装固定在基板设置有若干焊盘的一侧表面上,且第一数据传输焊脚及第二数据传输焊脚均对应与一个焊盘键合连接,基板内还设置有数据传输布线层,数据传输布线层的一端与键合连接第一数据传输焊脚的焊盘连接,数据传输布线层的另一端与键合连接第二数据传输焊脚的一个焊盘连接。这样一来,本申请芯片封装结构中的功率芯片和逻辑芯片之间的数据连接主要通过其内部的基板内的信号布线层来完成,相比现有外围电路的实现方式,可有效提高其数据传输效率,降低其外围电路的复杂度。

技术特征:

1.一种芯片封装结构,其特征在于,包括至少一个功率芯片、至少一个逻辑芯片以及基板,所述基板的一侧表面分布有若干焊盘,所述功率芯片上设置有第一数据传输焊脚,所述逻辑芯片上设置有第二数据传输焊脚,所述功率芯片及所述逻辑芯片分别封装固定在所述基板设置有所述若干焊盘的一侧表面上,且所述第一数据传输焊脚及所述第二数据传输焊脚均对应与一个所述焊盘键合连接,所述基板内还设置有数据传输布线层,所述数据传输布线层的一端与键合连接所述第一数据传输焊脚的所述焊盘连接,所述数据传输布线层的另一端与键合连接所述第二数据传输焊脚的所述焊盘连接。

2.根据权利要求1所述的芯片封装结构,其特征在于,所述功率芯片上还设置有第一电路传输焊脚,所述逻辑芯片上还设置第二电路传输焊脚,且所述第一电路传输焊脚及所述第二电路传输焊脚均对应与一个所述焊盘键合连接;

3.根据权利要求2所述的芯片封装结构,其特征在于,所述第二数据传输焊脚及所述第二电路传输焊脚分别凸设于所述逻辑芯片面向所述基板的一侧表面上,且通过导电凸块与所述第二数据传输焊脚及所述第二电路传输焊脚分别与对应的所述焊盘进行抵接键合连接,以使得所述逻辑芯片倒装在所述基板上。

4.根据权利要求3所述的芯片封装结构,其特征在于,所述第二数据传输焊脚的四周及所述第二电路传输焊脚的四周分别填充有填充胶。

5.根据权利要求1所述的芯片封装结构,其特征在于,所述基板上罩设有罩设所述功率芯片或所述逻辑芯片的电磁屏蔽罩。

6.根据权利要求5所述的芯片封装结构,其特征在于,所述功率芯片的上表面或所述逻辑芯片的上表面与上方的所述电磁屏蔽罩间隔预设距离,或,所述功率芯片的上表面或所述逻辑芯片的上表面与上方的所述电磁屏蔽罩之间夹设有绝缘胶。

7.根据权利要求5所述的芯片封装结构,其特征在于,所述电磁屏蔽罩与所述基板接触的表面填充有粘黏胶。

8.根据权利要求1-7任一项所述的芯片封装结构,其特征在于,所述基板的一侧表面还填充有封装胶,以封装密封所述功率芯片及所述逻辑芯片。

9.根据权利要求8所述的芯片封装结构,其特征在于,所述封装胶的上表面固设有散热鳍片。

10.根据权利要求8所述的芯片封装结构,其特征在于,所述封装胶为散热胶体,所述封装胶的上表面呈鳍片状或固设有散热鳍片。

技术总结

本申请公开一种芯片封装结构,属于芯片封装技术领域,该芯片封装结构包括至少一个功率芯片、至少一个逻辑芯片以及基板,基板的一侧表面分布有若干焊盘,功率芯片上设置有第一数据传输焊脚,逻辑芯片上设置有第二数据传输焊脚,功率芯片及逻辑芯片分别封装固定在基板设置有若干焊盘的一侧表面上,且第一数据传输焊脚及第二数据传输焊脚均对应与一个焊盘键合连接,基板内还设置有数据传输布线层,数据传输布线层的一端与键合连接第一数据传输焊脚的一个焊盘连接,数据传输布线层的另一端与键合连接第二数据传输焊脚的一个焊盘连接。本申请的技术方案,其可有效提高其数据传输效率,降低其外围电路的复杂度。

技术研发人员:赖振楠,吴奕盛

受保护的技术使用者:深圳宏芯宇电子股份有限公司

技术研发日:20221102

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!