静电夹盘及等离子体处理装置的制作方法

本技术涉及半导体设备,特别涉及一种静电夹盘及应用该静电夹盘的等离子体处理装置。

背景技术:

1、在半导体器件的制造过程中,通常采用静电夹盘(electrostatic chuck,esc)将基板静电吸附在基板支撑件上。基板可以是硅、砷化镓、磷化铟或其他合适的材料。

2、传统上,静电夹盘包括陶瓷主体,所述陶瓷主体中嵌有一个或多个吸附电极。在har(高深宽比)等离子体刻蚀等应用场景中,需要使用很高的偏压功率,以达到目标刻蚀轮廓。然而在高功率偏压的使用环境中,静电夹盘会承受很大的分压,静电夹盘上的氦气孔和升降销孔中的气体在分压的作用下容易产生电离,造成孔内打火。

3、现有技术中,静电夹盘中的电极多通过丝网印刷的方式嵌入陶瓷中,电极一般都很薄,在烧结过程中,由于陶瓷和电极浆料的收缩,电极厚度会出现不均匀的现象,可能会导致电极层局部产生缺陷。在通电后,电荷容易困在缺陷区域,形成残余电荷,这将不利于工艺后的基板解吸附。

技术实现思路

1、本实用新型的目的是提供一种静电夹盘及等离子体处理装置,用于降低静电夹盘中的分压和改善晶圆的解吸附。

2、为了实现以上目的,本实用新型通过以下技术方案实现:

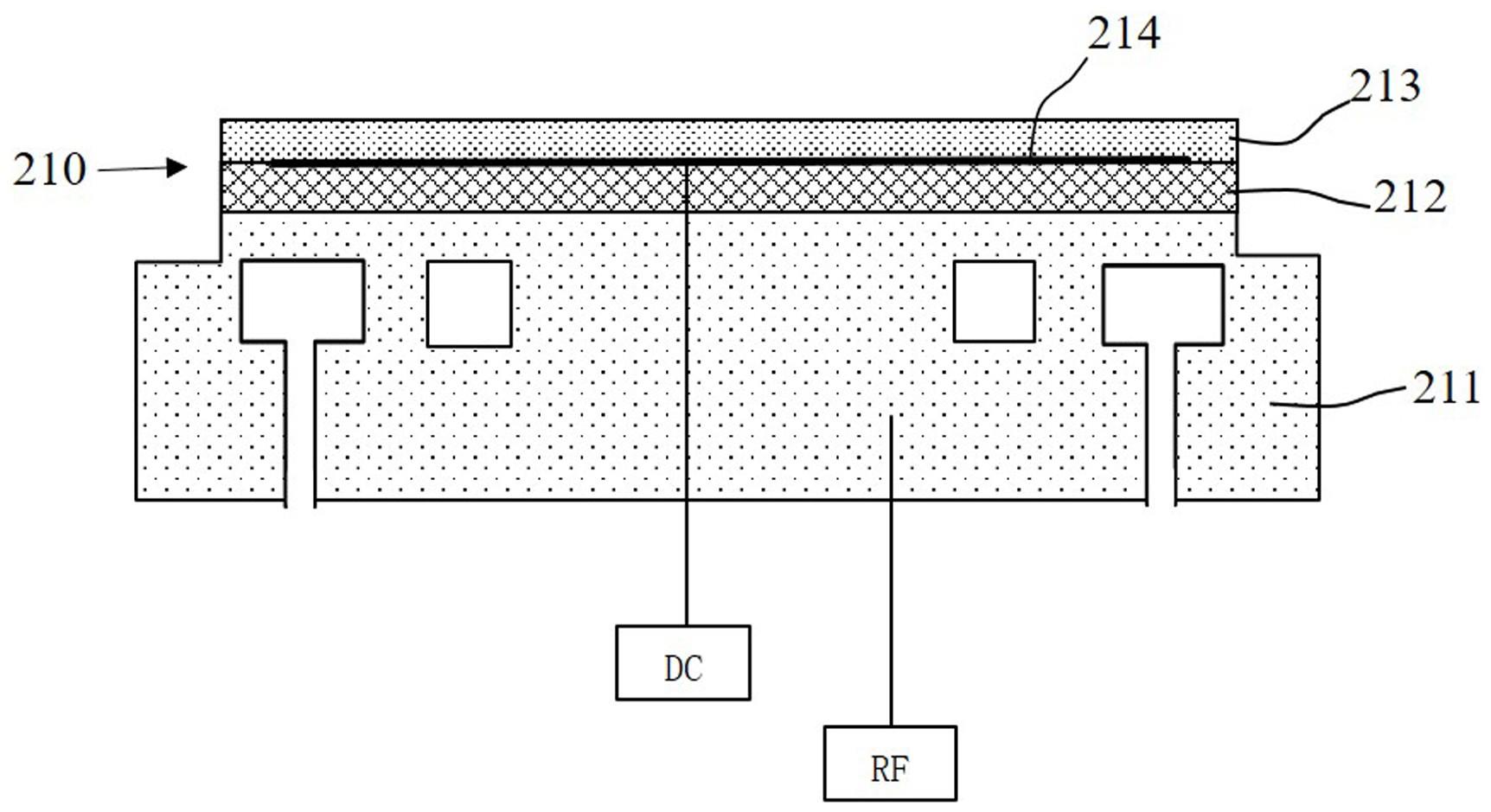

3、一种静电夹盘,所述静电夹盘包括:第一介电层,所述第一介电层具有第一电阻率;第二介电层,所述第二介电层的顶表面用于支撑晶圆;所述第二介电层具有第二电阻率,所述第二电阻率大于所述第一电阻率;电极,所述电极位于第一介电层的顶表面和第二介电层的底表面之间,且所述电极与第一介电层的顶表面和第二介电层的底表面均接触连接,所述电极用于产生静电吸力。

4、可选地,所述第一介电层为掺杂的陶瓷。

5、可选地,所述掺杂物为si、c、mg、mgo和tio2中的一种或多种;所述陶瓷为氧化铝、氮化铝、碳化硅和氮化硼中的一种或多种。

6、可选地,所述第一电阻率为106-1013ω·m。

7、可选地,所述第二介电层为无掺杂的陶瓷,所述陶瓷为氧化铝、氮化铝、碳化硅和氮化硼中的一种或多种。

8、可选地,所述第二电阻率为1013-1019ω·m。

9、可选地,所述第二介电层的厚度占所述第一介电层和第二介电层总厚度的5%-55%。

10、可选地,所述第一介电层的厚度为0.1-5mm。

11、可选地,所述第二介电层的厚度为0.2-2mm。

12、可选地,所述静电夹盘还包括设置在所述第一介电层下方的加热装置。

13、可选地,所述静电夹盘还包括设置在所述加热装置下方的阻热层。

14、可选地,所述静电夹盘还包括基座,所述基座内部设有冷却液通道。

15、可选地,所述第一介电层嵌入设置在基座顶部,所述第一介电层的顶表面与基座的顶表面平齐,所述第二介电层设置在基座上并完全覆盖所述第一介电层。

16、可选地,所述第二介电层的顶表面设有多个均匀分布或非均匀分布的凸起部,所述凸起部的高度范围为2~3μm。

17、可选地,所述第一介电层和第二介电层的外侧壁设有耐等离子体腐蚀的镀膜。

18、本实用新型还提供了一种等离子体处理装置,所述等离子体处理装置包括等离子体处理腔室,所述等离子体处理腔室的内部设有如上所述的静电夹盘。

19、可选地,所述等离子体处理装置包括若干个射频电源,射频电源用于在所述等离子体处理腔室的内部产生等离子体,所述若干个射频电源中的至少一个的功率大于5000w。

20、与现有技术相比,本实用新型的有益效果在于:

21、(1)本实用新型提出的静电夹盘中,将电极置于低电阻率介电层和高电阻率介电层之间,相对于传统cb型静电夹盘,减薄了高电阻率介电层的厚度,大大降低了阻抗,使其能够适用于高功率应用场景,而不会导致打火或电弧放电等现象的发生;

22、(2)陷在电极缺陷中的电荷可以通过下方的低电阻率介电层移动流走,而不会造成晶圆解吸附困难的问题;

23、(3)第一介电层212未处于完整的电路回路中,不会出现jr静电夹盘的“山峰”电荷,避免了“山峰”电荷导致的解吸附困难的问题。

技术特征:

1.一种静电夹盘,其特征在于,所述静电夹盘包括:

2.如权利要求1所述的静电夹盘,其特征在于,所述第一电阻率为106-1013ω·m。

3.如权利要求1所述的静电夹盘,其特征在于,所述第二介电层为无掺杂的陶瓷,所述陶瓷为氧化铝、氮化铝、碳化硅和氮化硼中的一种。

4.如权利要求1所述的静电夹盘,其特征在于,所述第二电阻率为1013-1019ω·m。

5.如权利要求1所述的静电夹盘,其特征在于,所述第二介电层的厚度占所述第一介电层和第二介电层总厚度的5%-55%。

6.如权利要求1所述的静电夹盘,其特征在于,所述第一介电层的厚度为0.1-5mm。

7.如权利要求1所述的静电夹盘,其特征在于,所述第二介电层的厚度为0.2-2mm。

8.如权利要求1所述的静电夹盘,其特征在于,所述静电夹盘还包括设置在所述第一介电层下方的加热装置。

9.如权利要求8所述的静电夹盘,其特征在于,所述静电夹盘还包括设置在所述加热装置下方的阻热层。

10.如权利要求1-9任一所述的静电夹盘,其特征在于,所述静电夹盘还包括基座,所述基座内部设有冷却液通道。

11.如权利要求10所述的静电夹盘,其特征在于,所述第一介电层嵌入设置在基座顶部,所述第一介电层的顶表面与基座的顶表面平齐,所述第二介电层设置在基座上并完全覆盖所述第一介电层。

12.如权利要求1所述的静电夹盘,其特征在于,所述第二介电层的顶表面设有多个均匀分布或非均匀分布的凸起部,所述凸起部的高度范围为2~3μm。

13.如权利要求1所述的静电夹盘,其特征在于,所述第一介电层和第二介电层的外侧壁设有耐等离子体腐蚀的镀膜。

14.一种等离子体处理装置,其特征在于,所述等离子体处理装置包括等离子体处理腔室,等离子体处理腔室的内部设有如权利要求1-13任一所述的静电夹盘。

15.如权利要求14所述的等离子体处理装置,其特征在于,所述等离子体处理装置包括若干个射频电源,射频电源用于在所述等离子体处理腔室的内部产生等离子体,所述若干个射频电源中的至少一个的功率大于5000w。

技术总结

本技术公开了一种静电夹盘及等离子体处理装置。静电夹盘包括第一介电层和第二介电层,第二介电层的电阻率大于第一介电层的电阻率;还包括用于产生静电吸力的电极,电极位于第一介电层的顶表面和第二介电层的底表面之间。本技术提出的静电夹盘能够使用于高功率应用场景,而不会导致打火或电弧放电等现象的发生;还能够改善晶圆解吸附困难的问题。

技术研发人员:左涛涛,吴狄

受保护的技术使用者:中微半导体设备(上海)股份有限公司

技术研发日:20221215

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!