蚀刻方法与流程

本发明涉及利用了等离子的包含半导体的处理对象的膜层例如sige以及ge的蚀刻方法。

背景技术:

1、正在推进半导体器件的微细化和三维化所带来的集成度提升,在逻辑器件中,在14nm节点以后,场效应晶体管(fet:field effect transistor)的构造从二维平面型移转到三维fin型。面向进一步的集成度提升,现在正在推进全环绕栅极(gaa:gate allaround)型fet的开发。gaa型fet具有沟道的周围完全被栅极包围的构造,具有在垂直方向大量层叠被称作纳米片的薄膜状的沟道、或被称作纳米丝的细线状的沟道的构造。作为该沟道材料,现在使用si,在技术节点为5nm以后的下一代中,将比硅(si)移动度高的锗(ge)用作沟道材料的方式被视作有前途。

2、在作为沟道材料而使用si的情况的gaa型fet的制造工艺中,首先,制作将用作沟道材料的si的层和用作牺牲层的硅锗(sige)的层交替外延生长而得到的多层构造。接下来,在对该多层构造进行各向异性干式蚀刻后,相对于si沟道层选择性地各向同性蚀刻作为牺牲层的sige层。然后,在蚀刻了sige层的区域,将内部间隔填充,来形成源极、漏极、栅极电极,由此完成以si为沟道材料的gaa型fet。

3、另一方面,在使用技术节点5nm以后的下一代中变得有力的新的沟道材料的ge的情况下,使用与以si为沟道材料的情况不同的多层构造和制作工艺。在作为沟道材料而使用ge的情况的gaa型fet的制造工艺中,首先,制作将用作沟道材料的ge的层和用作牺牲层的sige的层交替外延生长而得到的多层构造。接下来,在对该多层构造进行各向异性干式蚀刻后,相对于ge沟道层选择性地各向同性蚀刻作为牺牲层的sige层。然后,在蚀刻了sige层的区域填充内部间隔,来形成源极、漏极、栅极电极,由此完成以ge为沟道材料的gaa型fet。

4、作为相对于si选择性地蚀刻sige的技术,例如使用利用了氟化氢(hf)与过氧化氢(h2o2)、醋酸(ch3cooh)的混合液的方法。但由于加工尺寸的微细化推进和使用了纵横比高的三维构造,在湿式处理中,药液的表面张力所引起的图案坍塌的问题等明显化。例如报告了以下情况:在使用了硅的高纵横比图案的情况下,在使图案间隔变窄时,因冲洗液干燥时的表面张力而开始坍塌的图案间隔的极限值与纵横比的平方成比例地变大。因此,强烈期望开发不使用药液而各向同性地蚀刻各种膜的工艺手法。与此对应地,作为不使用药液而使用等离子来均匀性良好地各向同性蚀刻sige的现有技术,例如提出jp特开2021-150488号公报(专利文献1)、美国专利申请公开第2018/0218915号说明书(专利文献2)。

5、在专利文献1中公开了如下技术:在第一步骤中使用含氟和氧的自由基的远程等离子将sige的表面氧化后,在第二步骤中,通过hf/nh3气体处理(nh3:氨)和加热处理来除去氧化膜,重复这样的循环,相对于si选择性地蚀刻sige。

6、在专利文献2中公开了如下技术:在第一步骤中通过含氢的等离子对sige表面进行了还原处理后,在第二步骤中,通过含氧的等离子对sige表面进行氧化处理,在第三步骤中进行加热,重复这样的循环,来相对于si选择性地蚀刻sige。

7、现有技术文献

8、专利文献

9、专利文献1:jp特开2021-150488号公报

10、专利文献2:美国专利申请公开第2018/0218915号说明书

技术实现思路

1、发明要解决的课题

2、在上述的现有技术中,关于如下点并未考虑,在下一代器件的开发时会产生问题。

3、即,在上述现有技术中,虽然公开了相对于si选择性地且均匀性良好地循环蚀刻sige的技术,但并未考虑相对于ge选择性地且均匀性良好地循环蚀刻sige的技术。因此,存在无法应对技术节点5nm以后的代中变得有力的以ge为沟道材料的gaa型fet的制造工艺这样的问题。在现有技术中,在sige表面生成氧化物,通过将其除去,来相对于si实现选择性的蚀刻。该技术利用了膜中的ge含有量越多则sige的表面氧化越易于推进、ge的氧化物的挥发性比si氧化物的挥发性高的性质。但若将这样的现有的sige的原子层蚀刻运用于下一代的以ge为沟道材料的gaa型fet制造,则在蚀刻sige牺牲层时,极力抑制蚀刻量从而不蚀刻而应残留的ge沟道层的蚀刻会推进,存在会意外除去ge沟道层这样的问题。

4、如此地,在现有的作为反应生成物而使用表面氧化物的sige的原子层蚀刻技术中,在ge含有量大的材料中蚀刻量变大。因此,虽然适合于现在推进开发的以si为沟道材料的gaa型fet的制造,但在以ge为沟道材料的下一代以后的gaa型fet的器件制造工序中,认为其运用受到限制。

5、本发明的目的在于,提供相对于ge选择性地蚀刻sige且蚀刻量的均匀性高的循环蚀刻技术。

6、本发明的其他目的和新的特征会从本说明书的描述以及附图得以明确。

7、用于解决课题的手段

8、若简单说明本发明当中的代表性的方案的概要,则如下述那样。

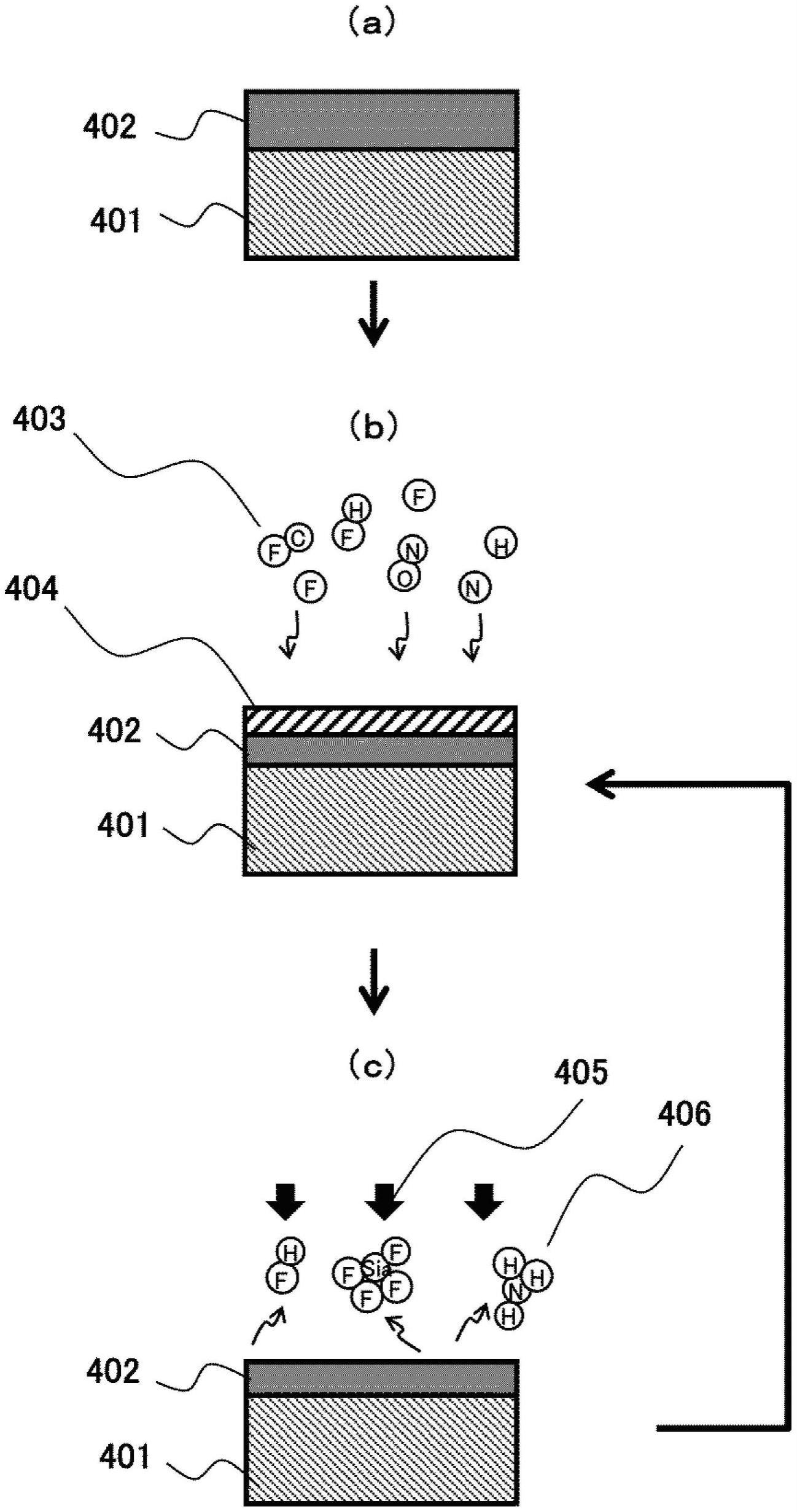

9、本发明的一方式所涉及的蚀刻技术对配置于晶片的表面的包含sige的处理对象的膜层进行蚀刻,具备如下工序:对膜层的表面供给包含氟、氢、氮的反应性的粒子,从而在膜层的表面形成具有氮-氢键的反应层;加热膜层来使反应层脱离。

10、发明的效果

11、若简单说明通过本发明当中的代表性的方案得到的效果,则如以下那样。

12、根据本发明的蚀刻技术,能相对于ge选择性地蚀刻sige,且能提升蚀刻量的均匀性。例如,能提供一种各向同性原子层蚀刻技术,在以ge为沟道材料的gaa型fet的制造工序中,在相对于ge沟道层选择性地蚀刻sige牺牲层的情况下,晶片面内方向、图案深度方向上的蚀刻量的均匀性高。

技术特征:

1.一种蚀刻方法,对配置于晶片的表面的包含半导体的处理对象的膜层进行蚀刻,其特征在于,具备以下工序:

2.根据权利要求1所述的蚀刻方法,其特征在于,

3.根据权利要求1或2所述的蚀刻方法,其特征在于,

4.根据权利要求1~3中任一项所述的蚀刻方法,其特征在于,

5.根据权利要求1~4中任一项所述的蚀刻方法,其特征在于,

6.根据权利要求1~5中任一项所述的蚀刻方法,其特征在于,

7.根据权利要求1所述的蚀刻方法,其特征在于,

技术总结

提供蚀刻量的均匀性高且蚀刻处理的成品率得以提升的蚀刻技术。在对配置于晶片的表面的包含SiGe的处理对象的膜层进行蚀刻的蚀刻方法中,具备如下工序:对膜层的表面供给包含氟、氢、氮的反应性的粒子,来在该膜层的表面形成包含氮‑氢键的反应层;和加热膜层来使反应层脱离。

技术研发人员:筱田和典,滨村浩孝,前田贤治,横川贤悦,阮氏翠儿,石川健治,堀胜

受保护的技术使用者:株式会社日立高新技术

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!