保护电路和半导体器件的制作方法

本公开涉及一种保护电路和半导体器件。

背景技术:

1、专利文献1公开了一种具有静电保护元件的射频集成电路。静电保护元件将耗尽型场效应晶体管和增强型场效应晶体管彼此串联电耦合,并且进一步将电容器与增强型场效应晶体管并联电耦合。场效应晶体管包括mesfet、栅极结型fet、hemt等。

2、在静电保护元件中,当从外部输入噪声或高电压脉冲时,增强型场效应晶体管执行击穿操作并且其阻抗降低以允许噪声或高电压脉冲的放电。

3、另外,专利文献2公开了浪涌保护元件和半导体器件。浪涌保护元件包括pnp双极晶体管。双极晶体管配置有作为集电极区域的p型gan层、作为基极区域的algan层和gan层,以及作为发射极区域的p型gan层。

4、在浪涌保护元件中,浪涌作为穿通电流被吸收。

5、此外,专利文献3公开了一种包括静电击穿保护电路的半导体集成电路。静电击穿保护电路包括二极管耦合晶体管。使用双极晶体管或mosfet作为晶体管。

6、引文列表

7、专利文献

8、专利文献1:日本专利no.4843927

9、专利文献2:国际公开no.wo 2014/103126a1

10、专利文献3:日本专利no.4803747

技术实现思路

1、已经为下一代移动终端开发了在毫米波段操作的射频功率放大器。使用包括基于gan的宽带隙材料的绝缘栅场效应晶体管来构造射频功率放大器。具体而言,使用金属-绝缘体-半导体场效应晶体管(metal insulator semiconductor field effecttransistor;在下文中简称为“misfet”)。

2、上述专利文献1中公开的静电保护元件、专利文献2中公开的浪涌保护元件以及专利文献3中公开的静电击穿保护电路各自使用p型层。在基于gan的工艺中,p型杂质的激活率非常低,这使得p型gan难以生产并且使得其在制造工艺中的工艺亲和性(量产性)差。换句话说,难以使用p型gan来实现保护元件。因而,期望静电放电(electro staticdischarge;在下文中简称为“esd”)稳健性或雪崩(avalanche)稳健性优异的保护电路和半导体器件。

3、本技术提供了一种在esd稳健性或雪崩稳健性方面优异的保护电路和半导体器件。

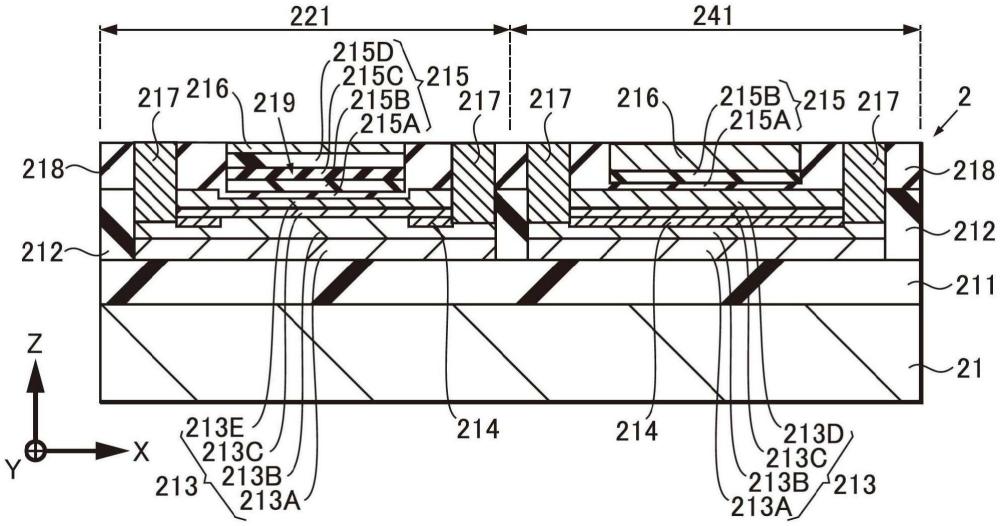

4、根据本公开的第一实施例的保护电路包括第一绝缘栅场效应晶体管,其中:第一主电极耦合在外部端子与内部电路之间;第二主电极和栅极电极耦合到基准电源;并且在栅极绝缘膜中提供有被配置为累积热载流子的电荷累积部。

5、根据本公开的第二实施例的半导体器件包括:在基板上提供的外部端子;在基板上提供并耦合到外部端子的内部电路;以及保护电路,在基板上提供并且包括第一绝缘栅场效应晶体管,其中:第一主电极耦合在外部端子与内部电路之间;第二主电极和栅极电极耦合到基准电源;并且在栅极绝缘膜中提供有被配置为累积热载流子的电荷累积部。

技术特征:

1.一种保护电路,包括

2.根据权利要求1所述的保护电路,还包括串联电耦合在所述栅极电极与所述第二主电极之间的电阻。

3.根据权利要求2所述的保护电路,还包括:

4.一种半导体器件,包括:

5.根据权利要求4所述的半导体器件,其中保护电路还包括串联电耦合在所述栅极电极与所述第二主电极之间的电阻。

6.根据权利要求5所述的半导体器件,还包括:

7.根据权利要求4所述的半导体器件,其中所述电荷累积部被配置有其中氧化物膜、氮化物膜和氧化物膜逐层堆叠的结构。

8.根据权利要求7所述的半导体器件,其中

9.根据权利要求7所述的半导体器件,其中所述电荷累积部包括al2o3、堆叠在所述al2o3上的hfo2、堆叠在所述hfo2上的sin以及堆叠在所述sin上的sio2。

10.根据权利要求4所述的半导体器件,其中所述第一绝缘栅场效应晶体管包括化合物半导体。

11.根据权利要求10所述的半导体器件,其中所述化合物半导体包括gan或gaas。

12.根据权利要求11所述的半导体器件,其中所述第一绝缘栅场效应晶体管包括inaln。

13.根据权利要求4所述的半导体器件,其中所述第一绝缘栅场效应晶体管使热载流子累积在所述电荷累积部中并且使阈值电压从耗尽型转移至正方向到增强型。

14.根据权利要求4所述的半导体器件,其中

15.根据权利要求5所述的半导体器件,其中所述电阻被形成为100ω以上且10mω以下。

16.根据权利要求4所述的半导体器件,还包括功率放大器,该功率放大器包括被形成为耗尽型的第二绝缘栅场效应晶体管。

17.根据权利要求16所述的半导体器件,其中

18.根据权利要求4所述的半导体器件,还包括串联电耦合在所述外部端子与所述第一主电极之间的电感电阻。

19.根据权利要求4所述的半导体器件,还包括串联电耦合在所述外部端子与所述内部电路之间的耦合电容器。

20.根据权利要求4所述的半导体器件,其中多个所述第一绝缘栅场效应晶体管被对称地提供。

技术总结

此保护电路包括第一绝缘栅场效应晶体管,其第一主电极耦合在外部端子与内部电路之间;其第二主电极和栅极电极耦合到基准电源;并且其中在栅极绝缘膜中提供有能够累积热载流子的电荷累积部。

技术研发人员:西田知矢,本山理一,二井英昭

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!