有源通孔的制作方法

本发明涉及半导体集成电路。更具体而言,本发明涉及一种用于半导体集成电路和芯片中的有源通孔(active via)。

背景技术:

1、半导体工业付出了很多努力来通过增加半导体集成电路的能力来增加半导体集成电路的实用性和功能性,同时相应地增加其复杂度和尺寸。例如,苹果公司最近设计的m1max集成电路已拥有超过570亿个晶体管,并包括多个处理器内核和诸如图形处理单元之类的专用处理器。

2、由于这种集成电路(通常被称为“芯片”)的尺寸和复杂度,“芯片”内的组件通常使用通常被称为“通孔”的互连进行电气链接。局部互连提供局部电路内(例如,在其上形成集成电路的管芯内的层之间)的连接,并且全局互连实现不同管芯(即,在不同晶圆上或由不同公司制造的管芯/电路等)之间的连接。

3、特别地,穿硅通孔(“tsv”)使得能够通过将两个或更多个原本分立的电路垂直连接成单个包装来制造集成电路,诸如2.5d或3d集成电路(“3dic”)。

4、常规的通孔,无论是局部通孔还是全局通孔,都是无源电路元件。对于这种通孔,对通过常规通孔连接的电路元件的唯一控制是选择通孔的固有特性(尺寸、电阻率等),这些特性不能通过施加外力(例如,电压偏置、电流偏置等)来进一步修改。

5、但是,随着芯片设计变得越来越复杂,对芯片各部分的控制和管理变得更具挑战性,并且所需的管理电路包括诸如ram、存储器控制器、电源网络等组件,这些组件通常被称为“非核心”组件。随着芯片复杂度的增加,非核心组件的复杂度和尺寸也相应增加。

6、此外,对于芯片内可以使用多少常规通孔存在限制。具体而言,将两个或更多个通孔靠近放置可能会导致电磁干扰(“emi”)问题,诸如两个或更多个常规通孔之间的串扰。

7、随着芯片复杂度的增加,emi(诸如常规通孔之间的串扰)的可能性也由于通孔彼此接近而增加。具体而言,尤其是由于尝试减少非核心组件所需的面积,可能会产生电耦合通孔(芯片内各层之间的电感耦合)或伪电耦合通孔(由电感耦合和物理连接的组合产生)。

8、在尝试降低emi时,在一些情况下,可以改变通孔尺寸,或者可以向芯片添加更多工艺层,以构造常规的通孔(诸如同轴通孔)。附加的绝缘层旨在减少电磁耦合,从而减少常规通孔之间的串扰,但这种改变会导致附加的制造成本和/或设计妥协。

9、同样,制造常规通孔的处理步骤需要在通孔周围有“禁止区(keep-out-zone)”(koz),这进一步减少了可用于核心组件的面积。在一些情况下,需要将koz设为通孔直径的两倍。这是因为常规的通孔通常需要在相对高的温度下执行的工艺步骤,并且这样的温度会显著改变相邻组件的特性,这可能对电路元件有害。例如,相邻组件的可能因此受到影响的特性包括信号通过通孔时的时序违规。

10、虽然无论是否与数据、电源或其它功能相关,常规通孔在芯片中的电路元件之间的信号迁移中都发挥着关键作用,但与常规通孔相关联的挑战和缺点仍然存在。

11、常规通孔的进一步限制涉及芯片的功耗。具体而言,为了降低整个芯片(诸如片上系统“soc”或系统级包装“sip”及类似变体)的功耗,“控制策略”(诸如“暗硅”管理)或输入/输出管理通常被实现以减少芯片上未用于给定功能的区域的功率消耗。

12、此外,常规的通孔不提供芯片内的区域、部分、层之间的任何静电保护或信号抑制。

13、控制策略的各种实施方式具有共同的途径,其中设定频率信号处的特定电压(动态电压缩放或dvs技术),或设定电压信号处的特定频率(动态频率缩放或dfs技术),或电压-频率信号的独特组合(动态电压-频率缩放或dvfs技术)从管理电路通过常规的通孔(诸如tsv)发送到芯片的一个或多个区域以将其置于“空闲模式”,从而减少其功率消耗。在需要其功能的情况下,通过相同的机制,从管理电路发送信号以将芯片的一个或多个区域从空闲模式移除。

14、但是,虽然这样的控制策略可以在一定程度上降低芯片的功率需求,但是芯片的随时处于空闲模式的区域仍然消耗功率,尽管以降低的水平消耗功率。

15、因此,期望具有能够减轻或避免这些问题中的至少一些问题的有源通孔。

技术实现思路

1、本发明的一个目的是提供一种新颖的有源通孔,其消除或减轻现有技术的至少一个缺点。

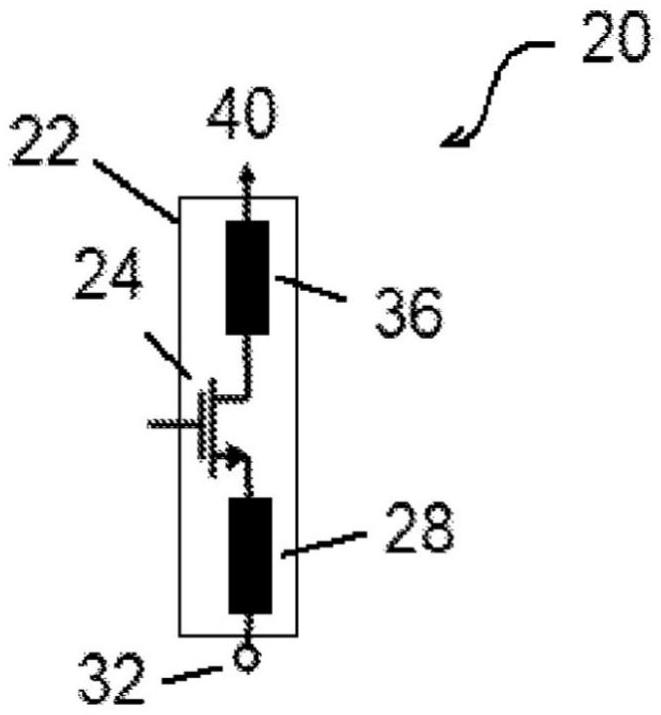

2、根据本发明的第一方面,提供了一种用于芯片中的有源通孔,该有源通孔包括:具有第一端和第二端的通孔;与通孔集成的开关元件,该开关元件包括至少一个晶体管,该至少一个晶体管具有源极接触件、漏极接触件和栅极接触件,其中源极接触件与芯片的第一电路元件电接触,漏极接触件与芯片的第二电路元件电接触,并且栅极接触件与芯片的第三电路元件电接触,并且其中,当第一电路元件、第二电路元件或第三电路元件之一向其相应的连接接触件施加电压时,源极接触件和漏极接触件在至少一个晶体管形成沟道时电连接。

3、优选地,至少一个晶体管是薄膜晶体管。还优选地,薄膜晶体管具有垂直沟道。还优选地,通孔可以是局部通孔或全局通孔。还优选地,有源通孔充当电路元件。

4、根据本发明的另一方面,提供了一种芯片,其包括多个区域,每个区域能够执行至少一个特定的电路功能,包括:控制策略电路;连接到每个相应区域的至少一个有源通孔,每个有源通孔可操作以向每个相应区域提供至少一个信号;并且其中,当不需要区域所执行的电路功能时,控制策略电路关闭向该区域供应至少一个信号的至少一个有源通孔,并且当需要区域所执行的电路功能时,控制策略电路开启向该区域供应至少一个信号的至少一个有源通孔。

5、优选地,至少一个信号包括对相应区域的供电。还优选地,有源通孔在后段制程(back end of line)工艺中形成。

6、根据本发明的另一方面,提供了一种芯片,包括:至少第一区域和第二区域的电路元件,每个区域实现电路功能;连接第一区域和第二区域的至少一个有源通孔;控制系统,用于在“on”和“off”状态之间更改有源通孔的状态。

7、本发明提供了一种新颖的有源通孔,其包括一个或多个通孔和薄膜晶体管开关元件。有源通孔可以用于1d、2.5d和/或3d芯片上,以:控制电路元件;减少或消除通孔(诸如相邻tsv)之间的emi;增加通孔密度;提高半导体电路的功率和热效率;简化芯片上的电力、数据和其它路由网络;实现更高级别的芯片或层堆叠,同时维持模块化。此外,通过使用所公开的薄膜晶体管,本发明的有源通孔可以利用后段制程工艺或前段制程(front end ofline)工艺来制造。

技术特征:

1.一种用于芯片的有源通孔,所述有源通孔包括:

2.如权利要求1所述的有源通孔,其中所述至少一个晶体管是具有垂直沟道的薄膜晶体管。

3.如权利要求2所述的有源通孔,其中所述薄膜晶体管包括半导体层和将所述源极接触件电连接到半导体层的源极沟道界面构件,所述源极沟道界面构件创建互补过量相反电荷的储存库以当所述第一电路元件、第二电路元件或第三电路元件之一不向其相应连接的接触件施加电压时,基本上最小化在半导体层中形成的沟道。

4.如权利要求2所述的有源通孔,其中所述薄膜晶体管包括半导体层和源极,当所述第一电路元件、第二电路元件或第三电路元件之一不向其相应连接的接触件施加电压时,所述源极最小化在半导体层中形成的沟道。

5.如权利要求1所述的有源通孔,包括至少两个晶体管。

6.如权利要求5所述的有源通孔,其中所述至少两个晶体管被构造处于公共漏极构造中。

7.如权利要求5所述的有源通孔,其中所述至少两个晶体管被构造处于公共源极构造中。

8.如权利要求5所述的有源通孔,其中所述至少两个晶体管处于级联构造中。

9.如权利要求1、2、3、4、5、6、7或8中的任一项所述的有源通孔,其中所述通孔是局部通孔、全局通孔或穿硅通孔之一。

10.如权利要求1、2、3、4、5、6、7或8中的任一项所述的有源通孔,其中所述至少一个晶体管在后段制程工艺中形成。

11.如权利要求1、2、3、4、5、6、7或8中的任一项所述的有源通孔,其中所述至少一个晶体管具有放大穿过所述通孔的信号的增益。

12.一种芯片,包括多个区域,每个区域能够执行至少一个特定电路功能,包括:

13.根据权利要求12所述的芯片,其中所述至少一个信号包括对相应区域的电力供应。

14.根据权利要求12或13所述的芯片,其中所述有源通孔包括局部通孔、全局通孔或穿硅通孔之一。

15.根据权利要求12或13所述的芯片,其中所述有源通孔在后段制程工艺中形成。

16.根据权利要求12所述的芯片,其中所述控制策略包括输入/输出管理。

17.一种芯片,包括:

18.根据权利要求17所述的芯片,其中所述有源通孔的状态被更改以静电隔离所述第一区域和第二区域。

19.根据权利要求17所述的芯片,其中当所述至少一个有源通孔处于on状态时,所述第一区域从所述至少一个有源通孔接收输入信号,该信号被所述至少一个有源通孔放大到所选择的水平,并且还包括与所述第一区域相邻的第二区域以及第二有源通孔,当所述第二有源通孔处于on状态时,所述第二区域从所述第二有源通孔接收输入信号,该信号被所述第二有源通孔放大到所选择的水平,所述第一区域和第二区域中的每一个的电路元件对低于所选择的水平的输入信号不响应,使得从第一区域接收到的输入信号在第二区域处的任何串扰低于所选择的水平。

技术总结

教导了一种有源通孔,其包括至少一个通孔和至少一个充当开关元件的晶体管。由此产生的有源通孔可以与1D、2.5D或3D芯片一起使用,以:控制电路元件;降低通孔之间的EMI;增加通孔的密度;提高芯片的功率和热效率;简化芯片上的电力、数据和其它路由网络;实现芯片中更高级别的管芯或层的堆叠,同时维持模块化;等等。可以提供控制策略系统,以在芯片的一个或多个区域不使用时取消对这些区域的电力供应,并在这些区域使用时向这些区域供应电力,或者控制对芯片的区域的输入和输出。有源通孔可以通过后段制程或前段制程工艺来制造。

技术研发人员:D·W·巴拉格,L·G·肖特

受保护的技术使用者:任耐特公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!