pn结二极管的制作方法

本发明涉及pn结二极管。

背景技术:

1、以往,已知由包括ga2o3系单晶的n型半导体层与包括nio的p型半导体层层叠而成的pn结二极管(参照专利文献1)。由于p型的ga2o3的形成是困难的,因此,在专利文献1所记载的pn结二极管中,p型半导体层的材料使用的是能够形成ga2o3系单晶异质pn结的nio单晶。

2、另外,专利文献1公开了一种沟槽型结势垒肖特基(jbs)二极管,其具备:包括ga2o3系单晶的n型半导体层,其具有沟槽;以及包括nio的p型半导体层,其埋入于n型半导体层的沟槽内。一般来说,肖特基势垒二极管与pn结二极管相比能够减小正向特性中的开启电压,但存在如下问题:有可能产生由肖特基接合界面的隧道现象引起的漏电流。在专利文献1的jbs二极管中,通过n型半导体层与沟槽内的p型半导体层的pn结来抑制由肖特基接合界面的隧道现象引起的漏电流,兼顾了低开启电压的实现与漏电流的抑制。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2019-36593号公报

技术实现思路

1、发明要解决的问题

2、然而,专利文献1所记载的jbs二极管由于具有在沟槽内埋入有p型半导体层的复杂结构,因此,其制造需要复杂的工序。

3、本发明的目的在于,提供即使在采取简单的结构的情况下也能够兼顾低开启电压的实现与漏电流的抑制的pn结二极管。

4、用于解决问题的方案

5、为了达到上述目的,本发明的一方面提供下述[1]~[4]的pn结二极管。

6、[1]一种pn结二极管,具备:n型半导体层,其包括具有(gaxalyin1-x-y)2o3(0<x≤1,0≤y<1,0<x+y≤1)的组成的n型半导体的单晶;以及p型半导体层,其与所述n型半导体层形成pn结,包括p型半导体,所述p型半导体是cu2o、nio、ag2o、ge、sixge1-x(0<x<1)、cuino2、cugao2、cualo2、cualxgayin1-x-yo2(0<x≤1,0≤y<1,0<x+y≤1)或者cuo,所述pn结二极管的开启电压为1.2v以下。

7、[2]一种pn结二极管,具备:n型半导体层,其包括具有(gaxalyin1-x-y)2o3(0<x≤1,0≤y<1,0<x+y≤1)的组成的n型半导体的单晶;以及p型半导体层,其与所述n型半导体层形成pn结,包括p型半导体,所述p型半导体是多晶si或者非晶si,所述pn结二极管的开启电压为1.2v以下。

8、[3]一种pn结二极管,具备:n型半导体层,其包括具有(gaxalyin1-x-y)2o3(0<x≤1,0≤y<1,0<x+y≤1)的组成的n型半导体的单晶;以及p型半导体层,其与所述n型半导体层形成pn结,包括p型半导体,所述p型半导体是单晶si,所述pn结二极管的开启电压为1.2v以下。

9、[4]根据上述[1]~[3]中的任意一项所述的pn结二极管,其中,所述p型半导体的电子亲和力χp和功函数以及所述n型半导体的电子亲和力χn和功函数满足由式表示的条件。

10、发明效果

11、根据本发明,能够提供即使在采取简单的结构的情况下也能够兼顾低开启电压的实现与漏电流的抑制的pn结二极管。

技术特征:

1.一种pn结二极管,其特征在于,具备:

2.一种pn结二极管,其特征在于,具备:

3.一种pn结二极管,其特征在于,具备:

4.根据权利要求1至3中的任意一项所述的pn结二极管,其中,

技术总结

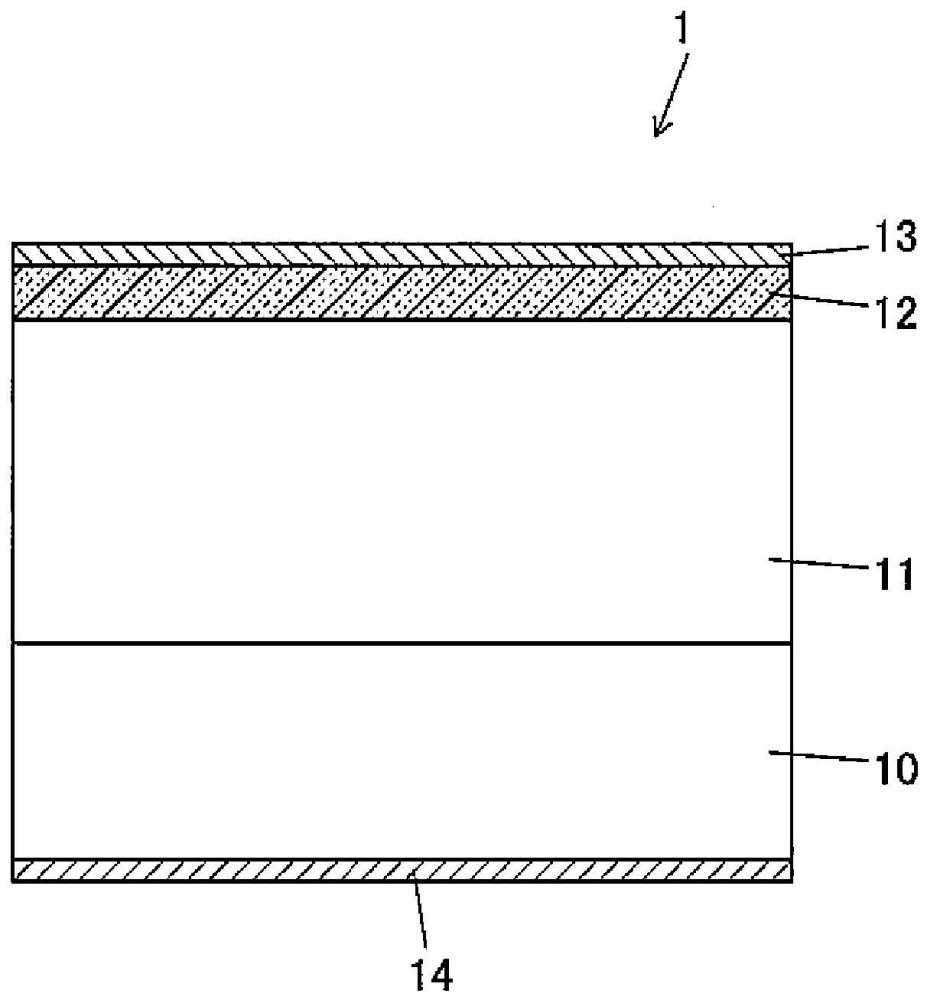

提供即使在采取简单的结构的情况下也能够兼顾低开启电压的实现与漏电流的抑制的pn结二极管。作为一实施方式,提供pn结二极管(1),具备:n型半导体层(11),其包括具有(Ga<subgt;x</subgt;Al<subgt;y</subgt;In<subgt;1‑x‑y</subgt;)<subgt;2</subgt;O<subgt;3</subgt;(0<x≤1,0≤y<1,0<x+y≤1)的组成的n型半导体的单晶;以及p型半导体层(12),其与n型半导体层(11)形成pn结,包括p型半导体,p型半导体是Cu<subgt;2</subgt;O、NiO、Ag<subgt;2</subgt;O、Ge、Si<subgt;x</subgt;Ge<subgt;1‑x</subgt;(0<x<1)、CuInO<subgt;2</subgt;、CuGaO<subgt;2</subgt;、CuAlO<subgt;2</subgt;、CuAl<subgt;x</subgt;Ga<subgt;y</subgt;In<subgt;1‑x‑y</subgt;O<subgt;2</subgt;(0<x≤1、0≤y<1、0<x+y≤1)或者CuO,pn结二极管(1)的开启电压为1.2V以下。

技术研发人员:高冢章夫,佐佐木公平

受保护的技术使用者:株式会社田村制作所

技术研发日:

技术公布日:2024/5/8

- 还没有人留言评论。精彩留言会获得点赞!