半导体封装结构及其制造方法与流程

一般地,本发明涉及半导体封装结构。更具体地,本发明涉及一种具有以小于其宽度的间隔而堆叠的晶粒的iii族氮化物基半导体封装结构。

背景技术:

1、近年来,对高电子迁移率晶体管(hemt)的研究越来越盛行,特别是对于高功率开关和高频应用。iii族氮化物基hemt利用具有不同带隙的两种材料之间的异质结界面以形成量子阱状结构,其容纳二维电子气(2deg)区域,以满足高功率/频率器件的需求。除了hemt之外,具有异质结构的器件的例子还包括异质结双极晶体管(hbt),异质结场效应晶体管(hfet)和调制掺杂fet(modfet)。

技术实现思路

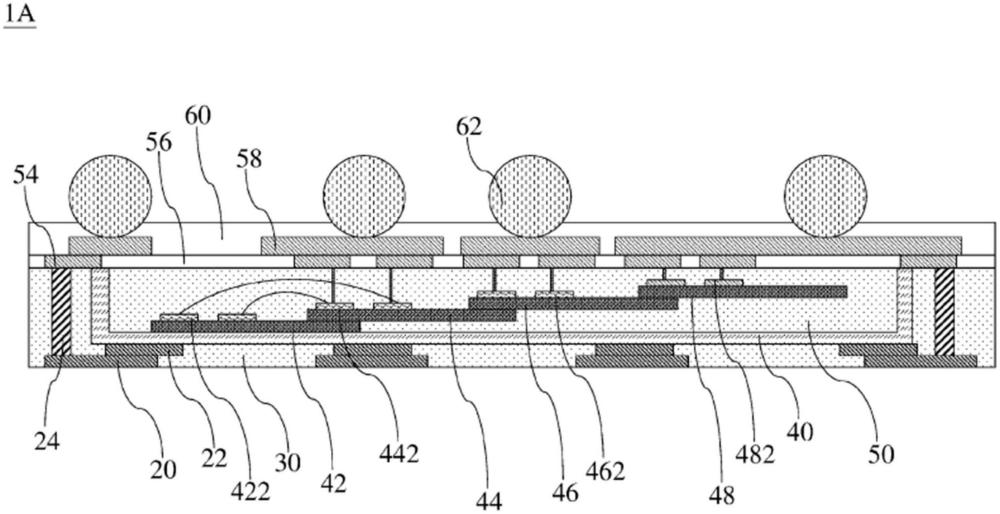

1、在一个方面,本发明提供了一种氮化物基半导体器件。该半导体封装器件包括晶粒载体,第一晶粒,第二晶粒,第三晶粒,第一导电柱和第二导电柱。晶粒载体限定空腔。第一晶粒设置在空腔中。第二晶粒设置在空腔中并位于第一晶粒上。第一晶粒包括第一焊盘和焊线。第二晶粒包括经由焊线与第一焊盘电连接的第二焊盘。第三晶粒设置在空腔中并位于第二晶粒上,并且包括第三焊盘。第一导电柱设置在第二焊盘上。第二导电柱设置在第三焊盘上。

2、在另一个方面,本发明提供了一种半导体器件的制造方法。该方法包括如下步骤:在载体晶片上设置载体衬底;在所述载体衬底中形成空腔;将第一晶粒设置在该空腔中;将第二晶粒设置在该空腔中并且位于该第一晶粒上;将第三晶粒设置在该空腔中并且位于该第二晶粒上;形成第一封装材料以填充所述空腔并封装所述第一晶粒,所述第二晶粒和所述第三晶粒;以及在所述第一晶粒,所述第二晶粒和所述第三晶粒上形成再分布层(rdl)。

3、在再一个方面,本发明提供了一种氮化物基半导体器件。半导体封装器件包括晶粒载体,第一晶粒和第二晶粒。晶粒载体限定空腔。第一晶粒设置在空腔中。第二晶粒设置在空腔中并位于第一晶粒上。第一晶粒包括第一焊盘和焊线。第二晶粒包括经由焊线与第一焊盘电连接的第二焊盘。第一晶粒和第二晶粒之间沿垂直方向上的重叠宽度小于第一晶粒的宽度。

4、通过上述构造,通过垂直堆叠和水平移位将晶粒封装在晶粒载体中,从而有利于改善封装尺寸灵活性。这样,两个相邻晶粒之间的重叠面积小于单个晶粒的宽度,从而减少用于连接的面积,进而减小翘曲。

技术特征:

1.一种半导体封装器件,包括:

2.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一晶粒与所述第二晶粒之间的接触界面是非导电的。

3.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第二晶粒与所述第三晶粒之间的接触界面是非导电的。

4.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述晶粒载体具有侧壁,且在所述第一晶粒,所述第二晶粒和所述第三晶粒中,所述第一晶粒最靠近所述侧壁。

5.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第二晶粒和所述第三晶粒与所述晶粒载体的底部分离。

6.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第二晶粒附接到所述第一晶粒的顶表面。

7.根据前述权利要求中任一权利要求所述的半导体封装器件,进一步包括设置在晶粒载体的空腔内并封装第一晶粒,第二晶粒和第三晶粒的第一封装材料。

8.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一封装材料填充所述晶粒载体的所述空腔。

9.根据前述权利要求中任一权利要求所述的半导体封装器件,其进一步包含围绕所述晶粒载体的第二封装材料。

10.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一导电柱和所述第二柱穿透所述第一封装材料且不被所述第一封装材料覆盖。

11.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第二晶粒和所述第三晶粒的底表面由所述第一封装材料覆盖。

12.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一晶粒与所述第二晶粒之间沿垂直方向上的重叠宽度小于所述第一晶粒的宽度。

13.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一焊盘与所述第二晶粒水平重叠。

14.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一导电柱与所述第二导电柱平行。

15.根据前述权利要求中任一权利要求所述的半导体封装器件,进一步包括设置在晶粒载体的空腔之外并与第一导电柱和第二导电柱平行的第三导电柱。

16.一种半导体器件的制造方法,包括:

17.根据前述权利要求中任一权利要求所述的制造方法,进一步包括在所述载体衬底中形成所述空腔之前形成封装所述载体衬底的第二封装材料。

18.根据前述权利要求中任一权利要求所述的制造方法,其中所述第一晶粒与所述第二晶粒之间沿垂直方向上的重叠宽度小于所述第一晶粒的宽度。

19.根据前述权利要求中任一权利要求所述的制造方法,其中所述第一晶粒与所述第二晶粒之间的接触界面是非导电的。

20.根据前述权利要求中任一权利要求所述的制造方法,其中所述载体衬底具有侧壁,且在所述第一晶粒,所述第二晶粒以及所述第三晶粒中,所述第一晶粒最靠近所述侧壁。

21.一种半导体封装器件,包括:

22.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第一晶粒与所述第二晶粒之间的接触界面是非导电的。

23.根据前述权利要求中任一权利要求所述的半导体封装器件,进一步包括设置在所述空腔中并位于所述第二晶粒上的第三晶粒。

24.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述第二晶粒与所述第三晶粒之间的接触界面是非导电的。

25.根据前述权利要求中任一权利要求所述的半导体封装器件,其中所述载体衬底具有侧壁,且在所述第一晶粒,所述第二晶粒以及所述第三晶粒中,所述第一晶粒最靠近所述侧壁。

技术总结

一种半导体封装器件,包括晶粒载体,第一晶粒,第二晶粒,第三晶粒,第一导电柱和第二导电柱。晶粒载体限定空腔。第一晶粒设置在空腔中。第二晶粒设置在空腔中并位于第一晶粒上。第一晶粒包括第一焊盘和焊线。第二晶粒包括经由焊线与第一焊盘电连接的第二焊盘。第三晶粒设置在空腔中并位于第二晶粒上,并且包括第三焊盘。第一导电柱设置在第二焊盘上。第二导电柱设置在第三焊盘上。

技术研发人员:许二岗,曹凯,张雷

受保护的技术使用者:英诺赛科(苏州)半导体有限公司

技术研发日:

技术公布日:2024/8/15

- 还没有人留言评论。精彩留言会获得点赞!