一种氮化镓器件及氮化镓器件的制作方法与流程

本申请实施例涉及通信技术与半导体制造领域,具体而言,涉及一种氮化镓器件及氮化镓器件的制作方法。

背景技术:

1、目前,学术界提升器件线性度特征的主要思路是从调制器件栅下的载流子速场关系,栅源电容等方面入手。具体的技术方案分别有:采用更厚的势垒层厚度、场板结构调制栅漏沟道电场、渐变铝组分势垒、采用金属-绝缘层-半导体(metal insulatorsemiconductor,简称为mis)结构、双沟道材料、三维鳍型结构的鳍式高电子迁移率晶体管(fin-high electric mobility transistor,简称为fin-hemt)以及基于阈值耦合作用的渐进凹槽栅结构等。但是,针对高频端的通讯系统,这些技术方案或多或少都有其致命缺陷。例如,更厚的势垒厚度会引入较强的漏致势垒降低效应,限制了器件在高频下的使用;场板结构在高频方案下容易引入过多寄生电容,限制器件的高频特性;渐变铝组分材料的生长难度巨大,很难实现大批量低成本生产;mis结构引入新的寄生,影响器件的稳定性;三维鳍型结构的fin-hemt是以牺牲器件输出能力,引入寄生电容,限制频率特性;渐进凹槽栅技术实现难度大,对于光刻和刻蚀技术要求过高难以大批量应用等。

2、针对相关技术中从调制器件栅下的载流子速场关系、栅源电容入手提升器件线性度特征,引入寄生电容限制频率特性、实现难度大、高,难以大批量应用的问题,尚未提出解决方案。

技术实现思路

1、本申请实施例提供了一种氮化镓器件及氮化镓器件的制作方法,以至少解决相关技术中从调制器件栅下的载流子速场关系、栅源电容入手提升器件线性度特征,引入寄生电容限制频率特性、实现难度大、高,难以大批量应用的问题。

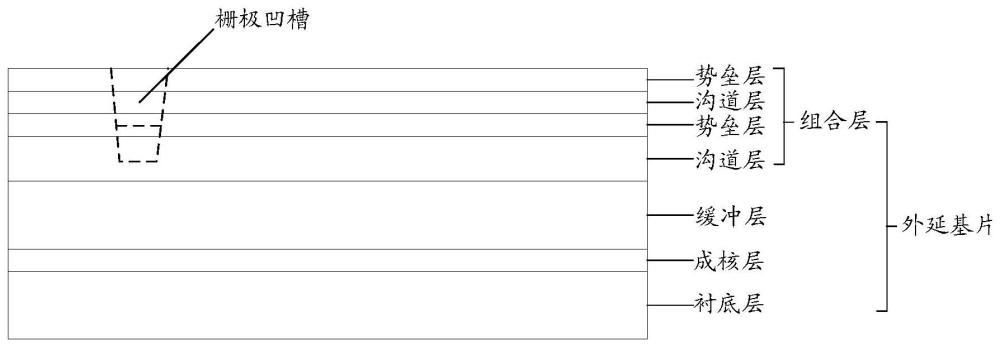

2、根据本申请的一个实施例,提供了一种氮化镓器件,所述氮化镓器件包括:外延基片,所述外延基片包括自下向上连接的衬底层、成核层、缓冲层、组合层,其中,所述组合层为至少两层,每层组合层包括自下向上连接的沟道层与势垒层,最上层的所述势垒层上设置有栅电极、源电极及漏电极;

3、所述栅电极的下方具有周期分布且相互间隔的不同深度的栅极凹槽,其中,所述栅极凹槽内填充有栅极金属,所述栅极金属用于部分耗尽所述栅极凹槽对应的所述组合层内所述势垒层与所述沟道层的连接面的二维电子气。

4、根据本申请的另一个实施例,还提供了一种氮化镓器件的制作方法,其特征在于,所述方法包括:

5、获取外延基片,其中,所述外延基片包括自下向上连接的衬底层、成核层、缓冲层、组合层,其中,所述组合层为至少两层,每层组合层包括自下向上连接的沟道层与势垒层;

6、在最上层的所述势垒层上光刻出栅电极的栅根、源电极及漏电极;

7、在所述栅电极的下方光刻出周期分布且相互间隔的不同深度的栅极凹槽,其中,所述栅极凹槽用于隔离所述栅极凹槽对应的所述组合层内所述势垒层与所述沟道层的连接面的二维电子气,形成纳米沟道;

8、在最上层的所述势垒层上光刻出栅电极的栅帽,并填充满栅极金属形成栅电极,填充到所述栅极凹槽内的栅极金属用于部分耗尽所述栅极凹槽对应的所述组合层内所述势垒层与所述沟道层的连接面的二维电子气;

9、在所述外延基片的表面进行钝化处理,以生成氮化硅薄膜。

10、通过本申请实施例的氮化镓器件,包括:外延基片,所述外延基片包括自下向上连接的衬底层、成核层、缓冲层、组合层,其中,所述组合层为至少两层,每层组合层包括自下向上连接的沟道层与势垒层,最上层的所述势垒层上设置有栅电极、源电极及漏电极;所述栅电极的下方具有周期分布且相互间隔的不同深度的栅极凹槽,所述栅极凹槽内填充有栅极金属,所述栅极金属用于部分耗尽所述栅极凹槽对应的所述组合层内所述势垒层与所述沟道层的连接面的二维电子气,可以解决相关技术中从调制器件栅下的载流子速场关系、栅源电容入手提升器件线性度特征,引入寄生电容限制频率特性、实现难度大、高,难以大批量应用的问题,实现多个不同导电沟道(沟道层与势垒层的连接面)之间的分层复用,在减小源极电阻在大源漏电流下的增长趋势对器件线性度的影响,同时,减小栅漏反向漏电,提升器件的击穿性能,实现更优的器件开关特性,引入寄生小、实现难度小、易于大规模应用。

技术特征:

1.一种氮化镓器件,其特征在于,所述氮化镓器件包括:外延基片,所述外延基片包括自下向上连接的衬底层、成核层、缓冲层、组合层,其中,所述组合层为至少两层,每层组合层包括自下向上连接的沟道层与势垒层,最上层的所述势垒层上设置有栅电极、源电极及漏电极;

2.根据权利要求1所述的氮化镓器件,其特征在于,

3.根据权利要求2所述的氮化镓器件,其特征在于,

4.根据权利要求1至3中任一项所述的氮化镓器件,其特征在于,

5.一种氮化镓器件的制作方法,其特征在于,所述方法包括:

6.根据权利要求5所述的方法,其特征在于,在所述获取外延基片之后,所述方法还包括:

7.根据权利要求6所述的方法,其特征在于,所述在最上层的所述势垒层上制备出源电极与漏电极包括:

8.根据权利要求7所述的方法,其特征在于,在采用溅射或电子束蒸发工艺在所述源电极图形与所述漏电极图形区域淀积欧姆金属,以形成所述源电极和所述漏电极之后,所述方法还包括:

9.根据权利要求7所述的方法,其特征在于,在最上层的所述势垒层上光刻出栅电极的栅根包括:

10.根据权利要求5所述的方法,其特征在于,在所述栅电极的下方光刻出周期分布且相互间隔的不同深度的栅极凹槽包括:

11.根据权利要求10所述的方法,其特征在于,在所述栅电极的下方光刻出周期分布且相互间隔的不同深度的栅极凹槽之后,所述方法还包括:

12.根据权利要求5至11中任一项所述的方法,其特征在于,在最上层的所述栅极凹槽上方光刻出栅电极的栅帽包括:

技术总结

本申请实施例提供了一种氮化镓器件及氮化镓器件的制作方法,该氮化镓器件包括:外延基片,外延基片包括自下向上连接的衬底层、成核层、缓冲层、组合层,组合层为至少两层,每层组合层包括自下向上连接的沟道层与势垒层,最上层的势垒层上设置有栅电极、源电极及漏电极;栅电极的下方具有周期分布且相互间隔的不同深度的栅极凹槽,栅极凹槽内填充有栅极金属,栅极金属用于部分耗尽栅极凹槽对应的组合层内势垒层与沟道层的连接面的二维电子气,可以解决相关技术中从调制器件栅下的载流子速场关系、栅源电容入手提升器件线性度特征,引入寄生电容限制频率特性、实现难度大、高,难以大批量应用的问题,引入寄生小、实现难度小、易于大规模应用。

技术研发人员:武盛,代云飞,李文明,刘海军,张煜

受保护的技术使用者:中兴通讯股份有限公司

技术研发日:

技术公布日:2024/7/9

- 还没有人留言评论。精彩留言会获得点赞!