集成芯片结构和形成集成芯片结构的方法与流程

本发明的实施例涉及集成芯片结构和形成集成芯片结构的方法。

背景技术:

1、多维集成芯片是具有多个衬底和/或管芯的集成电路,这些衬底和/或管芯垂直堆叠在彼此上并且彼此电互连。通过电互连堆叠的衬底和/或管芯,多维集成芯片充当单个器件,与传统集成芯片相比,它提供了改进的性能、降低的功耗和减少的占用面积。因此,多维集成芯片为继续满足下一代集成电路的性能/成本需求提供了途径。

技术实现思路

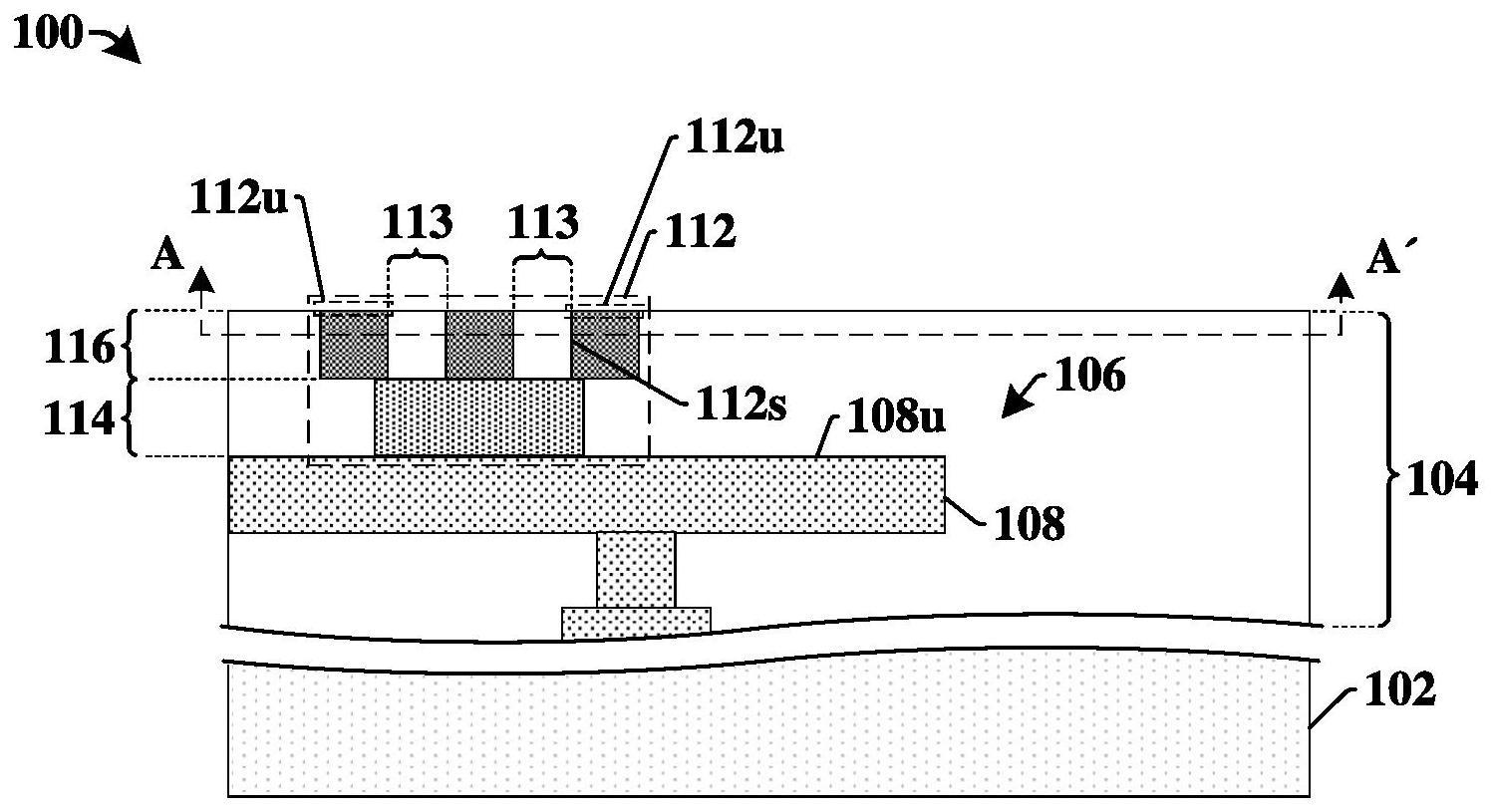

1、本发明的一些实施例提供了一种集成芯片结构,包括:一个或多个互连件,设置在衬底上方的介电结构内;接合焊盘,具有沿着所述介电结构的顶表面布置的顶表面,其中,如在截面图中所观察的,所述接合焊盘的所述顶表面包括彼此横向分隔开一个或多个非零距离的多个离散的顶表面段,所述一个或多个非零距离在所述接合焊盘的内侧壁之间延伸;以及其中,所述介电结构直接设置在所述接合焊盘的所述内侧壁之间。

2、本发明的另一些实施例提供了一种集成芯片结构,包括:一个或多个互连件,由设置在衬底上的介电结构围绕;接合焊盘,由所述介电结构围绕,并且所述接合焊盘包括在沿着所述接合焊盘的底部布置的下部侧壁的外边缘之间延伸的下部段,以及在沿着所述接合焊盘的顶部布置的上部侧壁的外边缘之间延伸的上部段;以及其中,所述接合焊盘的所述上部段包括在所述接合焊盘的顶表面的边缘之间的间隔开非零距离的一个或多个内侧壁,所述介电结构位于所述接合焊盘的所述顶表面的所述边缘之间。

3、本发明的又一些实施例提供了一种形成集成芯片结构的方法,包括:在形成在下部介电结构上方的第一上部介电结构内形成第一接合焊盘开口,所述下部介电结构围绕衬底上方的一个或多个互连件;在所述第一接合焊盘开口内形成第一阻挡层和第一导电芯;在所述第一上部介电结构上方形成第二上部介电结构;在所述第二上部介电结构内形成第二接合焊盘开口以暴露所述第一导电芯并且以围绕所述第二上部介电结构的一个或多个内侧壁;在所述第二接合焊盘开口内形成阻挡材料和导电材料;以及去除所述阻挡材料和所述导电材料的部分,其中,去除所述阻挡材料和所述导电材料的所述部分形成具有内侧壁的接合焊盘,所述接合焊盘的所述内侧壁形成延伸进入所述接合焊盘的一个或多个空腔。

4、本发明的再一些实施例提供了堆叠晶圆结构中的开槽的接合焊盘。

技术特征:

1.一种集成芯片结构,包括:

2.根据权利要求1所述的集成芯片结构,其中,所述接合焊盘的底表面横向且连续地延伸超过所述接合焊盘的所述内侧壁中的一个或多个。

3.根据权利要求1所述的集成芯片结构,其中,所述接合焊盘的所述顶表面与所述介电结构的所述顶表面基本上共面。

4.根据权利要求1所述的集成芯片结构,其中,所述一个或多个互连件包括设置在所述介电结构内的最顶部互连件,所述最顶部互连件具有上表面,所述最顶部互连件的所述上表面直接接触所述接合焊盘的底表面并且连续地延伸超过所述接合焊盘的所述底表面的最外侧壁。

5.根据权利要求1所述的集成芯片结构,其中,所述一个或多个互连件包括设置在所述介电结构内的最顶部互连件,位于所述接合焊盘的所述内侧壁之间的所述介电结构从所述介电结构的所述顶表面连续地延伸到所述最顶部互连件。

6.根据权利要求1所述的集成芯片结构,其中,所述接合焊盘包括:

7.根据权利要求6所述的集成芯片结构,其中,所述上部段的所述下表面物理接触所述下部段的所述上表面。

8.根据权利要求6所述的集成芯片结构,其中,所述接合焊盘的所述内侧壁布置在所述上部段内并且耦接至所述上部段的所述下表面正上方的水平延伸表面。

9.一种集成芯片结构,包括:

10.一种形成集成芯片结构的方法,包括:

技术总结

本发明涉及集成芯片结构。集成芯片结构包括设置在衬底上方的介电结构内的一个或多个互连件。接合焊盘具有沿着所述介电结构的顶表面布置的顶表面。其中,如在截面图中所观察的,接合焊盘的顶表面包括彼此横向分隔开非零距离的多个离散的顶表面段,该非零距离在接合焊盘的内侧壁之间延伸。介电结构直接设置在接合焊盘的内侧壁之间。本发明的实施例还提供了形成集成芯片结构的方法。

技术研发人员:庄学理,邓立峯,吴伟成

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!