衬底处理方法、半导体器件的制造方法、记录介质及衬底处理装置与流程

本公开文本涉及衬底处理方法、半导体器件的制造方法、记录介质及衬底处理装置。

背景技术:

1、作为具有三维结构的3dnand型闪存、dram的字线,例如使用低电阻的金属膜。另外,有时在该金属膜与绝缘膜之间形成阻挡膜(例如参见专利文献1及专利文献2)。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2011-252221号公报

5、专利文献2:日本特开2017-069407号公报

技术实现思路

1、发明所要解决的课题

2、本公开文本提供能够提高形成于衬底上的膜的膜质的技术。

3、用于解决课题的手段

4、根据本公开文本的一个方式,提供一种技术,其进行下述工序:

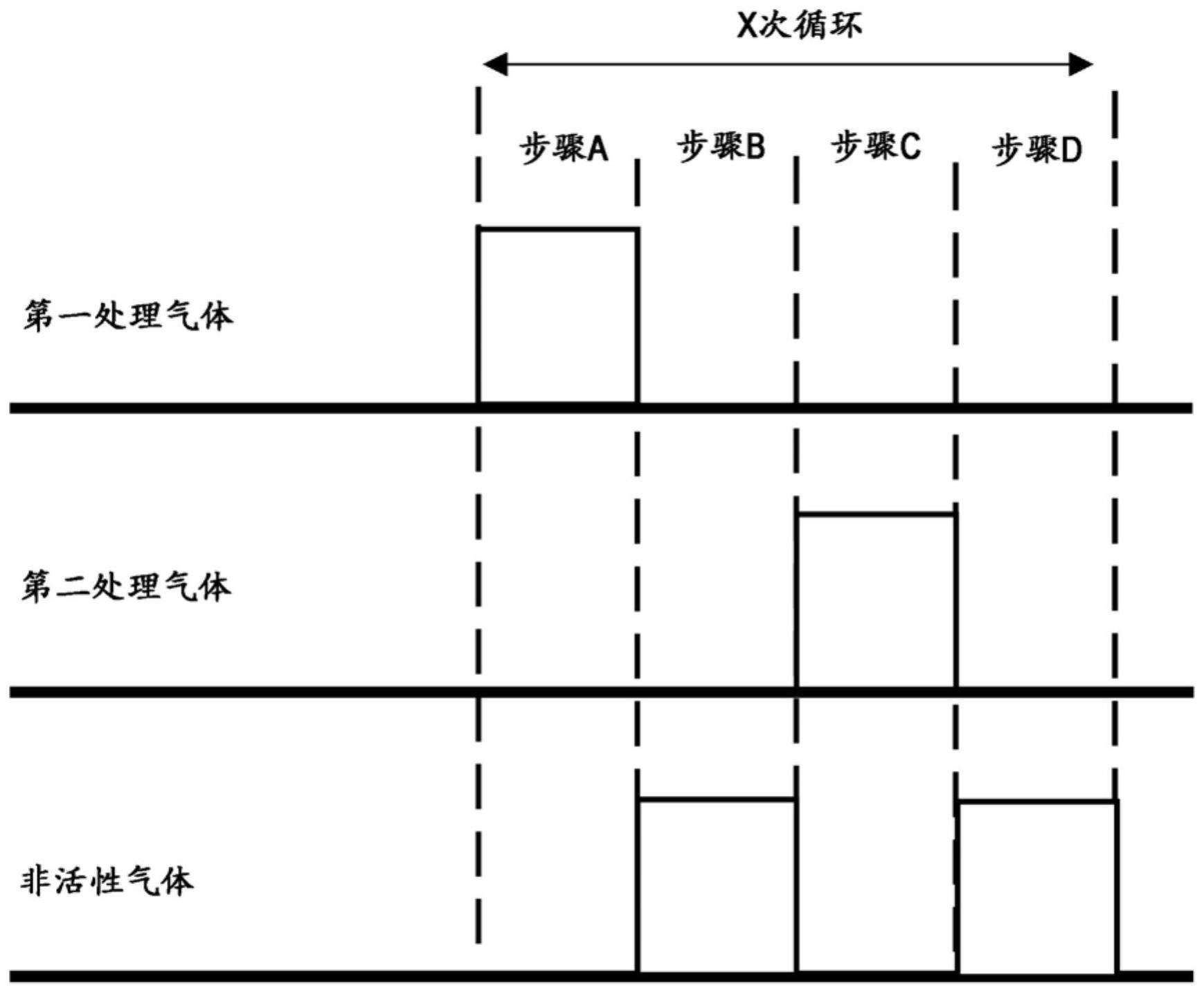

5、(a)向衬底供给包含第一元素和卤素的第一处理气体的工序;(b)向衬底供给具有n-n键和n-h键的第二处理气体的工序;和(c)在将衬底加热至250℃以下的温度的状态下,将(a)与(b)进行x(x为自然数)次,形成包含第一元素的第一膜的工序。

6、发明效果

7、根据本公开文本,能够提高形成于衬底上的膜的膜质。

技术特征:

1.衬底处理方法,其具有:

2.如权利要求1所述的衬底处理方法,其中,(c)于180℃以上、220℃以下的温度进行。

3.如权利要求1所述的衬底处理方法,其具有:

4.如权利要求2所述的衬底处理方法,其具有:

5.如权利要求1所述的衬底处理方法,其具有(f)在(c)之后,于比(c)的温度高的温度对所述衬底进行热处理的工序。

6.如权利要求2所述的衬底处理方法,其具有(f)在(c)之后,于比(c)的温度高的温度对所述衬底进行热处理的工序。

7.如权利要求3所述的衬底处理方法,其具有(f)在(c)之后,于比(c)的温度高的温度对所述衬底进行热处理的工序。

8.如权利要求1所述的衬底处理方法,其中,(f)中,具有在(c)之后于比(c)的温度高的温度对所述衬底进行热处理的工序,在向该高的温度升温的期间向所述衬底供给具有所述n-h键、且组成与所述第二处理气体不同的第三处理气体。

9.如权利要求2所述的衬底处理方法,其中,

10.如权利要求3所述的衬底处理方法,其中,

11.如权利要求1所述的衬底处理方法,其中,(b)中,供给具有所述n-h键、且组成与所述第二处理气体不同的第三处理气体。

12.如权利要求1所述的衬底处理方法,其中,(b)中,供给具有所述n-h键、且组成与所述第二处理气体不同的第三处理气体。

13.如权利要求1所述的衬底处理方法,其具有(g)在(a)的期间和(a)之后中的至少一者以上的工序中,供给包含与所述第一元素不同的第二元素的第四处理气体的工序。

14.如权利要求1所述的衬底处理方法,其具有(h)在(c)之后供给包含与所述第一元素不同的第二元素的第四处理气体,从而在所述第一膜之上形成包含所述第二元素的膜的工序。

15.如权利要求1所述的衬底处理方法,其中,(i)在(c)之前进行(b)。

16.半导体器件的制造方法,其具有:

17.计算机可读取的记录介质,其记录有利用计算机使衬底处理装置执行下述步骤的程序:

18.衬底处理装置,其具有:

技术总结

本公开文本涉及衬底处理方法、半导体器件的制造方法、记录介质及衬底处理装置。能够提高形成于衬底上的膜的膜质。其具有:(a)向衬底供给包含第一元素和卤素的第一处理气体的工序;(b)向衬底供给具有N‑N键和N‑H键的第二处理气体的工序;(c)在将衬底加热至250℃以下的温度的状态下,将(a)与(b)进行X(X为自然数)次,形成包含第一元素的第一膜的工序。

技术研发人员:清野笃郎,小川有人

受保护的技术使用者:株式会社国际电气

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!