具有三个不同材料部的沟槽隔离和包括此沟槽隔离的LDMOSFET的制作方法

背景技术:

1、本公开涉及集成电路结构,更具体地涉及包括具有三个不同材料部的沟槽隔离的ic结构和晶体管。

技术实现思路

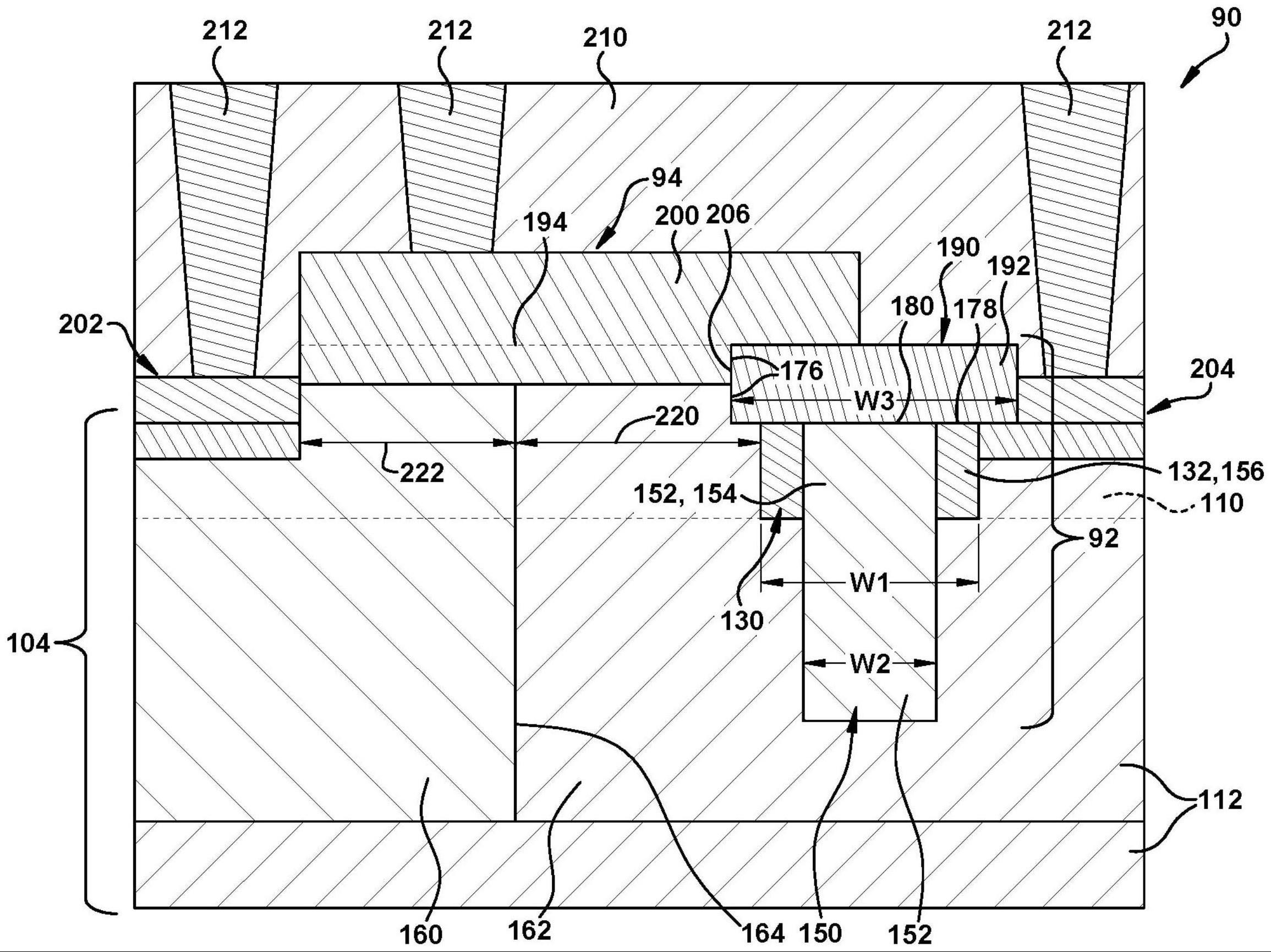

1、本公开的一方面涉及一种集成电路(ic)结构,包括:位于衬底中的沟槽隔离(ti),所述ti包括:下部,其包括第一电介质材料并具有第一宽度;中部,其包括所述第一电介质材料和外部第二电介质材料;以及上部,其包括第三电介质材料并具有大于所述第一宽度的第二宽度,其中所述第一电介质材料、所述第二电介质材料和所述第三电介质材料是不同的。

2、本公开的另一方面涉及一种晶体管,包括:位于半导体衬底中的第一源极/漏极区和位于所述半导体衬底中的第二源极/漏极区;位于所述半导体衬底中的沟槽隔离(ti),所述ti将所述第一源极/漏极区和所述第二源极/漏极区分隔开,所述ti更靠近所述第一源极/漏极区和所述第二源极/漏极区中的一者,所述ti包括:下部,其包括第一电介质材料并具有第一宽度;中部,其包括所述第一电介质材料和外部第二电介质材料,以及上部,其包括第三电介质材料并具有大于所述第一宽度的第二宽度;以及位于所述半导体衬底上方的栅电极,所述栅电极与所述ti的所述上部重叠。

3、本公开的另一方面涉及一种方法,包括:通过以下方式形成沟槽隔离(ti):在半导体衬底中形成一对间隔开的第一沟槽;通过用第一电介质材料填充所述一对间隔开的第一沟槽来形成所述ti的中部,从而形成一对间隔开的ti段;穿过所述一对间隔开的ti段之间的所述半导体衬底的剩余部分并穿过所述一对间隔开的ti段中的每一个ti段的内部在所述半导体衬底中形成第二沟槽;通过用第二电介质材料填充所述第二沟槽来形成所述ti的下部;在所述ti的所述中部的上段、所述ti的所述下部和邻近所述ti的所述中部的所述半导体衬底中形成第三沟槽;以及通过用第三电介质材料填充所述第三沟槽来形成所述ti的上部,其中所述第一电介质材料、所述第二电介质材料和所述第三电介质材料是不同的。

4、通过下面对本公开的实施例的更具体的描述,本公开的上述和其他特征将变得显而易见。

技术特征:

1.一种集成电路ic结构,包括:

2.根据权利要求1所述的ic结构,其中,所述外部第二电介质材料具有在尺寸上介于所述第一宽度和所述第二宽度之间的第三宽度。

3.根据权利要求1所述的ic结构,其中,所述第三电介质材料位于所述第一电介质材料和所述第二电介质材料上。

4.根据权利要求1所述的ic结构,还包括位于所述衬底上方的栅电极,所述栅电极与所述沟槽隔离的所述上部重叠,并且与所述沟槽隔离的所述上部的所述第三电介质材料的侧壁相邻。

5.根据权利要求4所述的ic结构,还包括位于所述衬底中的第一源极/漏极区和第二源极/漏极区,并且其中,所述ti和所述栅电极位于所述第一源极/漏极区和所述第二源极/漏极区之间。

6.根据权利要求5所述的ic结构,其中,所述第一源极/漏极区位于所述衬底中的第一阱中,并且所述第二源极/漏极区位于与所述第一阱相邻的所述衬底中的第二阱中。

7.根据权利要求6所述的ic结构,其中,所述ti位于所述第二阱中,并且所述第一阱和所述第二阱在所述栅电极下方限定结。

8.根据权利要求1所述的ic结构,其中,所述衬底包括位于基底半导体层上方的半导体鳍,并且所述ti部分地位于所述半导体鳍中。

9.根据权利要求8所述的ic结构,其中,所述ti的所述下部延伸到所述基底半导体层中。

10.一种晶体管,包括:

11.根据权利要求10所述的晶体管,其中,所述外部第二电介质材料具有在尺寸上介于所述第一宽度和所述第二宽度之间的第三宽度。

12.根据权利要求10所述的晶体管,其中,所述第三电介质材料接触所述第一电介质材料和所述第二电介质材料,并且所述第三电介质材料具有与所述半导体衬底的上表面共面的上表面。

13.根据权利要求10所述的晶体管,其中,所述栅电极与所述ti的所述第三电介质材料的侧壁相邻。

14.根据权利要求10所述的晶体管,其中,所述ti和所述栅电极位于所述第一源极/漏极区和所述第二源极/漏极区之间。

15.根据权利要求10所述的晶体管,其中,所述第一源极/漏极区位于所述半导体衬底中的第一阱中,并且所述第二源极/漏极区位于与所述第一阱相邻的所述半导体衬底中的第二阱中,其中,所述第一阱和所述第二阱在所述栅电极下方限定结,并且所述沟槽隔离位于所述第二阱中。

16.根据权利要求10所述的晶体管,其中,所述半导体衬底包括位于基底半导体层上方的半导体鳍,并且所述下部延伸到所述基底半导体层中。

17.一种方法,包括:

18.根据权利要求17所述的方法,其中,所述ti的所述下部具有第一宽度,所述ti的所述中部具有第二宽度,并且所述ti的所述上部具有第三宽度,其中,所述第一宽度、所述第二宽度和所述第三宽度是不同的。

19.根据权利要求17所述的方法,其中,所述ti的所述上部接触所述ti的所述中部和所述ti的所述下部。

20.根据权利要求17所述的方法,还包括:

技术总结

本公开涉及具有三个不同材料部的沟槽隔离和包括此沟槽隔离的LDMOS FET。一种IC结构,其包括位于衬底中并具有三个不同电介质材料部的沟槽隔离(TI)。这些材料部也可以具有不同的宽度。TI可以包括:下部,其包括第一电介质材料并具有第一宽度;中部,其包括第一电介质材料和外部第二电介质材料;以及上部,其包括第三电介质材料并具有大于第一宽度的第二宽度。第一、第二和第三电介质材料是不同的。

技术研发人员:刘荣庭,谷曼,J·B·约翰逊,郑望,贾加尔·辛格,王海艇

受保护的技术使用者:格芯(美国)集成电路科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!