晶圆接受测试方法与流程

本申请涉及半导体器件测试,具体涉及一种晶圆接受测试方法。

背景技术:

1、wat测试(wafer acceptance test,晶圆接受测试)在probe wafer后通过施加电流或电压信号来监测工艺稳定性。传统意义上,电性测试装置(wat tester)在针对干扰噪声方面普遍采用将测试过程中的干扰噪声通过测试装置的外壳物理引流至外部远端接地,以此来抑制噪声。

2、但在部分测试应用上这种方式却无法完全抑制干扰,无法完全消除噪声,主要表现在小电流测试上易受噪声干扰而导致测试数据偏移,stddev(标准偏差)偏大。就测试机型而论,串行测试机所测漏电稳定在pa级别,而并行测试机所测数据在~e-11a等级左右波动,稳定性较差,受到噪声干扰。此时传统意义上所使用外部远端接地的方式在并行测试机上不足以去完全屏蔽噪声的干扰。

技术实现思路

1、本申请提供了一种晶圆接受测试方法,可以解决wat测试的小电流测试中,并行测试受到噪声干扰、无法完全屏蔽噪声信号干扰导致测试数据稳定性较差等问题中的至少一个问题。

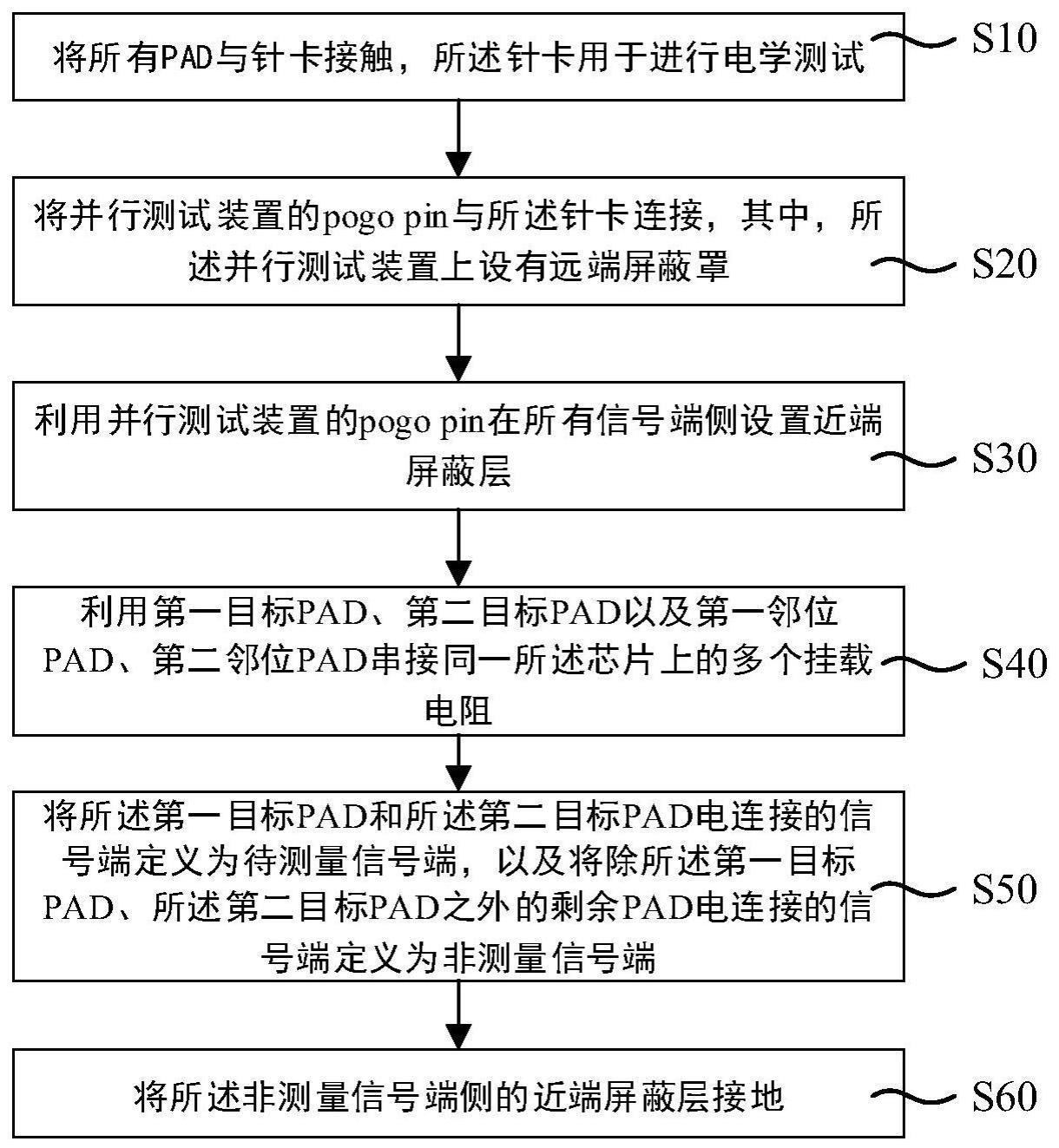

2、一方面,本申请实施例提供了一种晶圆接受测试方法,待测晶圆包括:多个相同的芯片和多个pad,各所述芯片均具有至少两个信号端,各所述信号端对应地与各所述pad电连接,所述晶圆接受测试方法包括:

3、将所有pad与针卡接触,所述针卡用于进行电学测试;

4、将并行测试装置的pogo pin与所述针卡连接,其中,所述并行测试装置上设有远端屏蔽罩;

5、利用并行测试装置的pogo pin在所有信号端侧设置近端屏蔽层;

6、利用第一目标pad、第二目标pad以及第一邻位pad、第二邻位pad串接同一所述芯片上的多个挂载电阻,其中,所述第一邻位pad位于所述第一目标pad侧,所述第二邻位pad位于所述第二目标pad侧;

7、将所述第一目标pad和所述第二目标pad电连接的信号端定义为待测量信号端,以及将除所述第一目标pad、所述第二目标pad之外的剩余pad电连接的信号端定义为非测量信号端;

8、将所述非测量信号端侧的近端屏蔽层接地;

9、在所述第一目标pad、所述第二目标pad之间施加偏置电压,以获取所述待测量信号端之间的电流。

10、可选的,在所述晶圆接受测试方法中,利用第一目标pad、第二目标pad以及第一邻位pad、第二邻位pad串接同一所述芯片上的多个挂载电阻的步骤包括:

11、在所述第一邻位pad和所述第一目标pad之间串接第一挂载电阻;

12、在所述第一邻位pad和所述第二目标pad之间串接第二挂载电阻;

13、在所述第一邻位pad和所述第二邻位pad之间串接第三挂载电阻。

14、可选的,在所述晶圆接受测试方法中,所述第一挂载电阻的阻值小于所述第二挂载电阻的阻值,所述第二挂载电阻的阻值小于所述第三挂载电阻的阻值。

15、可选的,在所述晶圆接受测试方法中,在将并行测试装置的pogo pin与所述针卡连接之后,以及在将除所述第一目标pad、所述第二目标pad之外的剩余pad电连接的信号端侧的近端屏蔽层接地之前,所述晶圆接受测试方法还包括:

16、将所述远端屏蔽罩接地。

17、可选的,在所述晶圆接受测试方法中,所有的所述近端屏蔽层相互独立。

18、可选的,在所述晶圆接受测试方法中,所述第一目标pad和所述第二目标pad为所有pad中的任意两个pad。

19、可选的,在所述晶圆接受测试方法中,所述在所述第一目标pad、所述第二目标pad之间施加偏置电压,以获取所述待测量信号端之间的电流之后,所述晶圆接受测试方法还包括:

20、切断所述非测量信号端侧的近端屏蔽层与地端的连接。

21、本申请技术方案,至少包括如下优点:

22、本申请通过利用pogo pin在所有信号端侧设置近端屏蔽层;然后在第一目标pad、第二目标pad以及第一邻位pad、第二邻位pad之间接上挂载电阻;接着将非测量信号端侧的近端屏蔽层接地,最后在第一目标pad、第二目标pad之间施加偏置电压,以获取待测量信号端之间的电流,这样可以将所有非测量信号端在与晶圆接触后形成的噪声及时引至并行测试装置内部的地端,从而避免产生回路噪声,消除了非测量信号端带来的噪声干扰,提高了小电流测试中待测量信号端的测试数据(微小电流)的稳定性,并且能够及时监测器件是否存在漏电风险。

23、进一步的,本申请利用pogo pin在所有信号端侧设置近端屏蔽层,并将非测量信号端侧的近端屏蔽层接地,同时也将并行测试装置上的远端屏蔽罩接地,这样可以对干扰噪声起到双重屏蔽的效果,进一步提高了小电流测试中待测量信号端的测试数据(微小电流)的稳定性。

技术特征:

1.一种晶圆接受测试方法,待测晶圆包括:多个相同的芯片和多个pad,各所述芯片均具有至少两个信号端,各所述信号端对应地与各所述pad电连接,其特征在于,所述晶圆接受测试方法包括:

2.根据权利要求1所述的晶圆接受测试方法,其特征在于,利用第一目标pad、第二目标pad以及第一邻位pad、第二邻位pad串接同一所述芯片上的多个挂载电阻的步骤包括:

3.根据权利要求2所述的晶圆接受测试方法,其特征在于,所述第一挂载电阻的阻值小于所述第二挂载电阻的阻值,所述第二挂载电阻的阻值小于所述第三挂载电阻的阻值。

4.根据权利要求1所述的晶圆接受测试方法,其特征在于,在将并行测试装置的pogopin与所述针卡连接之后,以及在将除所述第一目标pad、所述第二目标pad之外的剩余pad电连接的信号端侧的近端屏蔽层接地之前,所述晶圆接受测试方法还包括:

5.根据权利要求1所述的晶圆接受测试方法,其特征在于,所有的所述近端屏蔽层相互独立。

6.根据权利要求1所述的晶圆接受测试方法,其特征在于,所述第一目标pad和所述第二目标pad为所有pad中的任意两个pad。

7.根据权利要求1所述的晶圆接受测试方法,其特征在于,所述在所述第一目标pad、所述第二目标pad之间施加偏置电压,以获取所述待测量信号端之间的电流之后,所述晶圆接受测试方法还包括:

技术总结

本发明提供一种晶圆接受测试方法,包括:在所有PAD上放置针卡;将并行测试装置的pogo pin与针卡连接;利用pogo pin在所有信号端侧设置近端屏蔽层;在第一目标PAD、第二目标PAD以及第一邻位PAD、第二邻位PAD之间接上挂载电阻;定义待测量信号端、非测量信号端;将非测量信号端侧的近端屏蔽层接地;在第一目标PAD、第二目标PAD之间施加偏置电压,以获取待测量信号端之间的电流。本申请通过在所有信号端侧设置近端屏蔽层,并将非测量信号端侧的近端屏蔽层接地,可以将非测量信号端在与晶圆接触后形成的噪声及时引导至并行测试装置的内部地端,从而避免产生回路噪声,提高了小电流测试中测试数据的稳定性。

技术研发人员:陈俊池,于亚男,孟文艳,韩斌

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!