半导体存储器装置的制作方法

各种示例实施例涉及半导体存储器装置,并且更具体地,涉及包括竖直沟道晶体管的半导体存储器装置和/或制造半导体存储器装置的方法。

背景技术:

1、随着半导体装置的设计规则已经被减少,制造技术已经被开发以提高半导体装置的集成密度、操作速度和/或产量。因此,具有竖直沟道的晶体管已经被提出,以增大晶体管的集成密度、电阻和/或电流驱动能力。

技术实现思路

1、各种示例实施例可提供能够提高电特性和/或集成密度的半导体存储器装置。

2、根据一些示例实施例,一种半导体存储器装置可包括:位线;沟道图案,包括位线上的水平沟道部分;竖直沟道部分,从水平沟道部分竖直突出;字线,在水平沟道部分上,并且在竖直沟道部分的侧壁上;以及栅极绝缘图案,在字线与沟道图案之间。沟道图案可包括氧化物半导体,并且可包括顺序堆叠的第一沟道层、第二沟道层和第三沟道层。第一沟道层至第三沟道层可包括第一金属,并且第二沟道层还可包括与第一金属不同的第二金属。第一沟道层的至少一部分可与位线接触。

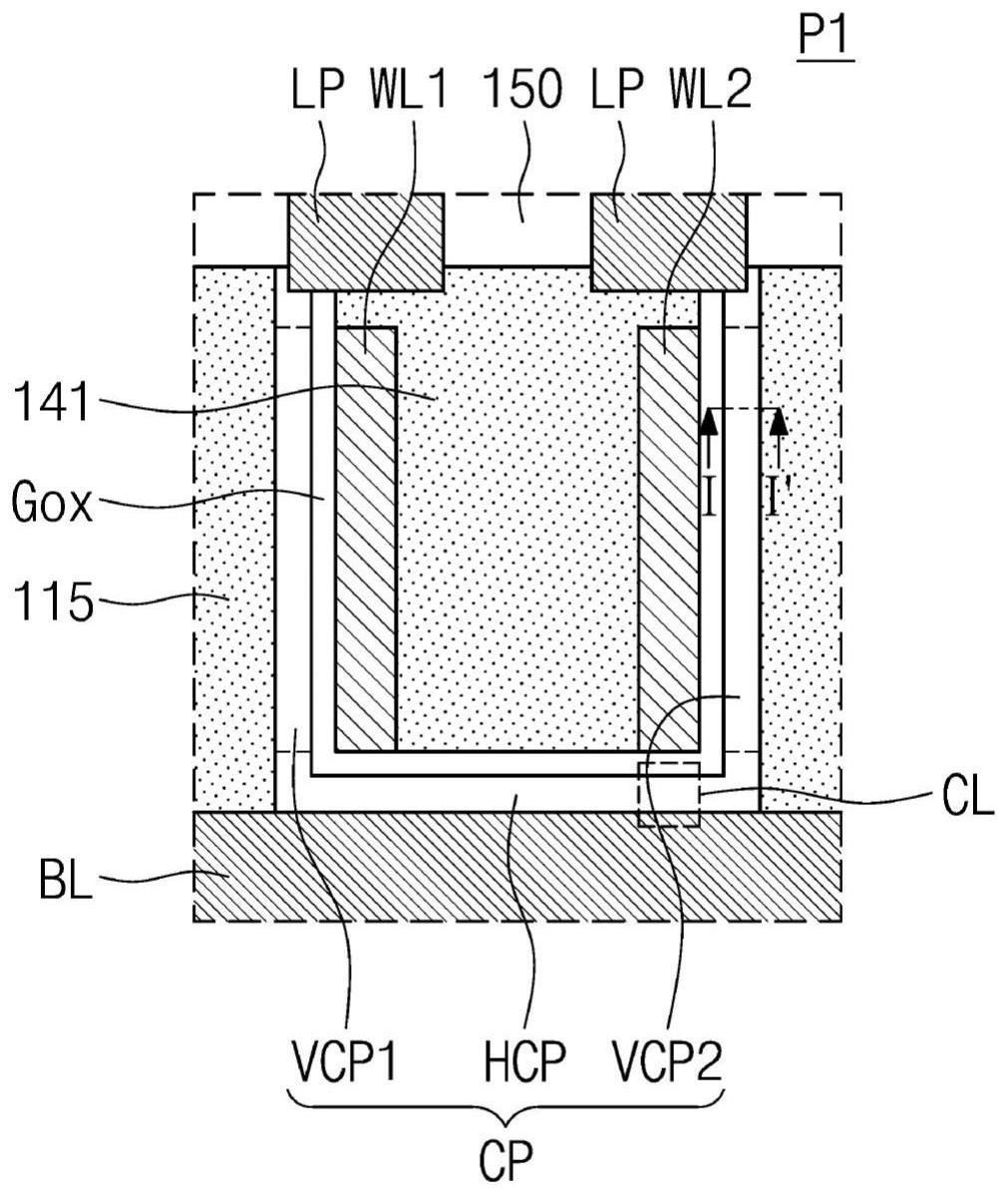

3、根据一些示例实施例,一种半导体存储器装置可包括:位线;沟道图案,包括位线上的水平沟道部分、以及从水平沟道部分竖直突出并且彼此面对的第一竖直沟道部分和第二竖直沟道部分;第一字线和第二字线,在水平沟道部分上,并且在第一竖直沟道部分与第二竖直沟道部分之间;栅极绝缘图案,在沟道图案与第一字线和第二字线之间;以及绝缘图案,在第一字线与第二字线之间。沟道图案可包括氧化物半导体,并且可包括顺序堆叠的第一沟道层、第二沟道层和第三沟道层。第一沟道层至第三沟道层可包括第一金属,并且第二沟道层还可包括与第一金属不同的第二金属。第一沟道层的至少一部分可与位线接触。

4、根据一些示例实施例,一种半导体存储器装置可包括:外围电路结构,包括半导体基底上的外围电路和覆盖外围电路的下绝缘层;位线,在外围电路结构上在第一方向上延伸;第一绝缘图案,限定在第二方向上延伸的沟槽以与位线相交;沟道图案,在沟槽中在第二方向上彼此间隔开,其中,每个沟道图案包括彼此面对的第一竖直沟道部分和第二竖直沟道部分、以及连接第一竖直沟道部分和第二竖直沟道部分的水平沟道部分;第一字线和第二字线,在沟道图案的水平沟道部分上在第二方向上延伸,第一字线与沟道图案的第一竖直沟道部分邻近,并且第二字线与沟道图案的第二竖直沟道部分邻近;栅极绝缘图案,在沟道图案与第一字线和第二字线之间,并且在第二方向上延伸;第二绝缘图案,覆盖沟槽中的第一字线和第二字线;第一数据存储图案,在沟道图案的第一竖直沟道部分上;以及第二数据存储图案,设置在沟道图案的第二竖直沟道部分上。每个沟道图案可包括氧化物半导体,并且可包括顺序堆叠的第一沟道层、第二沟道层和第三沟道层。第一沟道层至第三沟道层可包括第一金属,并且第二沟道层还可包括与第一金属不同的第二金属。第一沟道层的至少一部分可接触位线。

技术特征:

1.一种半导体存储器装置,包括:

2.根据权利要求1所述的半导体存储器装置,其中,第三沟道层接触栅极绝缘图案。

3.根据权利要求1所述的半导体存储器装置,其中,

4.根据权利要求1所述的半导体存储器装置,其中,

5.根据权利要求1所述的半导体存储器装置,其中,第一沟道层和第三沟道层中的每个中的第一金属的组分比大于第二沟道层中的第一金属的组分比。

6.根据权利要求1所述的半导体存储器装置,其中,

7.根据权利要求6所述的半导体存储器装置,还包括:

8.根据权利要求1所述的半导体存储器装置,其中,

9.根据权利要求1所述的半导体存储器装置,其中,字线的顶表面位于比沟道图案的竖直沟道部分的顶表面低的水平处。

10.根据权利要求1至权利要求9中的任一项所述的半导体存储器装置,还包括:

11.一种半导体存储器装置,包括:

12.根据权利要求11所述的半导体存储器装置,其中,第三沟道层接触栅极绝缘图案。

13.根据权利要求11所述的半导体存储器装置,其中,

14.根据权利要求11所述的半导体存储器装置,其中,

15.根据权利要求11所述的半导体存储器装置,其中,第一字线包括第一水平部分和第一竖直部分,并且第二字线包括第二水平部分和第二竖直部分,其中,第一水平部分和第二水平部分在沟道图案的水平沟道部分上,并且第一竖直部分和第二竖直部分分别位于沟道图案的第一竖直沟道部分和第二竖直沟道部分的侧壁上,并且

16.根据权利要求15所述的半导体存储器装置,还包括:

17.根据权利要求11所述的半导体存储器装置,其中,

18.根据权利要求11至权利要求17中的任一项所述的半导体存储器装置,其中,

19.一种半导体存储器装置,包括:

20.根据权利要求19所述的半导体存储器装置,还包括:

技术总结

提供了半导体存储器装置。所述半导体存储器装置包括:位线;沟道图案,包括位线上的水平沟道部分和从水平沟道部分竖直突出的竖直沟道部分;字线,在水平沟道部分上,并且在竖直沟道部分的侧壁上;以及栅极绝缘图案,在字线与沟道图案之间。沟道图案包括氧化物半导体,并且包括顺序堆叠的第一沟道层、第二沟道层和第三沟道层。第一沟道层至第三沟道层包括第一金属,并且第二沟道层还包括与第一金属不同的第二金属。第一沟道层的至少一部分接触位线。

技术研发人员:金台原,金俞琳,李昇嬉,张胜愚,卓容奭

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!