半导体装置的形成方法与流程

本公开实施例关于半导体制造技术,特别关于半导体装置及其形成方法。

背景技术:

1、以鳍片为主的晶体管,例如鳍式场效晶体管(fin field effect transistors,finfets)和纳米结构晶体管(例如纳米线晶体管、纳米片晶体管、全绕式栅极(gate-all-around,gaa)晶体管、多桥通道晶体管、纳米带晶体管)是三维结构,其包含在半导体基底之上延伸的鳍片(或其一部分)中的通道区作为三维结构。被配置为控制通道区内的电荷载子的流动的栅极结构包覆环绕半导体材料的鳍片。作为范例,在鳍式场效晶体管中,栅极结构包覆环绕鳍片的三个侧面(以及因此通道区),借此能够增加对通道区的控制(以及因此鳍式场效晶体管的开关)。作为另一范例,在纳米结构晶体管中,栅极结构包覆环绕鳍片结构中的多个通道区,使得栅极结构环绕多个通道区中的每一个。源极/漏极区(例如外延区)位于栅极结构的两侧。

技术实现思路

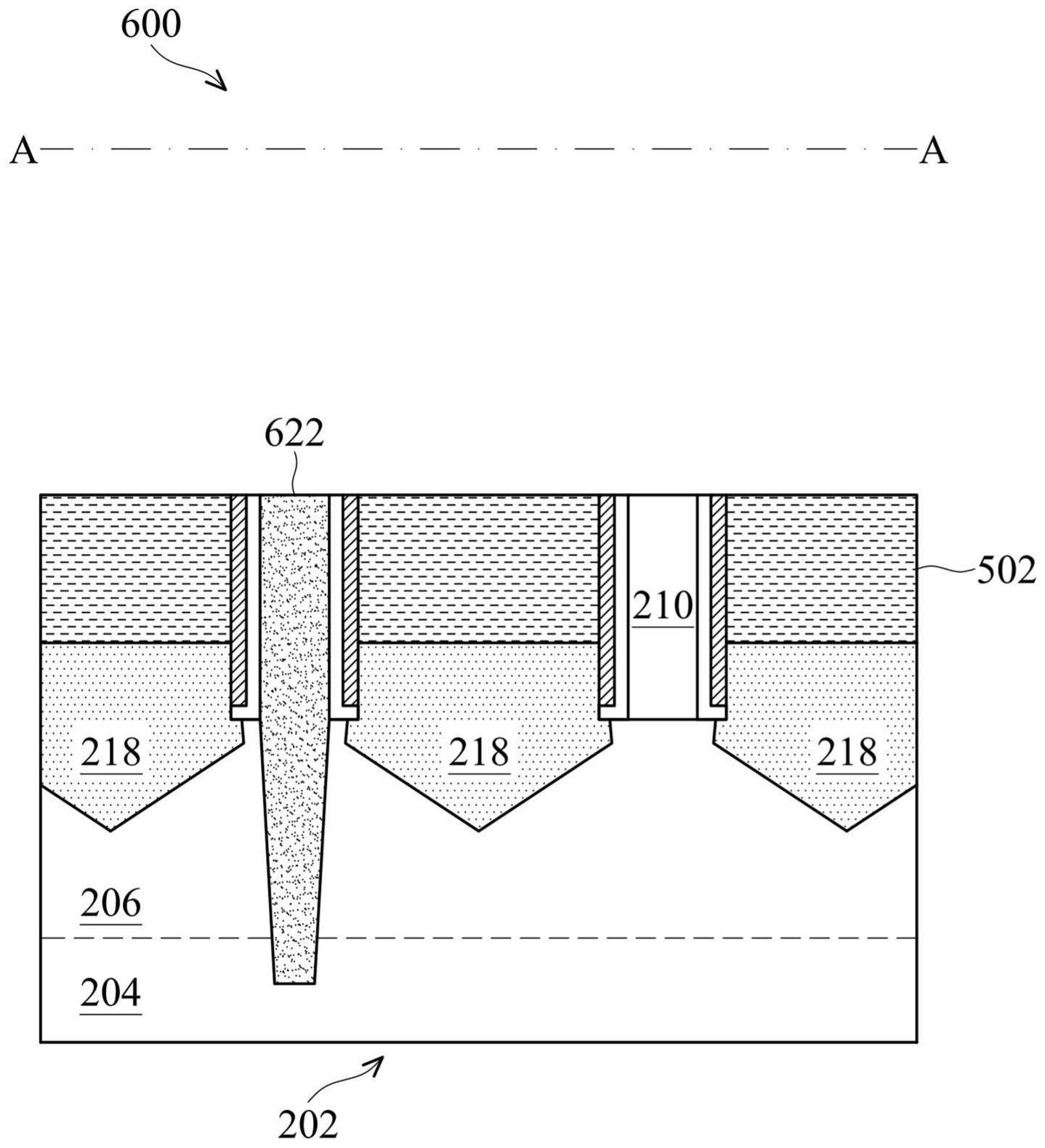

1、根据一些实施例提供半导体装置的形成方法。此方法包含在半导体装置的虚设栅极结构的一部分中形成凹槽至第一深度并使用第一蚀刻技术;在虚设栅极结构的所述部分中形成凹槽至第二深度并使用第二蚀刻技术;以及在形成凹槽至第二深度之后,在凹槽中形成氧化物界定边缘上连续多晶硅(cpode)结构。

2、根据另一些实施例提供半导体装置的形成方法。此方法包含在半导体装置的多晶硅栅极结构的一部分中形成第一凹槽至第一深度并使用以等向性等离子体为主的蚀刻技术;在多晶硅栅极结构的所述部分中形成第一凹槽至第二深度并使用以非等向性等离子体为主的蚀刻技术;经由第一凹槽并在形成第一凹槽至第二深度之后,在半导体装置的鳍片结构的一部分中及鳍片结构下方的基底的一部分中形成第二凹槽;以及用绝缘材料填充第一凹槽和第二凹槽。

3、根据又一些实施例提供半导体装置的形成方法。此方法包含在半导体装置的虚设栅极结构的一部分上方的硬遮罩层中形成图案;基于硬遮罩层中的图案将虚设栅极结构的所述部分蚀刻至第一深度并使用等向性蚀刻技术,以在虚设栅极结构的所述部分中形成凹槽;使用非等向性蚀刻技术蚀刻虚设栅极结构的所述部分,以将凹槽从第一深度增加至第二深度;在将凹槽增加至第二深度之后,蚀刻半导体装置的鳍片结构的一部分和鳍片结构下方的基底的一部分,以将凹槽的一部分从第二深度增加至第三深度;以及在将凹槽的所述部分增加至第三深度之后,在凹槽中形成氧化物界定边缘上连续多晶硅(cpode)结构。

技术特征:

1.一种半导体装置的形成方法,包括:

2.如权利要求1所述的半导体装置的形成方法,其中该第一蚀刻技术包括等向性蚀刻技术;以及

3.如权利要求2所述的半导体装置的形成方法,其中该虚设栅极结构的该部分邻近该半导体装置的至少一层间介电层;以及

4.如权利要求1所述的半导体装置的形成方法,更包括:

5.如权利要求1所述的半导体装置的形成方法,其中该第一蚀刻技术包括不使用偏压的第一以等离子体为主的技术;以及

6.如权利要求1所述的半导体装置的形成方法,其中一第一蚀刻操作的一第一持续时间小于一第二蚀刻操作的一第二持续时间,该第一蚀刻技术在该第一蚀刻操作中用于在该虚设栅极结构的该部分中形成该凹槽至该第一深度,该第二蚀刻技术在该第二蚀刻操作中用于在该虚设栅极结构的该部分中形成该凹槽至该第二深度。

7.如权利要求1所述的半导体装置的形成方法,其中使用该第一蚀刻技术移除的该虚设栅极结构的该部分的厚度大于使用该第二蚀刻技术移除的该虚设栅极结构的该部分的厚度。

8.一种半导体装置的形成方法,包括:

9.如权利要求8所述的半导体装置的形成方法,其中该第二凹槽在该第二凹槽的顶部的宽度大于在该第二凹槽的底部的宽度。

10.一种半导体装置的形成方法,包括:

技术总结

提供半导体装置的形成方法。两步骤蚀刻技术用于氧化物界定边缘上连续多晶硅(CPODE)凹蚀制程,以形成其中要形成CPODE结构的凹槽。两步骤制程包含使用等向性蚀刻技术进行第一蚀刻操作,其中虚设栅极结构中的凹槽形成至第一深度。使用非等向性蚀刻技术进行第二蚀刻操作以将凹槽形成至第二深度。使用非等向性蚀刻技术造成第二蚀刻操作中虚设栅极结构的高度定向(例如垂直)蚀刻。在虚设栅极结构的底部或其附近由非等向性蚀刻技术提供的高度定向蚀刻减少、最小化及/或防止蚀刻到层间介电(ILD)层的相邻部分及/或在层间介电层的所述部分下方的源极/漏极区中。

技术研发人员:林耿纬,游家齐,倪俊龙,谢瑞夫

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!