水平环绕式栅极元件纳米线气隙间隔的形成的制作方法

本公开内容的实施方式大体上关于堆叠的hgaa元件。

背景技术:

1、可靠地生产次半微米(sub-half micron)及更小的特征是半导体元件的下一代超大型集成电路(very large scale integration,vlsi)和特大型集成电路(ultra large-scale integration,ulsi)的一项关键技术挑战。然而,随着电路技术的极限的推进,vlsi及ulsi技术的持续缩小的尺寸已对处理能力有额外的要求。在基板上可靠地形成栅极结构对vlsi及ulsi的成功而言是重要的,且对持续致力增加电路密度及个别基板与裸片(die)的品质而言也是重要的。

2、随着下一代的元件的电路密度的增加,互连件(诸如过孔、沟槽、触点、栅极结构及其它特征)的宽度以及这些部件之间的介电材料的宽度减少到25nm及20nm的尺寸及更小,然而介电层的厚度维持实质上恒定,结果增加特征的深宽比。再者,减少的通道长度经常引发现有平面mosfet架构中的显著短通道效应。为了实现下一代元件及结构的制造,三维(3d)元件结构经常用于改善晶体管的性能。尤其,鳍式场效应晶体管(finfet)经常用于增强元件性能。finfet元件一般包括具高深宽比的半导体鳍片,其中用于晶体管的通道及源极/漏极区域形成在所述半导体鳍片上。随后利用增加的通道及源极/漏极区域表面积的优点而在所述鳍片元件的一部分的侧面上且沿着所述侧面形成栅极电极,从而生产快速、更可靠、更好控制的半导体晶体管元件。finfet的进一步优点包括减少短通道效应及提供更高的电流。有水平环绕式栅极(horizontal gate-all-around,hgaa)构造的元件结构经常通过环绕的栅极提供卓越的静电控制,从而抑制短通道效应及相关的漏电流。

3、一些应用中,hgaa结构用于下一代半导体元件应用。hgaa元件结构包括数个晶格匹配通道(例如纳米线),这些晶格匹配通道悬挂在堆叠构造中且通过源极/漏极区域连接。

4、在hgaa结构中,经常利用不同的材料形成通道结构(例如纳米线),所述通道结构可能会不期望地增加将所有这些材料整合于纳米线结构中且不恶化元件性能的制造困难度。例如,与hgaa结构相关的一项挑战包括金属栅极与源极/漏极之间存在大寄生电容。此类寄生电容的不适当管理可能造成相当劣化的元件性能。

5、因此,需要制造hgaa元件的改善结构与方法。

技术实现思路

1、本公开内容提供一种使用期望材料形成用于半导体晶片的水平环绕式栅极(hgaa)结构的纳米线结构的结构与方法。

2、一个实施方式中,公开一种处理基板的方法。所述方法包括,将介电材料沉积在堆叠的第一侧及所述堆叠的第二侧的每一个上。所述堆叠包括重复多对的第一层与第二层。所述堆叠的所述第一侧与所述堆叠的所述第二侧相对,且所述第一侧与所述第二侧的每一个包括一个或多个凹部。所述方法也包括,从所述堆叠的所述第一侧及所述堆叠的所述第二侧移除所述介电材料。所述介电材料保留在所述第一侧与所述第二侧的所述一个或多个凹部中。所述方法也包括,沉积应力源(stressor)层并形成一个或多个间隙,所述应力源层邻近所述第一侧与所述第二侧,并且所述间隙位于所述应力源层与所述堆叠的所述第一侧之间及所述应力源层与所述堆叠的所述第二侧之间。

3、另一实施方式中,公开另一种处理基板的方法。所述方法包括,在处理腔室中将堆叠沉积于所述基板上。所述堆叠包括重复多对的第一层与第二层。所述方法也包括,从所述堆叠移除材料,以在所述堆叠的第一侧及所述堆叠的与所述第一侧相对的第二侧的每一个上产生一个或多个凹部。所述方法也包括,将介电材料沉积在所述堆叠的所述第一侧上、所述堆叠的所述第二侧上,及所述一个或多个凹部内。所述方法也包括,从所述第一侧及所述第二侧的每一个移除所述介电材料。所述介电材料保留在所述一个或多个凹部中。所述方法也包括,沉积应力源(stressor)层并形成一个或多个间隙,所述应力源层邻近所述第一侧及所述第二侧,所述间隙位于所述应力源层与所述堆叠的所述第一侧之间及所述应力源层与所述堆叠的所述第二侧之间。

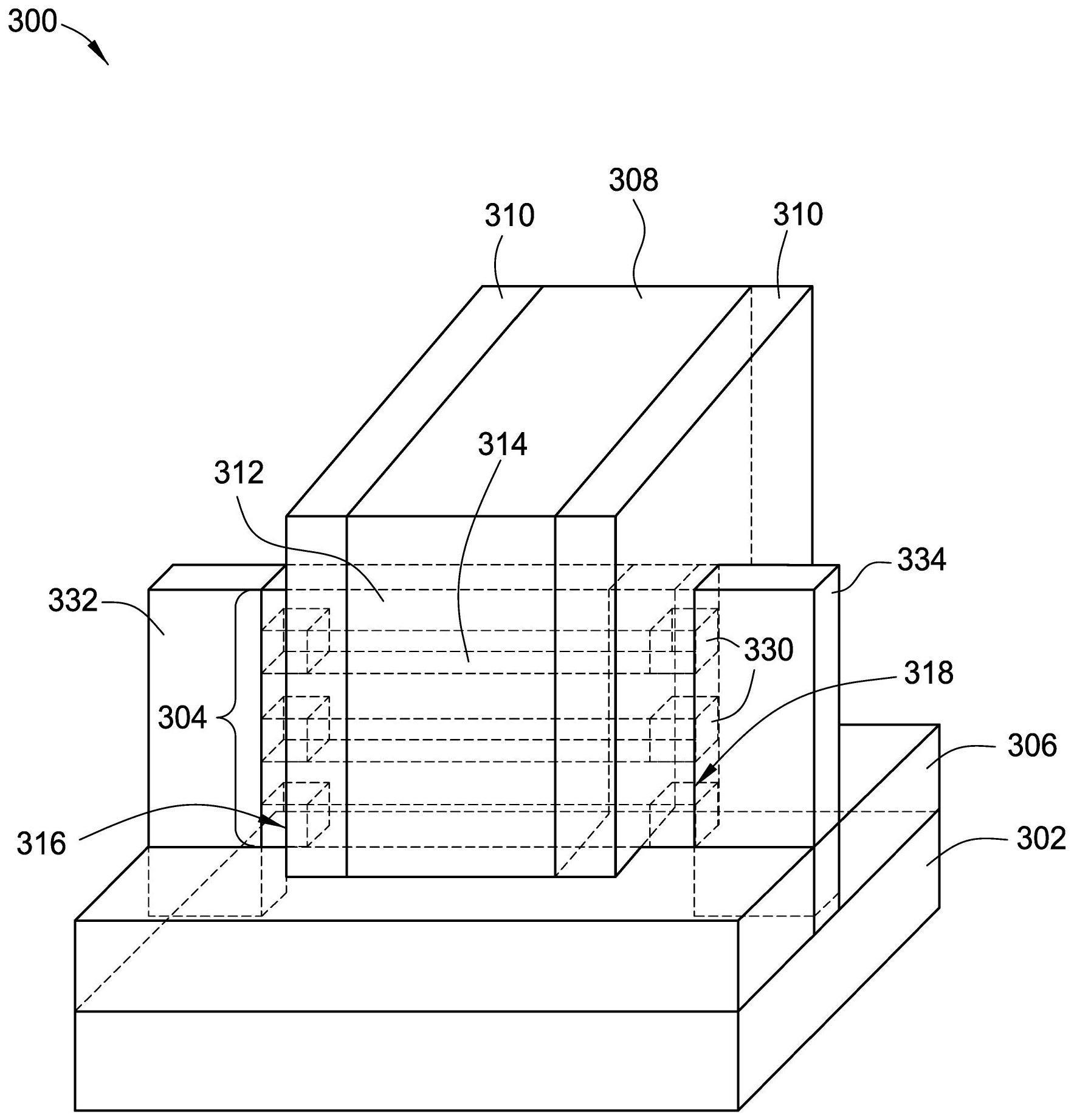

4、尚有另一实施方式中,公开一种纳米线结构。所述纳米线结构包括具有重复多对的第一层与第二层的堆叠。所述堆叠包括第一侧,所述第一侧与第二侧相对。所述纳米线结构也包括:环绕所述堆叠的栅极结构、邻近所述堆叠的第一侧的源极层、与所述源极层相对且邻近所述堆叠的所述第二侧的漏极层、设置在所述源极层与所述第二层之间的一个或多个间隙、以及设置在所述漏极层与所述第二层之间的一个或多个间隙。

技术特征:

1.一种纳米线结构,包括:

2.根据权利要求1所述的纳米线结构,其中所述间隙的每一者含有下述的至少一者:氢、氧、氩、氮、氦、或上述物质的混合物。

3.根据权利要求1所述的纳米线结构,其中所述第一层的每一者是硅层,且所述第二层的每一者是sige层。

4.根据权利要求1所述的纳米线结构,其中所述堆叠包括至少重复四对的所述第一层和所述第二层。

5.根据权利要求2所述的纳米线结构,其中所述间隙的每一者含有氧、氮、以及氢、氦中的至少一者、或上述物质的混合物。

6.根据权利要求1所述的纳米线结构,其中所述间隙的每一者的介电常数的值约为1。

7.根据权利要求1所述的纳米线结构,其中所述介电材料包含氮化硅、氧化硅、氮氧化硅、碳氧化硅、氮碳化硅、氮碳氧化硅、具掺杂剂的硅材料、氮化物、氮氧化物、或上述材料的混合物。

8.根据权利要求7所述的纳米线结构,其中所述介电材料包括氮化硅、氧化硅或氮氧化硅。

9.根据权利要求1所述的纳米线结构,其中所述介电材料包含具有厚度为约5埃至约50埃的氮氧化硅层。

10.根据权利要求1所述的纳米线结构,其中所述介电材料是通过原子层沉积工艺产生的。

11.根据权利要求1所述的纳米线结构,其中所述堆叠位于包含氧化硅、氮化硅或氮氧化硅的材料层上。

12.根据权利要求11所述的纳米线结构,其中所述材料层位于包含硅的基板上。

13.一种纳米线结构,包括:

14.根据权利要求13所述的纳米线结构,其中所述间隙的每一者含有下述的至少一者:氢、氧、氩、氮、氦、或上述物质的混合物。

15.根据权利要求13所述的纳米线结构,其中所述间隙的每一者含有氧、氮、以及氢、氦中的至少一者、或上述物质的混合物。

16.根据权利要求13所述的纳米线结构,其中所述介电材料包含氮化硅、氧化硅或氮氧化硅。

17.根据权利要求13所述的纳米线结构,所述介电材料具有约5埃至约50埃的厚度,并且是通过原子层沉积工艺产生的。

18.根据权利要求13所述的纳米线结构,其中所述第一层的每一者是硅层,且所述第二层的每一者是sige层。

19.根据权利要求13所述的纳米线结构,其中所述堆叠包括至少重复四对的所述第一层和所述第二层。

20.一种纳米线结构,包括:

技术总结

本公开内容提供一种使用期望材料形成用于半导体晶片的水平环绕式栅极(hGAA)结构场效应晶体管(FET)的纳米线结构的设备与方法。一个范例中,一种形成纳米线结构的方法包括将介电材料沉积在堆叠的第一侧与第二侧上。堆叠可包括重复多对的第一层与第二层。第一侧与第二侧相对,且第一侧与第二侧具有形成于第一侧与第二侧中的一个或多个凹部。该方法包括从堆叠的第一侧及第二侧移除介电材料。介电材料保留在一个或多个凹部中。该方法包括沉积应力源层及在应力源层与堆叠的第一侧及所述第二侧之间形成一个或多个侧隙。

技术研发人员:孙世宇,纳姆·孙·基姆,邴希·孙·伍德,吉田娜奥米,龚盛钦,金苗

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!