一种可用于多尺寸互连的凹槽式转接板制备工艺的制作方法

本发明涉及电子封装领域,特别涉及一种可用于多尺寸互连的凹槽式转接板制备工艺。

背景技术:

1、随着对高性能计算(hpc)需求的不断增长,异构集成已经成为了一个重要的性能实现方式。根据芯片的不同需要,互连通道的大小也要随着变化,因此为了解决不同大小的凸块放置空间需求,配适不同互连凸块的使用,本申请提出了一种凹槽式转接板的制备工艺,可以方便快速的制备转接板,保证不同大小互连凸块的空间需求。

技术实现思路

1、本发明提供了一种可用于多尺寸互连的凹槽式转接板制备工艺,其目的是为了提供一种可以方便快速制备转接板的工艺,保证不同大小互连凸块的空间需求。

2、为了达到上述目的,本发明的实施例提供了一种可用于多尺寸互连的凹槽式转接板制备工艺,包括:

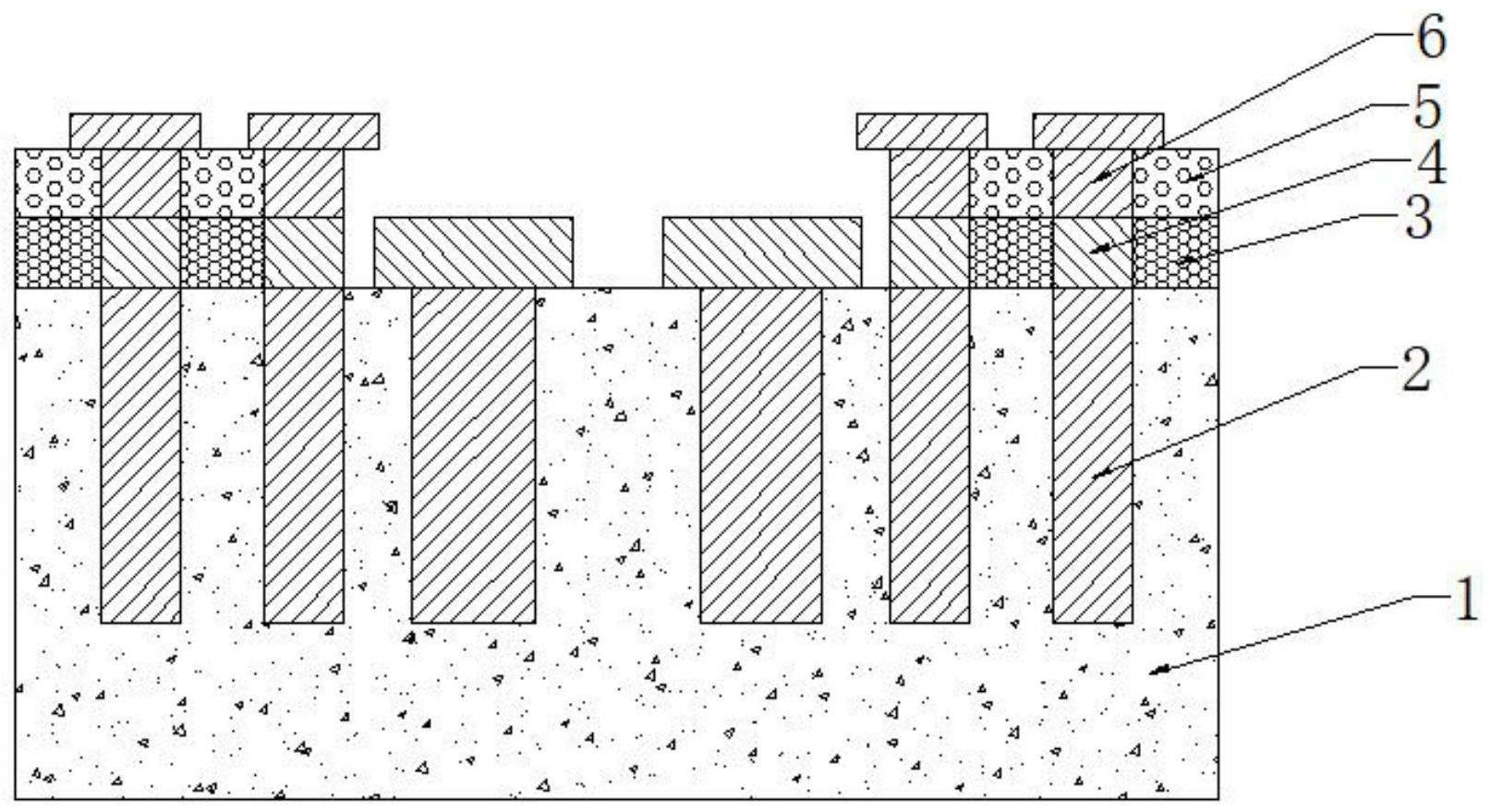

3、s1.在转接板本体的上表面开设有盲孔,所述盲孔包括多个位于转接板本体中央的中部盲孔及多个位于中部盲孔周围的侧部盲孔,

4、s2.在各盲孔内填充导电材料至与转接板本体的上表面齐平;

5、s3.在转接板本体的上表面设置有第一介电层,蚀刻第一介电层,并在各盲孔的周围形成第一介电支撑;

6、s4.在第一介电支撑的间隙内设置第一导电层,第一导电层与第一介电支撑齐平,第一导电层在中部盲孔处形成中部焊盘;

7、s5.在第一介电层和第一导电层的上方设置有第二介电层,并对第二介电层进行蚀刻形成第二介电支撑和第三介电支撑,所述第二介电支撑覆盖于中部焊盘,第三介电支撑与侧部盲孔周围的第一介电支撑共线;

8、s6.在第二介电支撑和/或第三介电支撑的间隙内设置第二导电层,第二导电层与第二介电支撑齐平;

9、s7.在第二介电层和第二导电层上方设置有第三介电层,对第三介电层进行蚀刻,使得侧部盲孔上方的第二导电层裸露,在第二导电层裸露处设置第三导电层形成侧部焊盘;

10、s8.清除第三介电层和第二介电层位于中部焊盘上方的部分,并在清除的位置粘合有临时载板;

11、s9.翻转转接板本体,并对转接板本体的下表面进行研磨直至导电材料裸露,重复步骤s3-s7后,将临时载板拆除。

12、优选地,在步骤s3、s5、和s7中,进行蚀刻前在相应的第一介电层、第二介电层和第三介电层上涂覆有光刻胶层,在蚀刻结束后,清除光刻胶层。

13、优选地,所述第一介电层、第二介电层和第三介电层为通过pecvd形成二氧化硅层。

14、优选地,所述第一介电层、第二介电层和第三介电层为旋涂的树脂层。

15、优选地,所述第一导电层和第二导电层采用化学沉积或电镀的方式形成。

16、优选地,在步骤s1中,中部盲孔的直径大于侧部盲孔的直径。

17、本发明的上述方案有如下的有益效果:

18、在本申请中,通过对第一介电层、第二介电层进行不同蚀刻,形成用于容纳凸块的空间,解决了凸块互连的空间需求,具有操作简便、成品效率高的优势。

19、本发明的其它特征和优点将在随后的具体实施方式部分予以详细说明。

技术特征:

1.一种可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于,包括:

2.根据权利要求1所述的可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于:在步骤s3、s5、和s7中,进行蚀刻前在相应的第一介电层(3)、第二介电层(5)和第三介电层上涂覆有光刻胶层,在蚀刻结束后,清除光刻胶层。

3.根据权利要求1所述的可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于:所述第一介电层(3)、第二介电层(5)和第三介电层为通过pecvd形成二氧化硅层。

4.根据权利要求1所述的可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于:所述第一介电层(3)、第二介电层(5)和第三介电层为旋涂的树脂层。

5.根据权利要求1所述的可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于:所述第一导电层(4)和第二导电层(6)采用化学沉积或电镀的方式形成。

6.根据权利要求1所述的可用于多尺寸互连的凹槽式转接板制备工艺,其特征在于:在步骤s1中,中部盲孔的直径大于侧部盲孔的直径。

技术总结

本发明提供了可用于多尺寸互连的凹槽式转接板制备工艺,涉及电子封装领域,在转接板本体上设置中部盲孔及侧部盲孔,各盲孔内填充导电材料,在转接板本体的上表面设置有第一介电层,蚀刻第一介电层,并在各盲孔的周围形成第一介电支撑;在第一介电支撑的间隙内设置第一导电层,并在中部盲孔处形成中部焊盘;在第一介电层和第一导电层的上方设置有第二介电层,蚀刻第二介电层形成第二介电支撑和第三介电支撑,第二介电支撑覆盖于中部焊盘;在第二介电支撑和/或第三介电支撑的间隙内设置第二导电层;在第二介电层和第二导电层上方设置有第三介电层,对第三介电层进行蚀刻,使得第二导电层裸露,在第二导电层裸露处设置第三导电层形成侧部焊盘。

技术研发人员:滕晓东,郑博宇,刘振

受保护的技术使用者:长沙安牧泉智能科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!