具有柔性互连件的半导体裸片组合件以及相关联方法和系统与流程

本公开大体上涉及半导体装置组合件,且更具体地说,涉及具有柔性互连件的半导体裸片组合件以及相关联方法和系统。

背景技术:

1、半导体封装通常包含安装在封装衬底上且包覆在保护性覆盖物中的一或多个半导体裸片(例如,存储器芯片、微处理器芯片、成像器芯片)。半导体裸片包含各种功能特征,如存储器单元、处理器电路或成像器装置,以及电连接到功能特征的接合垫。接合垫电连接到封装衬底的对应导电结构,所述对应导电结构耦合到保护性覆盖物外部的端子,使得半导体裸片可连接到较高层级的电路系统。在某些半导体封装中,使用倒装芯片接合技术将半导体裸片附接到封装衬底。

2、市场压力不断地驱使半导体制造商减小裸片封装的大小以适应电子装置的空间限制,同时还给半导体制造商施压以增加每一封装的功能容量。一种用于增加半导体封装的处理功率而不大体上增加封装所占据的表面积的方法是在单个封装中将多个半导体裸片竖直堆叠在彼此的顶部上。在一些情况下,半导体裸片以“z字形”图案堆叠以在接合垫上方提供相对于上覆于接合垫上方的半导体裸片的空间。在一些半导体封装中,减小半导体裸片的厚度以堆叠多个半导体裸片而不增加半导体封装的总高度。

技术实现思路

技术特征:

1.一种半导体裸片,其包括:

2.根据权利要求1所述的半导体裸片,其中:

3.根据权利要求1所述的半导体裸片,其中:

4.根据权利要求3所述的半导体裸片,其中:

5.根据权利要求1所述的半导体裸片,其中所述刚性区段为所述导电柱的第一刚性区段,且所述导电柱进一步包括第二刚性区段,所述第二刚性区段连接到所述第一柔性区段以使得所述第一柔性区段位于所述第一刚性区段与所述第二刚性区段之间。

6.根据权利要求5所述的半导体裸片,其中:

7.根据权利要求6所述的半导体裸片,其中所述第二柔性区段配置成附接到封装衬底的衬底接合垫。

8.根据权利要求6所述的半导体裸片,其中:

9.根据权利要求5所述的半导体裸片,其中所述导电柱进一步包括第三刚性区段,所述第三刚性区段连接到所述第二柔性区段以使得所述第二柔性区段位于所述第一刚性区段与所述第三刚性区段之间。

10.根据权利要求9所述的半导体裸片,其中:

11.根据权利要求10所述的半导体裸片,其中:

12.一种方法,其包括:

13.根据权利要求12所述的方法,其中形成所述多个导电柱包括:

14.根据权利要求12所述的方法,其中所述刚性区段为所述导电柱的第一刚性区段,且所述方法进一步包括:

15.根据权利要求14所述的方法,其中形成所述多个导电柱包括:

16.一种半导体裸片组合件,其包括:

17.根据权利要求16所述的半导体裸片组合件,其中每一导电柱的所述第一柔性区段进一步附接到所述多个中的对应接合垫,使得所述第一柔性区段位于所述接合垫与所述刚性区段的所述第一侧之间。

18.根据权利要求16所述的半导体裸片组合件,其中:

19.根据权利要求16所述的半导体裸片组合件,其中所述刚性区段为所述导电柱的第一刚性区段,且所述导电柱进一步包括第二刚性区段,所述第二刚性区段连接到所述第一柔性区段以使得所述第一柔性区段位于所述第一刚性区段与所述第二刚性区段之间。

20.根据权利要求19所述的半导体裸片,其中:

技术总结

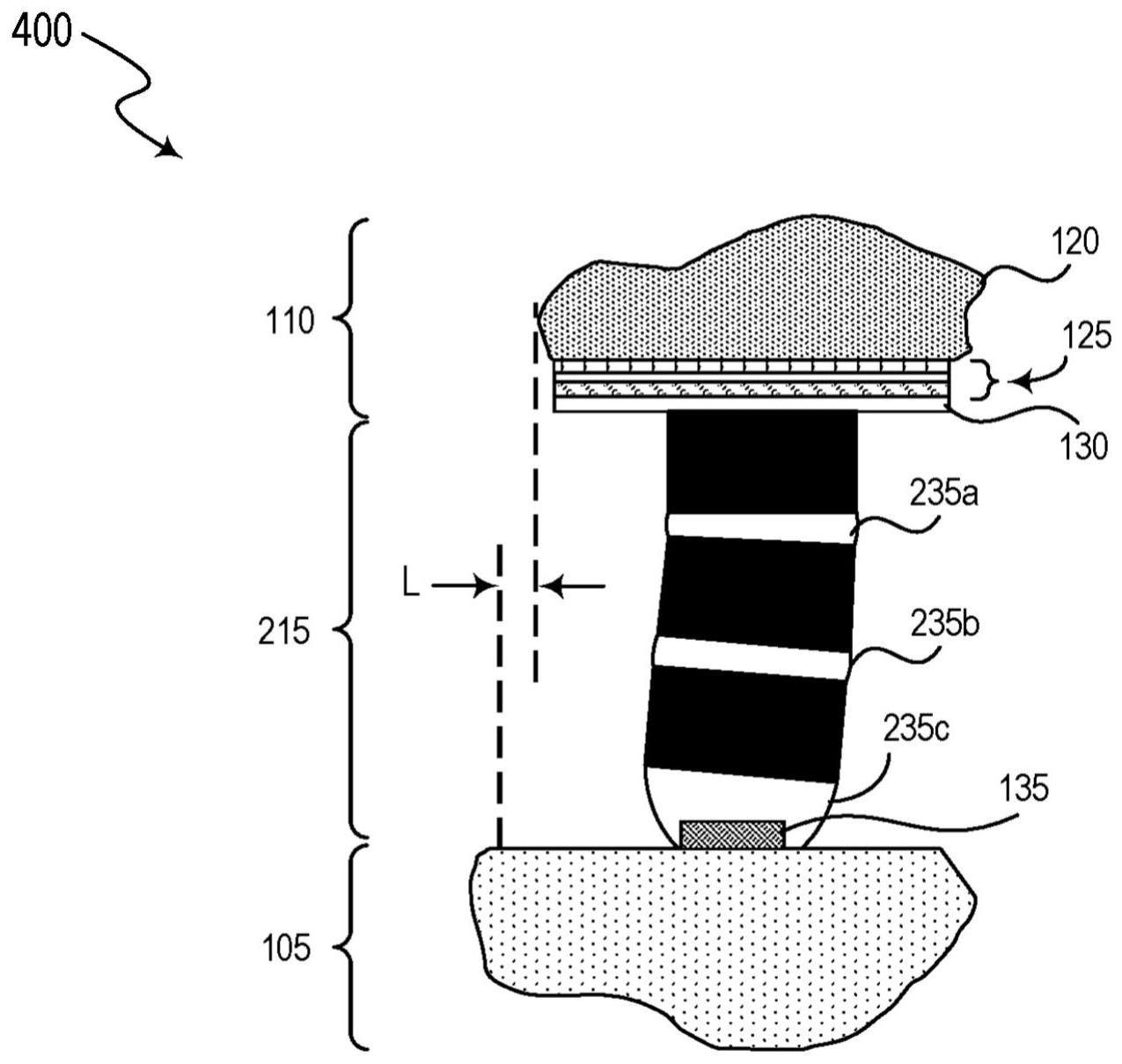

公开具有柔性互连件的半导体裸片组合件以及相关联方法和系统。所述半导体裸片组合件包含封装衬底和通过所述柔性互连件附接到所述封装衬底的半导体裸片。所述柔性互连件包含一或多个刚性区段和一或多个柔性区段,所述柔性区段中的每一个紧靠所述刚性区段安置。所述柔性区段可包含具有相对较低熔融温度的可延展材料(例如,在高温下具有相对较低的模量),使得所述柔性互连件可在组装过程期间具有减小的挠曲硬度。通过响应于在所述组装过程期间产生的应力的塑性变形,所述柔性互连件的所述可延展材料可促使所述柔性互连件的部分移位,以便减少所述应力到所述半导体裸片组合件的其它部分——例如,所述半导体裸片的电路系统的转移。

技术研发人员:C·格兰西,S·U·阿里芬,K·辛哈,Q·阮

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!