光感测单元及光感测装置的制作方法

本申请涉及感光成像,尤其是一种光感测单元及光感测装置。

背景技术:

1、传统的cmos图像传感器芯片,通常是将像素单元的感光器件(例如光电二极管)与像素原位信号放大电路的mos器件同置于一个半导体层内,这使得感光器件的收光区域的面积受到限制,无法有效提高感光器件的光学填充因子,换言之,这将造成像素单元的整体面积增大而降低感光效率,进而导致芯片的面积和成本增加。另外,在成像时,由于相邻像素单元的感光器件之间存在原位信号放大电路,可能产生影像盲区,从而影响成像效果。

技术实现思路

1、本申请提供一种光感测单元及光感测装置,以解决背景技术中的至少部分技术问题。

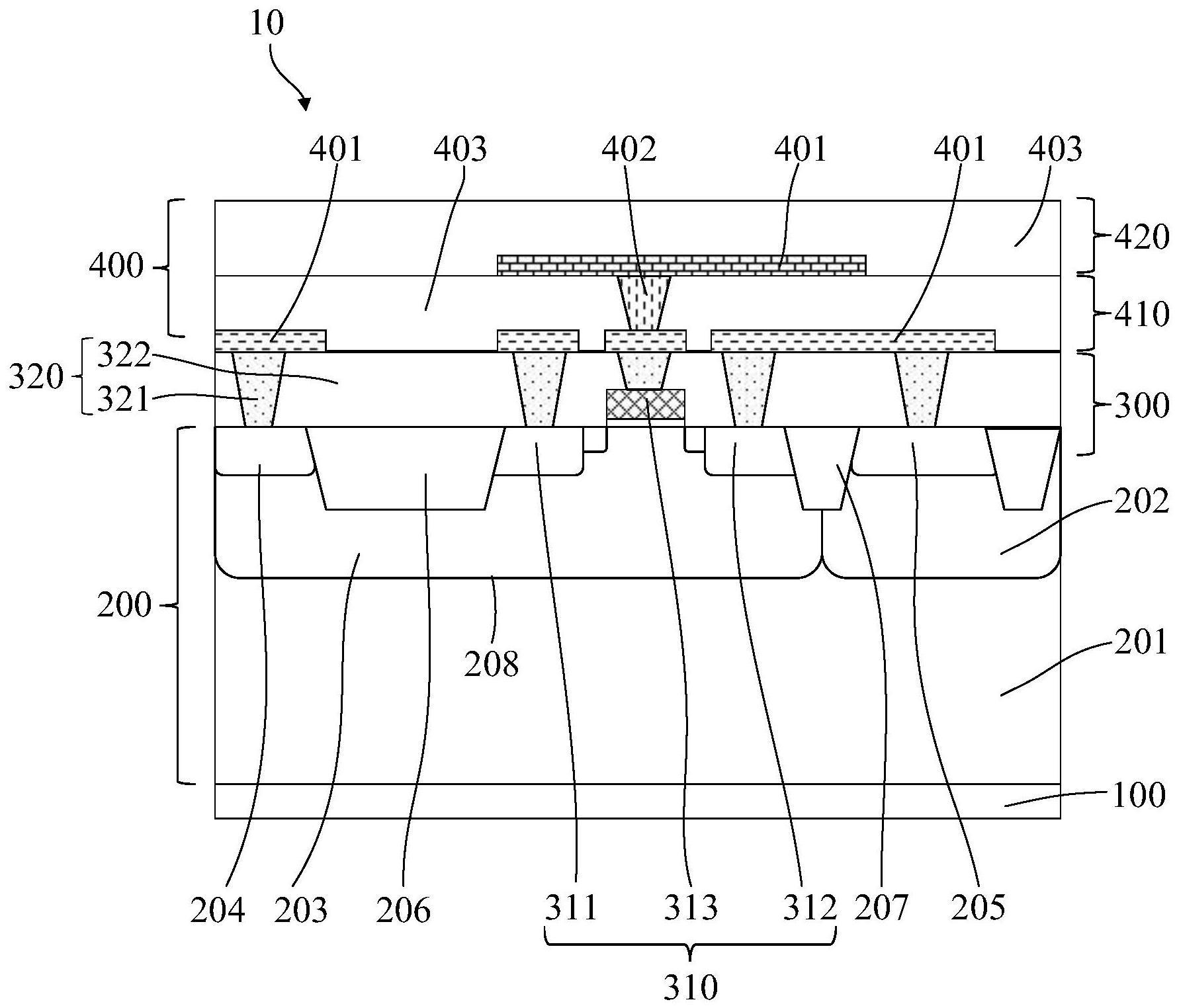

2、本申请一方面的实施例提供一种光感测单元,光感测单元包括:单一基板;感光区,配置于所述基板上;线路区,直接配置于所述感光区上。

3、在一些实施例中,所述线路区在垂直于所述基板的方向上部分地嵌入所述感光区内。

4、在一些实施例中,所述感光区包括配置于所述基板上的第一型半导体埋层、配置于所述第一型半导体埋层上的第一型半导体阱区、以及配置于所述第一型半导体埋层上的第二型半导体阱区;所述线路区包括至少一个晶体管,所述晶体管的有源区配置于所述第二型半导体阱区内。

5、在一些实施例中,所述晶体管包括:源极,配置于所述第二型半导体阱区中;漏极,配置于所述第二型半导体阱区中;栅极,配置于所述第二型半导体阱区的背对所述第一型半导体埋层的表面上。

6、在一些实施例中,所述感光区还包括:第一电极,配置于所述第二型半导体阱区中;第二电极,配置于所述第一型半导体阱区中。

7、在一些实施例中,所述第一电极和所述晶体管的有源区由配置于所述第二型半导体阱区内的第一绝缘层隔开,所述第二电极和所述晶体管的有源区由配置于所述第一型半导体阱区和所述第二型半导体阱区内的第二绝缘层隔开。

8、在一些实施例中,光感测单元还包括:金属层,配置于所述线路区上,所述第一电极和所述第二电极分别与所述金属层电性连接。

9、在一些实施例中,所述基板的厚度为5μm~7μm。

10、本申请另一方面的实施例提供一种光感测装置,光感测装置包括多个呈阵列排布的所述光感测单元。

11、在一些实施例中,所述光感测装置为背照式图像传感器。

12、在本申请实施例的光感测单元及光感测装置中,将线路区配置于感光区上,线路区不会占据光感测单元的横向空间,也就不会限制感光区的收光面积,使感光区的收光面积可以近似等于光感测单元的横向面积,从而有效提高光学填充因子。另外,将线路区直接配置于感光区上,不必再另外设置基板来配置线路区,故仅需单一基板,从而简化制程,并降低成本。

技术特征:

1.一种光感测单元,其特征在于,包括:

2.根据权利要求1所述的光感测单元,其特征在于,

3.根据权利要求2所述的光感测单元,其特征在于,

4.根据权利要求3所述的光感测单元,其特征在于,所述晶体管包括:

5.根据权利要求3所述的光感测单元,其特征在于,所述感光区还包括:

6.根据权利要求5所述的光感测单元,其特征在于,

7.根据权利要求6所述的光感测单元,其特征在于,还包括:

8.根据权利要求1所述的光感测单元,其特征在于,所述基板的厚度为5μm~7μm。

9.一种光感测装置,其特征在于,包括多个呈阵列排布的权利要求1至8任一项所述的光感测单元。

10.根据权利要求9所述的光感测装置,其特征在于,所述光感测装置为背照式图像传感器。

技术总结

本申请提供一种光感测单元及光感测装置,光感测单元包括单一基板、配置于基板上的感光区、以及直接配置于感光区上的线路区。光感测装置包括多个呈阵列排布的光感测单元。本申请通过将线路区配置于感光区上,线路区不会占据光感测单元的横向空间,也就不会限制感光区的收光面积,使感光区的收光面积可以近似等于光感测单元的横向面积,从而有效提高光学填充因子;通过将线路区直接配置于感光区上,不必再另外设置基板来配置线路区,故仅需单一基板,从而简化制程,并降低成本。

技术研发人员:吴劲昌,庄富翔

受保护的技术使用者:神盾股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!