改善MOS器件电性失配的方法与流程

本发明涉及半导体,特别是涉及一种改善mos器件电性失配的方法。

背景技术:

1、离子注入工艺是将原子或分子电离,加速到一定的能量后,再注入到芯片中进行掺杂的过程。由于单晶硅中的晶格原子整齐的排列,在特定的角度存在很多的通道,如果离子以垂直的角度进入通道,则其只要带很少的能量就可以行进一个很长的距离,无法精确控制深度,即离子注入的通道效应(channeling effect)。预非晶化是一种常用的抑制通道效应方法,通常采用锗、硅、氙等注入使单晶硅表面非晶化,从而达到抑制通道离子。

2、mos器件的mismatch(电性失配)主要来源于芯片制作过程中的工艺波动。随着器件尺寸的不断缩小,栅极尺寸也相应减小,为降低短沟道效应源漏极的结深也相应减小,预非晶化是一种常用的抑制通道效应、有效控制结深的方法,因此预非晶化的一致性对于离子注入量和深度均匀性至关重要。

3、为解决上述问题,需要提出一种新型的改善mos器件电性失配的方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种改善mos器件电性失配的方法,用于解决现有技术中mos器件的电性失配主要来源于芯片制作过程中的工艺波动,随着器件尺寸的不断缩小,栅极尺寸也相应减小,为降低短沟道效应源漏极的结深也相应减小,预非晶化是一种常用的抑制通道效应、有效控制结深的方法,但是多步预非晶化的一致性难以控制的问题。

2、为实现上述目的及其他相关目的,本发明提供一种改善mos器件电性失配的方法,包括:

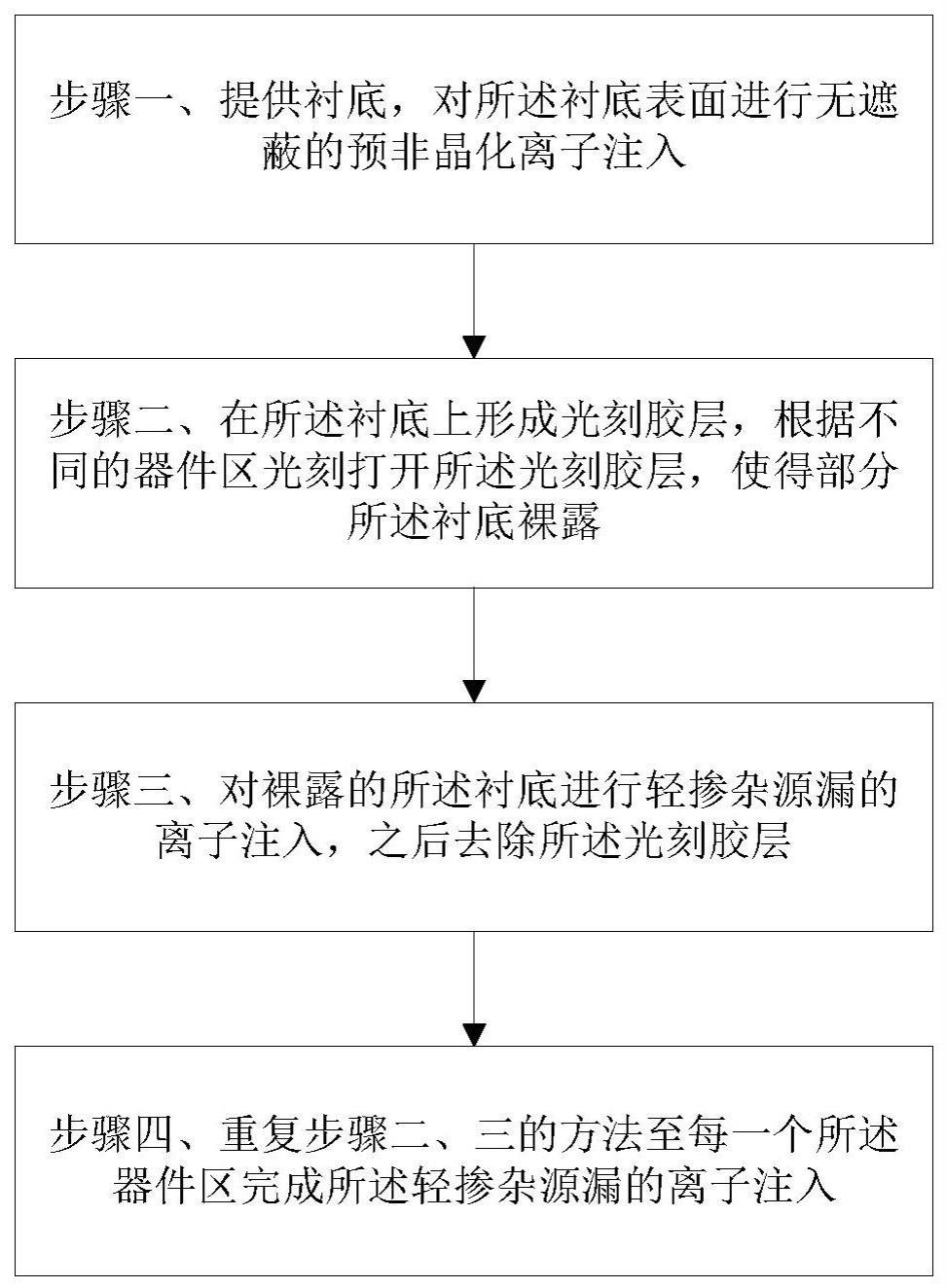

3、步骤一、提供衬底,对所述衬底表面进行无遮蔽的预非晶化离子注入;

4、步骤二、在所述衬底上形成光刻胶层,根据不同的器件区光刻打开所述光刻胶层,使得部分所述衬底裸露;

5、步骤三、对裸露的所述衬底进行轻掺杂源漏的离子注入,之后去除所述光刻胶层;

6、步骤四、重复步骤二、三的方法至每一个所述器件区完成所述轻掺杂源漏的离子注入。

7、优选地,步骤一中的所述衬底包括块状半导体衬底或绝缘体上硅衬底。

8、优选地,步骤一中所述预非晶化离子注入的离子源包括ge、si和xe。

9、优选地,步骤二中的所述器件区包括低压器件区和高压器件区。

10、优选地,步骤三中对nmos进行所述轻掺杂源漏的离子注入的离子源包括p、p2、p4、as、as2、as4。

11、优选地,步骤三中对pmos进行所述轻掺杂源漏的离子注入的离子源包括b、bf2、b10h14、b12h22、c2b10h12。

12、优选地,步骤三中利用灰化工艺以及湿法清洗的方法去除所述光刻胶层。

13、如上所述,本发明的改善mos器件电性失配的方法,具有以下有益效果:

14、本发明的方法改善了mos器件电性失配的问题,提高了器件良率。

技术特征:

1.一种改善mos器件电性失配的方法,其特征在于,至少包括:

2.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤一中的所述衬底包括块状半导体衬底或绝缘体上硅衬底。

3.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤一中所述预非晶化离子注入的离子源包括ge、si和xe。

4.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤二中的所述器件区包括低压器件区和高压器件区。

5.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤三中对nmos进行所述轻掺杂源漏的离子注入的离子源包括p、p2、p4、as、as2、as4。

6.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤三中对pmos进行所述轻掺杂源漏的离子注入的离子源包括b、bf2、b10h14、b12h22、c2b10h12。

7.根据权利要求1所述的改善mos器件电性失配的方法,其特征在于:步骤三中利用灰化工艺以及湿法清洗的方法去除所述光刻胶层。

技术总结

本发明提供一种改善MOS器件电性失配的方法,提供衬底,对衬底表面进行无遮蔽的预非晶化离子注入;在衬底上形成光刻胶层,根据不同的器件区光刻打开光刻胶层,使得部分衬底裸露;对裸露的衬底进行轻掺杂源漏的离子注入,之后去除光刻胶层;重复上述的方法至每一个器件区完成轻掺杂源漏的离子注入。本发明的方法改善了MOS器件电性失配的问题,提高了器件良率。

技术研发人员:翟海涛,赵鹏,齐瑞生,黄冠群

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!