制作半导体装置的方法与半导体装置与流程

本揭露是有关于一种制作半导体装置的方法与半导体装置。

背景技术:

1、随着近年来随着太阳能电子、汽车电子以及高频化高功率密度化电源模组等电力电子技术快速发展,对电力电子设备的功率密度也提出了更高的要求。又因应电动车的兴起,晶体管元件的技术发展也随着往高电压大电流的高功率方向发展,其中大电流的晶体管元件除了将元件尺寸放大来实现之外,亦可经由导通阻抗(ron)的降低来达成。

技术实现思路

1、本揭露的一态样提供了一种制作半导体装置的方法,包含提供基板,基板为碳化硅基底,基板由下而上依序包含n型重掺杂基层、n型轻掺杂层、p型阱区域,以及n型重掺杂层。接着,使用图案化遮罩蚀刻基板,以形成至少一栅极沟槽以及由栅极沟槽所定义的通道区域,其中通道区域被图案化遮罩所覆盖。接着,对栅极沟槽进行离子注入,以在栅极沟槽的底面形成遮蔽注入层。对栅极沟槽进行氧化工艺,以形成栅极氧化物层,其中栅极沟槽的底面的氧化速率大于栅极沟槽的侧壁的氧化速率,以及形成栅极电极于栅极沟槽中。

2、在一些实施例中,离子注入所使用的离子包含磷、砷或氩。

3、在一些实施例中,制作半导体装置的方法还包含在对栅极沟槽进行离子注入之后,移除图案化遮罩。

4、在一些实施例中,制作半导体装置的方法还包含在移除图案化遮罩之后,进行退火。

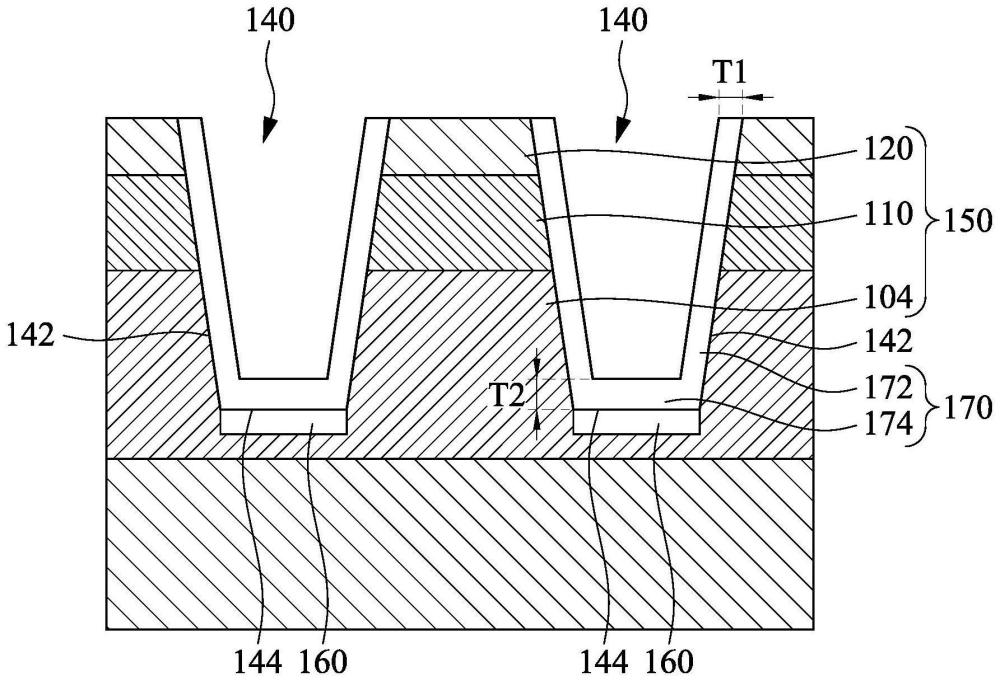

5、在一些实施例中,蚀刻基板以形成栅极沟槽的步骤包含使栅极沟槽的侧壁具有倾斜角度。

6、在一些实施例中,对栅极沟槽进行离子注入的角度为垂直于栅极沟槽的底面。

7、在一些实施例中,对栅极沟槽进行离子注入的角度为朝向通道区域倾斜。

8、在一些实施例中,使用图案化遮罩蚀刻基板的步骤终止在n型轻掺杂层。

9、本揭露的另一态样提供了一种半导体装置,包含设置在n型重掺杂基层上的通道区域,通道区域从n型重掺杂基层起依序包含n型轻掺杂层、p型阱区域,以及n型重掺杂层,其中通道区域与n型重掺杂基层皆为碳化硅基底。半导体装置还包含两栅极电极以及两栅极氧化物层。两栅极电极设置于通道区域的两侧,其中栅极电极的顶表面与通道区域的顶表面共平面。两栅极氧化物层分别包覆栅极电极的侧壁与底面,其中栅极氧化物层在栅极电极的底面的厚度不小于栅极氧化物层在栅极电极的侧壁的厚度。

10、在一些实施例中,半导体装置还包含两遮蔽注入层,分别位于栅极氧化物层的底部,其中栅极电极的底部宽度等于或是小于遮蔽注入层的宽度。

11、在一些实施例中,栅极氧化物层的宽度等于遮蔽注入层的宽度。

12、在一些实施例中,遮蔽注入层的宽度大于栅极氧化物层的宽度,且遮蔽注入层从栅极电极的底部单侧地延伸进入通道区域。

13、在一些实施例中,栅极氧化物层具有位在栅极电极的侧壁的第一部分与位在栅极电极的底面的第二部分,第一部分的厚度为30nm至200nm,第二部分的厚度为30nm至400nm。

14、本揭露的又一态样提供了一种半导体装置,包含设置在n型重掺杂基层上的通道区域,通道区域从n型重掺杂基层起依序包含n型轻掺杂层、p型阱区域,以及n型重掺杂层,其中通道区域与n型重掺杂基层皆为碳化硅基底。半导体装置还包含栅极电极以及栅极氧化物层。栅极电极连续地包围通道区域的侧壁,其中栅极电极的顶表面与通道区域的顶表面共平面。栅极氧化物层包覆栅极电极的侧壁与底面,其中栅极氧化物层在栅极电极的底面的厚度不小于栅极氧化物层在栅极电极的侧壁的厚度。

15、在一些实施例中,半导体装置还包含位于栅极氧化物层的底部的遮蔽注入层,其中栅极电极的底部宽度等于或是小于遮蔽注入层的宽度。

16、在一些实施例中,栅极氧化物层的宽度等于遮蔽注入层的宽度。

17、在一些实施例中,遮蔽注入层的宽度大于栅极氧化物层的宽度,且遮蔽注入层从栅极电极的底部单侧地延伸进入通道区域。

18、在一些实施例中,栅极氧化物层具有位在栅极电极的侧壁的第一部分与位在栅极电极的底面的第二部分,第一部分的厚度为30nm至200nm,第二部分的厚度为30nm至400nm。

19、本揭露提供了一种制作半导体装置的方法与半导体装置,包含利用自对准离子注入工艺在栅极沟槽的底面形成遮蔽注入层,以降低栅极氧化物层的崩溃电压与底部电场,并利用自对准离子注入工艺使得在栅极沟槽的侧壁与底面上氧化层的成长速度不同,使得后续所形成的栅极氧化物层的底部厚度不小于侧壁厚度,借以降低沟槽式栅极的半导体装置在栅极氧化物层的底部的电场。

技术特征:

1.一种制作半导体装置的方法,其特征在于,包含:

2.根据权利要求1所述的制作半导体装置的方法,其中该离子注入所使用的离子包含磷、砷或氩。

3.根据权利要求1所述的制作半导体装置的方法,其中还包含在对该至少一栅极沟槽进行该离子注入之后,移除该图案化遮罩。

4.根据权利要求3所述的制作半导体装置的方法,其中还包含在移除该图案化遮罩之后,进行退火。

5.根据权利要求1所述的制作半导体装置的方法,其中蚀刻该基板,以形成该至少一栅极沟槽的步骤包含使该至少一栅极沟槽的侧壁具有倾斜角度。

6.根据权利要求1所述的制作半导体装置的方法,其中对该至少一栅极沟槽进行该离子注入的角度为垂直于该至少一栅极沟槽的底面。

7.根据权利要求1所述的制作半导体装置的方法,其中对该至少一栅极沟槽进行该离子注入的角度为朝向该通道区域倾斜。

8.根据权利要求1所述的制作半导体装置的方法,其中使用该图案化遮罩蚀刻该基板终止在该n型轻掺杂层。

9.一种半导体装置,其特征在于,包含:

10.根据权利要求9所述的半导体装置,其中还包含两遮蔽注入层,分别位于所述多个栅极氧化物层的底部,其中各该栅极电极的底部宽度等于或是小于各该遮蔽注入层的宽度。

11.根据权利要求10所述的半导体装置,其中各该栅极氧化物层的宽度等于各该遮蔽注入层的宽度。

12.根据权利要求10所述的半导体装置,其中各该遮蔽注入层的宽度大于各该栅极氧化物层的宽度,且各该遮蔽注入层从各该栅极电极的底部单侧地延伸进入该通道区域。

13.根据权利要求9所述的半导体装置,其中各该栅极氧化物层具有位在各该栅极电极的侧壁的第一部分与位在各该栅极电极的底面的第二部分,该第一部分的厚度为30nm至200nm,该第二部分的厚度为30nm至400nm。

14.一种半导体装置,其特征在于,包含:

15.根据权利要求14所述的半导体装置,其中还包含遮蔽注入层,位于该栅极氧化物层的底部,其中该栅极电极的底部宽度等于或是小于该遮蔽注入层的宽度。

16.根据权利要求15所述的半导体装置,其中该栅极氧化物层的宽度等于该遮蔽注入层的宽度。

17.根据权利要求15所述的半导体装置,其中该遮蔽注入层的宽度大于该栅极氧化物层的宽度,且该遮蔽注入层从该栅极电极的底部单侧地延伸进入该通道区域。

18.根据权利要求14所述的半导体装置,其中该栅极氧化物层具有位在该栅极电极的侧壁的第一部分与位在该栅极电极的底面的第二部分,该第一部分的厚度为30nm至200nm,该第二部分的厚度为30nm至400nm。

技术总结

一种制作半导体装置的方法,包含提供基板,基板为碳化硅基底,基板由下而上依序包含N型重掺杂基层、N型轻掺杂层、P型阱区域,以及N型重掺杂层。接着,使用图案化遮罩蚀刻基板,以形成栅极沟槽以及由栅极沟槽所定义的通道区域,其中通道区域被图案化遮罩所覆盖。接着,对栅极沟槽进行离子注入,以在栅极沟槽的底面形成遮蔽注入层。对栅极沟槽进行氧化工艺,以形成栅极氧化物层,其中栅极沟槽的底面的氧化速率大于栅极沟槽的侧壁的氧化速率,以及形成栅极电极于栅极沟槽中。一种半导体装置亦在此揭露。制作半导体装置的方法利用自对准离子注入工艺在栅极沟槽的底面形成遮蔽注入层,以降低沟槽式栅极的半导体装置在栅极氧化物层底部的电场。

技术研发人员:洪嘉隆,萧逸楷,郭浩中

受保护的技术使用者:鸿海精密工业股份有限公司

技术研发日:

技术公布日:2024/9/5

- 还没有人留言评论。精彩留言会获得点赞!