HEMT器件及其制备方法与流程

本申请涉及电路,尤其涉及一种hemt器件及其制备方法。

背景技术:

1、高电子迁移率晶体管(high electron mobility transistors,hemt)具有高击穿电压、低导通电阻、高开关速度和高能量转换效率等优异性能;cmos具有集成度高和功耗低等优势,将hemt和cmos集成在同一衬底上,可以显著提高器件的综合性能,因此,与cmos单片集成的hemt器件(亦可称为互补型hemt)被越来越广泛地应用于电动汽车、电网、和电力电子等领域。

2、互补型的hemt器件同时包括p沟道金属氧化物半导体(p-metal-oxide-semiconductor,pmos)和n沟道金属氧化物半导体(n-metal-oxide-semiconductor,nmos),pmos和nmos形成在同一衬底上。

3、由于互补型hemt器件是由两个mos管构成,因此,互补型hemt器件的尺寸通常比较大,这样也会影响hemt器件的导通电阻。

技术实现思路

1、有鉴于此,本申请实施例提供一种hemt器件及其制作方法,用于减小hemt器件尺寸,进而减小hemt器件的导通电阻。

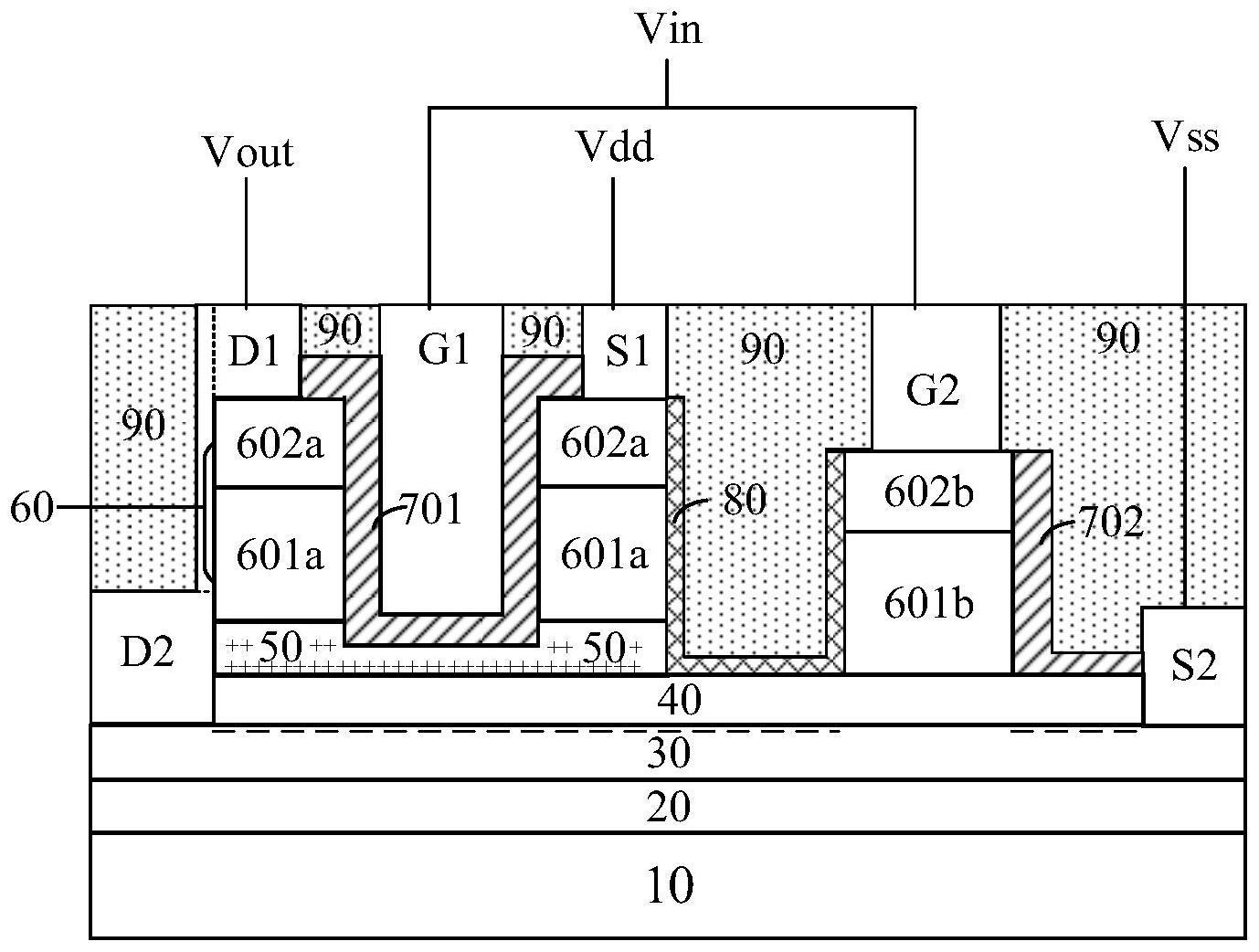

2、为了实现上述目的,第一方面,本申请实施例提供一种hemt器件,包括:衬底层、缓冲层、第一沟道层、势垒层、第二沟道层、半导体层,第一栅极介质层、第一源电极、第一漏电极和第一栅电极、隔离层、第二源电极、第二漏电极和第二栅电极、第二栅极介质层;

3、所述衬底层、所述缓冲层、所述第一沟道层、所述势垒层和所述第二沟道层自下而上层叠设置;

4、所述半导体层包括:间隔设置的pmos半导体层和nmos半导体层;

5、所述pmos半导体层位于所述第二沟道层上,第一源电极和第一漏电极设置在所述pmos半导体层上,并分布在所述pmos半导体层的两侧;所述第一栅极介质层位于所述第一源电极和所述第一漏电极之间,形成底部嵌入所述第二沟道层中的凹槽结构;所述第一栅电极位于所述第一栅极介质层上;

6、所述nmos半导体层位于所述势垒层上,所述第二栅电极位于所述nmos半导体层上;所述隔离层位于所述第一源电极和所述第二栅电极之间,形成底部接触所述势垒层的凹槽结构;

7、所述第二源电极和第二漏电极位于所述第一沟道层上,其中,所述第二源电极位于所述nmos半导体层远离所述pmos半导体层的一侧;所述第二漏电极位于所述pmos半导体层远离所述nmos半导体层的一侧,并且与所述第一漏电极接触;所述第二栅极介质层位于所述第二栅电极和所述第二源电极之间,且底部接触所述势垒层。

8、作为本申请实施例一种可选的实施方式,所述半导体层为p型半导体层。

9、作为本申请实施例一种可选的实施方式,所述p型半导体层包括自下而上层叠设置的第一半导体层和第二半导体层。

10、作为本申请实施例一种可选的实施方式,所述第二半导体层的掺杂浓度高于所述第一半导体层的掺杂浓度。

11、作为本申请实施例一种可选的实施方式,所述第一漏电极与所述pmos半导体层之间,以及,所述第一源电极与所述pmos半导体层之间均为欧姆接触;所述第一栅电极与所述第一栅极介质层之间,以及,所述第二栅电极与所述nmos半导体层之间均为肖特基接触。

12、作为本申请实施例一种可选的实施方式,所述第一沟道层和所述第二沟道层均为非故意掺杂的氮化物层。

13、作为本申请实施例一种可选的实施方式,所述势垒层由含铝组分的氮化物生成。

14、作为本申请实施例一种可选的实施方式,所述hemt器件还包括:钝化层,所述钝化层覆盖所述第二漏电极、所述第一漏电极与所述第一栅电极之间的第一栅极介质层、所述第一栅电极与所述第一源电极之间的第一栅极介质层、所述隔离层、所述第二栅极介质层和所述第二源电极。

15、作为本申请实施例一种可选的实施方式,所述第一源电极、所述第一漏电极、所述第一栅电极、所述第二源电极、所述第二栅电极和所述第二漏电极的材料均包括钛、铝、镍、金、钽中的一种或多种。

16、第二方面,本申请实施例提供一种hemt器件的制备方法,用于制备如上述第一方面所述的hemt器件,所述方法包括:

17、在衬底层表面依次生长缓冲层、第一沟道层、势垒层和第二沟道层;

18、对部分所述第二沟道层进行刻蚀后,在所述势垒层和所述第二沟道层上生长半导体层;

19、对所述半导体层和所述第二沟道层进行刻蚀,形成pmos半导体层、nmos半导体层、位于所述pmos半导体层中的栅极凹槽、位于所述pmos半导体层和所述nmos半导体层之间的隔离凹槽,并去除所述pmos半导体层远离所述nmos半导体层一侧的势垒层以及去除所述nmos半导体层远离所述pmos半导体层一侧的势垒层;

20、在所述栅极凹槽、所述隔离凹槽和所述nmos半导体层远离所述pmos半导体层一侧的势垒层上沉积绝缘介质,形成第一栅极介质层、隔离层和第二栅极介质层;

21、沉积金属层,形成第二漏电极、第一漏电极、第一栅电极、第一源电极、第二栅电极和第二源电极。

22、本申请实施例提供的技术方案,通过将第二源电极设置在nmos半导体层远离pmos半导体层的一侧,将第二漏电极设置在pmos半导体层远离nmos半导体层的一侧,与第一漏电极直接接触,可以减小hemt器件的尺寸,从而可以减小hemt器件的导通电阻;另外,在第二沟道层上制备p型半导体层可以耗尽势垒层和第一沟道层之间的二维电子气,还可以在第二沟道层与势垒层的界面处形成二维空穴气,形成pmos的导电沟道,提高了pmos器件的输出电流。

技术特征:

1.一种hemt器件,其特征在于,包括:衬底层、缓冲层、第一沟道层、势垒层、第二沟道层、半导体层,第一栅极介质层、第一源电极、第一漏电极和第一栅电极、隔离层、第二源电极、第二漏电极和第二栅电极、第二栅极介质层;

2.根据权利要求1所述的hemt器件,其特征在于,所述半导体层为p型半导体层。

3.根据权利要求2所述的hemt器件,其特征在于,所述p型半导体层包括自下而上层叠设置的第一半导体层和第二半导体层。

4.根据权利要求3所述的hemt器件,其特征在于,所述第二半导体层的掺杂浓度高于所述第一半导体层的掺杂浓度。

5.根据权利要求1所述的hemt器件,其特征在于,所述第一漏电极与所述pmos半导体层之间,以及,所述第一源电极与所述pmos半导体层之间均为欧姆接触;所述第一栅电极与所述第一栅极介质层之间,以及,所述第二栅电极与所述nmos半导体层之间均为肖特基接触。

6.根据权利要求1所述的hemt器件,其特征在于,所述第一沟道层和所述第二沟道层均为非故意掺杂的氮化物层。

7.根据权利要求1所述的hemt器件,其特征在于,所述势垒层由含铝组分的氮化物生成。

8.根据权利要求1所述的hemt器件,其特征在于,所述hemt器件还包括:钝化层,所述钝化层覆盖所述第二漏电极、所述第一漏电极与所述第一栅电极之间的第一栅极介质层、所述第一栅电极与所述第一源电极之间的第一栅极介质层、所述隔离层、所述第二栅极介质层和所述第二源电极。

9.根据权利要求1-8中任一项所述hemt器件,其特征在于,所述第一源电极、所述第一漏电极、所述第一栅电极、所述第二源电极、所述第二栅电极和所述第二漏电极的材料均包括钛、铝、镍、金、钽中的一种或多种。

10.一种hemt器件的制备方法,用于制备如权利要求1-9任一项所述的hemt器件,其特征在于,所述方法包括:

技术总结

本申请提供一种HEMT器件及其制作方法,涉及电路技术领域,其中,该HEMT器件中,NMOS的源电极设置在NMOS半导体层远离PMOS半导体层的一侧,NMOS的漏电极设置在PMOS半导体层远离NMOS半导体层的一侧,且直接与PMOS的漏电极接触,这样可以减小HEMT器件体积,从而可以减小HEMT器件的导通电阻。

技术研发人员:刘浩文,李孟泽

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!