半导体外延结构及制备方法和半导体器件与流程

本发明涉及半导体,更具体地说,涉及一种半导体外延结构及制备方法和半导体器件。

背景技术:

1、氮化镓(gan)作为第三代宽禁带半导体材料的代表,具有突出的优势。gan功率器件,在外延层标准制程的模板(template)发展过程中,基于硅(si)基功率器件结构,结合gan材料本身的物理和化学特性,开发出了一系列适合gan器件本身的金属-氧化物半导体场效应晶体管(mosfet)功率器件。

2、基于si材料制程的mosfet、绝缘栅双极型晶体管igbt(igbt)等器件的开关工作原理是通过掺杂注入技术得到的p型空穴或n型电子的载流子输运过程控制实现;基于gan材料制程的高频功率开关器件原理是基于对algan/gan异质结层中极化效应得到的二维电子气(2deg)沟道层的开通与关断控制,其2deg的迁移率远高于si材料。因2deg浓度受限与沟道层厚度较窄,通常单通道层只有10nm以下,导致所述gan功率器件工作电流小于30a/每单颗芯片和可承载的工作电压(通常小于950v)受限,存在高电压、高电流、高功率下无法突破的工作瓶颈。

技术实现思路

1、本发明的目的在于提供一种半导体外延结构及制备方法和半导体器件,以解决传统方法工作电流小、可承载工作电压受限的问题。

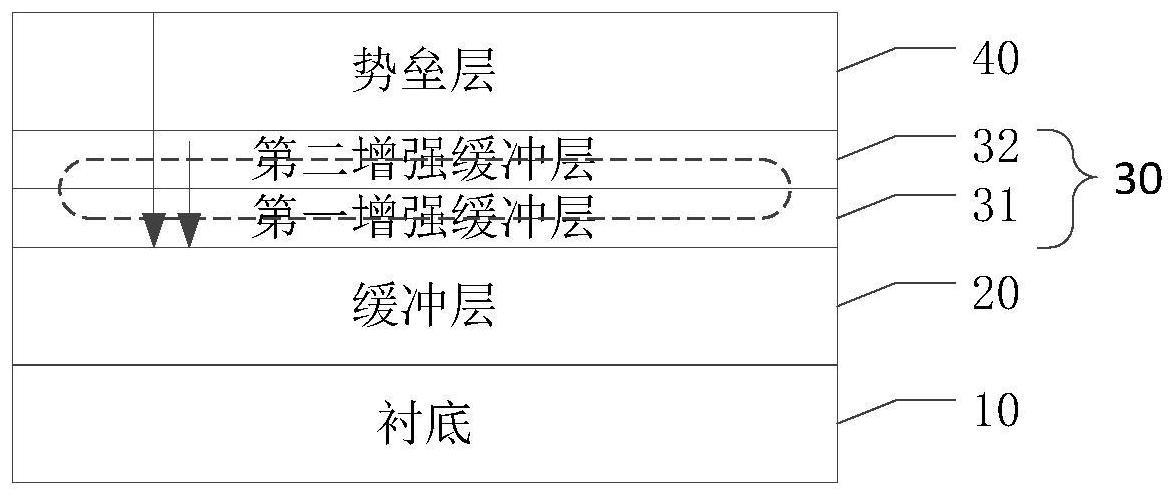

2、为解决上述技术问题,本发明提供一种半导体外延结构,包括:

3、衬底;

4、缓冲层,位于所述衬底上;

5、增强型缓冲层,所述增强型缓冲层包括第一增强缓冲层和第二增强缓冲层,所述第一增强缓冲层为si单晶薄膜层,位于所述缓冲层上,所述第二增强缓冲层为mgn单晶薄膜层,位于所述第一增强缓冲层上;

6、势垒层,所述势垒层位于所述第二增强缓冲层上。

7、在一具体实施方式中,包括多个周期交替层叠的所述增强型缓冲层和所述势垒层;

8、还包括多个阻挡层,所述增强型缓冲层和势垒层之间设置有一个阻挡层,所述阻挡层上表面与所述第一增强缓冲层接触,下表面与所述势垒层接触。

9、在一具体实施方式中,所述第一增强缓冲层单层厚度小于10nm,和/或第二增强缓冲层单层厚度小于10nm。

10、在一具体实施方式中,所述增强型缓冲层包括3~20个所述第一增强缓冲层和3~20个所述第二增强缓冲层。

11、基于同一发明构思,本发明还提供一种半导体外延结构制备方法,包括:

12、步骤s1:提供衬底;

13、步骤s2:在所述衬底上生长缓冲层;

14、步骤s3:在所述缓冲层上生长增强型缓冲层,包括步骤s31生长第一增强缓冲层和步骤s32生长第二增强缓冲层;

15、所述步骤s31包括:采用mocvd化学气相法将sih4分解为si,沉积至所述缓冲层上,生长出si单晶薄膜层;

16、所述步骤s32包括:在mocvd设备内对所述第一增强缓冲层做退火处理,在所述第一增强缓冲层上生长mgn单晶薄膜层;

17、步骤s4:在所述第二增强缓冲层上生长势垒层。

18、在一具体实施方式中,还包括:步骤s5:在所述势垒层上生长阻挡层;

19、步骤s6:重复执行步骤s3~步骤s5,且最上层是势垒层。

20、在一具体实施方式中,其特征在于,所述第一增强缓冲层单层厚度小于10nm,和/或所述第二增强缓冲层单层厚度小于10nm。

21、在一具体实施方式中,所述第一增强缓冲层生长温度为1200℃~1650℃。

22、在一具体实施方式中,所述第二增强缓冲层生长温度为850℃~1050℃。

23、基于同一发明构思,本发明还提供一种半导体器件。

24、与现有技术相比,本发明提出一种新型的外延结构,基于gan材料,同时融合si基mosfet/igbt双极性工作优点,兼容gan材料mosfet本身利用极化效应产生的二维电子气工作的特性,适合高频功率器件,其有益效果至少包括:

25、1、所述第一增强缓冲层采用si单晶薄膜层以及所述第二增强缓冲层采用mgn单晶薄膜层,单晶向程度高,缺陷密度低,厚度小于10nm避免产生多晶、应力、裂变等问题。

26、2、对si单晶薄膜层做高温退火处理可以有效去除由于杂质、多晶相等因素造成的界面态势垒,降低si单晶薄膜层与缓冲层和之后生长的mgn单晶薄膜层之间的欧姆接触,降低器件开关损耗。

27、3、所述si单晶薄膜层通过高温退火,活化激活程度高,形成了良好的电子源,而后相对低温下生长的mgn单晶薄膜层可较好的获得mg空穴载流子源,电子或载流子注入效率提升,增加沟道势垒差,降低电子泄露。

28、4、si单晶薄膜层,mgn单晶薄膜层,其净电荷方向与原有algan/gan异质结界面产生的极化电场方向一致,起到了增强、强化原有的2deg沟道层,拓宽了沟道层的有效厚度范围;沟道相互之间,由于阻挡层的隔离作用,不会互相抵消降低多沟道2deg,形成准3deg大通道的效果。

技术特征:

1.一种半导体外延结构,其特征在于,包括:

2.根据权利要求1所述的半导体外延结构,其特征在于,包括多个周期交替层叠的所述增强型缓冲层和所述势垒层;

3.根据权利要求1所述的半导体外延结构,其特征在于,所述第一增强缓冲层单层厚度小于10nm,和/或第二增强缓冲层单层厚度小于10nm。

4.根据权利要求2所述的半导体外延结构,其特征在于,所述增强型缓冲层包括3~20个所述第一增强缓冲层和3~20个所述第二增强缓冲层。

5.一种半导体外延结构制备方法,其特征在于,包括:

6.根据权利要求5所述的半导体外延结构制备方法,其特征在于,还包括:

7.根据权利要求5所述的半导体外延结构制备方法,其特征在于,所述第一增强缓冲层单层厚度小于10nm,和/或所述第二增强缓冲层单层厚度小于10nm。

8.根据权利要求7所述的半导体外延结构制备方法,其特征在于,所述第一增强缓冲层生长温度为1200℃~1650℃。

9.根据权利要求7所述的半导体外延结构制备方法,其特征在于,所述第二增强缓冲层生长温度为850℃~1050℃。

10.一种半导体器件,其特征在于,包括权利要求1~4任一项所述的外延结构。

技术总结

本发明公开了一种半导体外延结构及制备方法和半导体器件。外延结构包括:衬底;缓冲层,位于所述衬底上;增强型缓冲层,所述增强型缓冲层包括第一增强缓冲层和第二增强缓冲层,所述第一增强缓冲层为Si单晶薄膜层,位于所述缓冲层上,所述第二增强缓冲层为MgN单晶薄膜层,位于所述第一增强缓冲层上;势垒层,所述势垒层位于所述第二增强缓冲层上。采用上述结构Si单晶层,MgN单晶层,其净电荷方向与原有AlGaN/GaN异质结界面产生的极化电场方向一致,起到了增强、强化原有的2DEG沟道层,拓宽了沟道层的有效厚度范围。

技术研发人员:倪贤锋,范谦

受保护的技术使用者:苏州汉骅半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!