本发明的实施例涉及鳍式场效应晶体管及其制造方法。

背景技术:

1、随着半导体器件在尺寸上不断减小,诸如鳍式场效应晶体管(finfet)的三维多栅极结构已经发展以替代平面的互补金属氧化物半导体(cmos)器件。finfet的结构特征是硅基鳍,硅基鳍从衬底表面垂直延伸,并且包绕由鳍形成的导电沟道的栅极进一步提供了对沟道的更好的电控制。源极/漏极(s/d)和沟道的轮廓对于器件性能是至关重要的。

技术实现思路

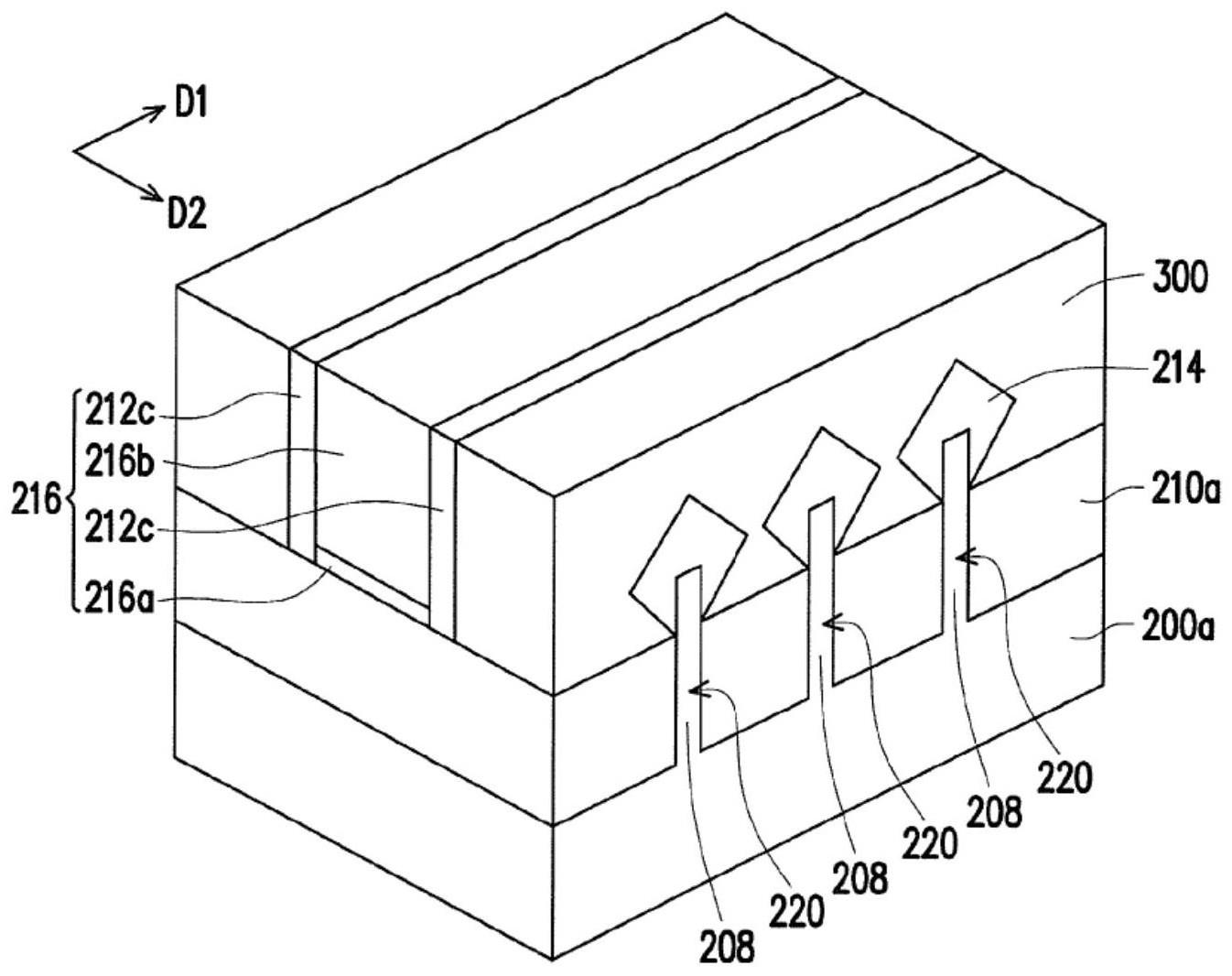

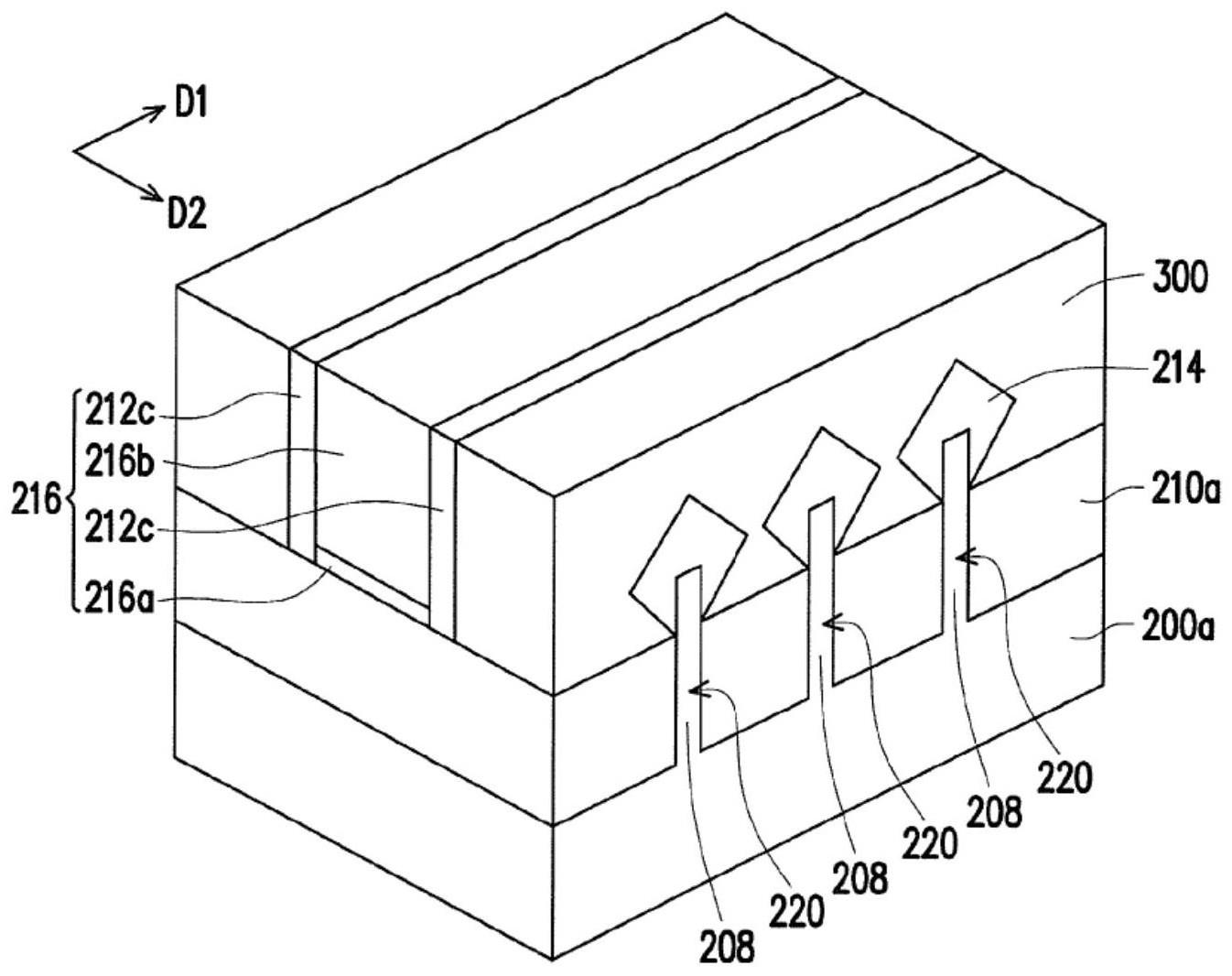

1、本发明的实施例提供了一种制造鳍式场效应晶体管(finfet)的方法,包括:图案化半导体衬底以在所述半导体衬底中形成多个沟槽并且在所述沟槽之间形成至少一个半导体鳍;在所述沟槽中形成多个绝缘体;在部分所述半导体鳍上方和部分所述绝缘体上方形成伪栅极堆叠件;在由所述伪栅极堆叠件暴露的部分所述半导体鳍上方形成应变材料;去除部分所述伪栅极堆叠件以形成暴露部分所述半导体鳍的凹部;去除位于所述凹部中的部分所述半导体鳍;以及在所述凹部中形成栅极介电材料并且填充栅极材料以形成栅极堆叠件。

2、本发明的另一实施例提供了一种制造鳍式场效应晶体管(finfet)的方法,包括:图案化半导体衬底以在所述半导体衬底中形成多个沟槽并且在所述沟槽之间形成至少一个半导体鳍;在所述沟槽中形成多个绝缘体;在部分所述半导体鳍上方和部分所述绝缘体上方形成伪栅极堆叠件以暴露所述半导体鳍的源极/漏极区,其中,所述伪栅极堆叠件包括伪栅极、伪栅极介电层和多个间隔件;在所述半导体鳍的所述源极/漏极区上方形成应变材料;去除所述伪栅极和所述伪栅极介电层以暴露所述半导体鳍的沟道区;去除所述半导体鳍的部分所述沟道区;以及在所述半导体鳍的所述沟道区上方形成栅极介电材料和栅极材料以形成栅极堆叠件。

3、本发明的又一实施例提供了一种鳍式场效应晶体管(finfet),包括:半导体衬底,包括位于所述半导体衬底上的至少一个半导体鳍,其中,所述半导体鳍包括源极/漏极区和沟道区,并且所述源极/漏极区的宽度大于所述沟道区的宽度;多个绝缘体,设置在所述半导体衬底上,所述绝缘体将所述半导体鳍夹在中间;栅极堆叠件,位于所述半导体鳍的所述沟道区上方和部分所述绝缘体上方;以及应变材料,覆盖所述半导体鳍的所述源极/漏极区。

技术特征:1.一种制造鳍式场效应晶体管(finfet)的方法,包括:

2.根据权利要求1所述的方法,其中,所述伪栅极堆叠件还包括多个间隔件。

3.根据权利要求2所述的方法,其中:

4.根据权利要求3所述的方法,其中,所述含氧气体包括臭氧(o3)或过氧化氢(h2o2)。

5.根据权利要求3所述的方法,其中,去除所述伪栅极介电层的步骤和实施所述氧化处理的步骤是原位工艺。

6.根据权利要求1所述的方法,其中,所述应变材料延伸超过所述绝缘体的顶面。

7.根据权利要求1所述的方法,还包括:

8.一种制造鳍式场效应晶体管(finfet)的方法,包括:

9.根据权利要求8所述的方法,其中,所述栅极介电层的材料包括氧化硅、氮化硅、氮氧化硅、高k介电材料或它们的组合。

10.一种鳍式场效应晶体管(finfet),包括:

技术总结鳍式场效应晶体管(FinFET)包括半导体衬底、多个绝缘体、栅极堆叠件和应变材料。半导体衬底包括位于半导体衬底上的至少一个半导体鳍。半导体鳍包括源极/漏极区和沟道区,并且源极/漏极区的宽度大于沟道区的宽度。绝缘体设置在半导体衬底上并且绝缘体将半导体鳍夹在绝缘体中间。栅极堆叠件位于半导体鳍的沟道区上方和部分绝缘体上方。应变材料覆盖半导体鳍的源极/漏极区。此外,提供了用于制造FinFET的方法。

技术研发人员:萧茹雄,吴启明,郑志成

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:技术公布日:2024/1/13