具有沟槽接触部的过电压保护器件的制作方法

本申请涉及半导体器件,并且具体地涉及过电压保护器件。

背景技术:

1、诸如晶体管、二极管、电阻器、电光器件、精密薄膜电阻器和各种集成电路等组件都对静电放电(electrostatic discharge,esd)敏感。随着电子制造商努力使器件小型化并且提高操作速度,器件对esd的易损性正在增加。器件在每个生产阶段都会受到esd损坏。为了避免在组装或操作期间脉冲对集成电路或电子器件造成损坏,esd保护器件被连接在集成电路的引脚之间,以防止电路故障或击穿。esd保护器件通过将电压维持在安全操作范围内并且变得导电以对落在安全操作范围之外的电压进行钳位来操作。

2、一些esd应用非常容易受到负esd冲击,并且在负极性中需要低钳位电压,而在正极性中需要相对较高的钳位电压。这些esd应用可能需要esd保护器件具有低寄生电容和/或小器件占地面积和/或低生产成本。用于实现这些目标的常规esd保护解决方案具有相互冲突的权衡。因此,需要提供一种具有最低可能寄生电容、最小可能封装占地面积和最低成本的esd保护器件。

技术实现思路

1、本领域技术人员在阅读以下详细描述并且查看附图之后将能够认识到其他特征和优点。

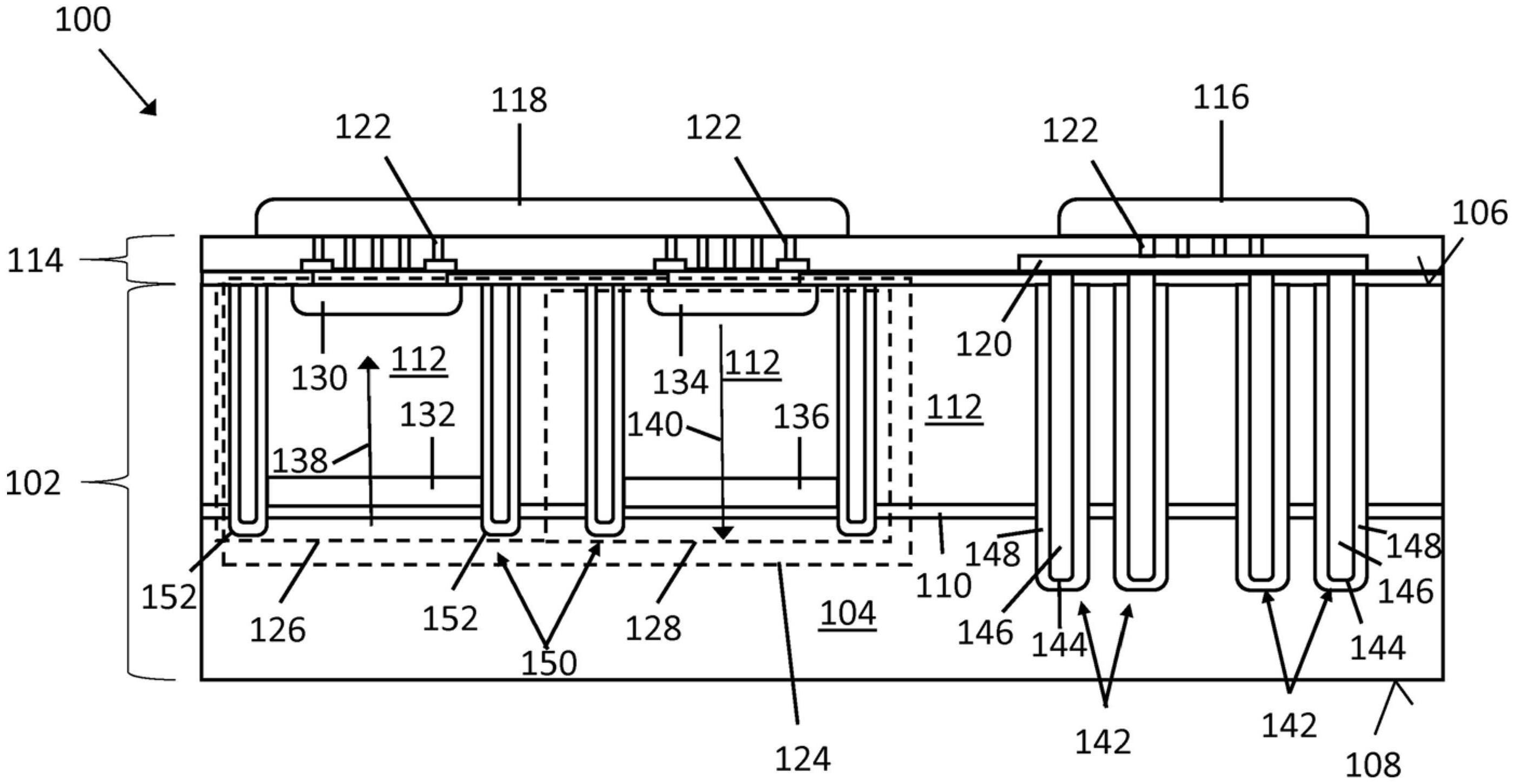

2、公开了一种过电压保护器件。根据一个实施例,该过电压保护器件包括半导体本体、设置在半导体本体的上表面之上的第一接触焊盘和第二接触焊盘、形成在半导体本体中的沟槽式连接件,以及形成在半导体本体中的竖直电压阻挡器件,该半导体本体包括设置在半导体本体的上表面之下(beneath)的衬底区域,其中沟槽式连接件包括形成在半导体本体的上表面中并且延伸到衬底区域的沟槽的金属电极,并且该金属电极设置在沟槽内,其中金属电极在第一接触焊盘与衬底区域之间形成导电连接,并且其中电压阻挡器件连接在第二接触焊盘与衬底区域之间。

3、根据另一实施例,该过电压保护器件包括半导体本体、设置在半导体本体的上表面之上的第一接触焊盘和第二接触焊盘、电连接在第一接触焊盘与衬底区域之间的沟槽式连接件,以及形成在半导体本体中并且连接在第二接触焊盘与衬底区域之间的单向电压钳位器件,该半导体本体包括设置在半导体本体的上表面之下的衬底区域。

4、根据又一实施例,该过电压保护器件包括:半导体本体,包括基极区域和设置在基极区域的上表面上的多个半导体台面(mesa);设置在半导体台面中的分开的半导体台面的上表面上的第一接触焊盘和第二接触焊盘;形成在半导体台面的下表面处的多个掺杂区域,半导体台面的下表面面向基极区域;以及形成在半导体台面中的多个沟槽式连接件,其中沟槽式连接件中的每个沟槽式连接件包括形成在半导体台面的上表面中并且延伸到基极区域的沟槽、设置在沟槽内的金属电极,以及作为沟槽的侧壁的衬里的掺杂侧壁区域,并且其中掺杂区域和沟槽式连接件共同形成在第一接触焊盘与第二接触焊盘之间的第一电压阻挡器件。

技术特征:

1.一种过电压保护器件,包括:

2.根据权利要求1所述的过电压保护器件,其中所述沟槽式连接件还包括作为所述沟槽的侧壁的衬里的掺杂侧壁区域,并且其中所述金属电极直接邻接所述掺杂侧壁区域并且经由所述掺杂侧壁区域与所述衬底区域低欧姆接触。

3.根据权利要求2所述的过电压保护器件,其中所述竖直电压阻挡器件包括第一电压阻挡器件和第二电压阻挡器件,其中所述第一电压阻挡器件和所述第二电压阻挡器件以反并联配置方式连接在所述第二接触焊盘与所述衬底区域之间,其中所述第一电压阻挡器件被布置为传导从所述衬底区域流向所述第二接触焊盘的竖直电流,其中所述第二电压阻挡器件被布置为传导从所述第二接触焊盘流向所述衬底的竖直电流。

4.根据权利要求3所述的过电压保护器件,其中所述半导体本体包括低掺杂区域和掩埋层,其中所述掩埋层布置在所述衬底区域与所述低掺杂区域之间,其中所述低掺杂区域布置在所述掩埋层与所述半导体本体的所述上表面之间,并且其中所述掩埋层具有与所述衬底区域相同的导电类型并且具有低于所述衬底区域的净掺杂剂浓度。

5.根据权利要求4所述的过电压保护器件,其中所述第一电压阻挡器件包括第一掺杂区域和第一掩埋掺杂区域,所述第一掺杂区域从所述半导体本体的所述上表面延伸到所述低掺杂区域中,所述第一掩埋掺杂区域布置在所述低掺杂区域与所述掩埋层之间,其中所述第二电压阻挡器件包括第二掺杂区域和第二掩埋掺杂区域,所述第二掺杂区域从所述半导体本体的所述上表面延伸到所述低掺杂区域中,所述第二掩埋掺杂区域布置在所述低掺杂区域与所述掩埋层之间。

6.根据权利要求3所述的过电压保护器件,其中所述过电压保护器件包括从所述半导体本体的所述上表面延伸到所述衬底区域中的电隔离结构,其中所述电隔离结构围绕并且横向电隔离所述第一电压阻挡器件和所述第二电压阻挡器件,使得所述第一电压阻挡器件的电流流过所述半导体本体的第一横向隔离区域,并且使得所述第二电压阻挡器件的电流流过所述半导体本体的第二横向隔离区域。

7.根据权利要求6所述的过电压保护器件,其中所述电隔离结构与所述沟槽式连接件分开。

8.根据权利要求6所述的过电压保护器件,其中所述电隔离结构包括所述沟槽式连接件。

9.根据权利要求8所述的过电压保护器件,其中围绕并且横向电隔离所述第二电压阻挡器件的所述沟槽式连接件被布置为使得所述第二竖直电流跨所述连接沟槽的侧壁流动。

10.一种过电压保护器件,包括:

11.根据权利要求10所述的过电压保护器件,其中所述沟槽式连接件包括形成在所述半导体本体的所述上表面中并且延伸到所述衬底区域的沟槽、设置在所述沟槽内的金属电极以及作为所述沟槽的侧壁的衬里的掺杂侧壁区域,并且其中所述金属电极直接邻接所述掺杂侧壁区域并且经由所述掺杂侧壁区域与所述衬底区域低欧姆接触。

12.根据权利要求11所述的过电压保护器件,其中所述单向电压钳位器件包括第一电压阻挡器件和第二电压阻挡器件,其中所述第一电压阻挡器件和所述第二电压阻挡器件以反并联配置方式连接在所述第二接触焊盘与所述衬底区域之间,其中在所述第一接触焊盘与所述第二接触焊盘之间的负偏置处,所述单向器件的负钳位电压由所述第二电压阻挡器件限定,并且其中在所述第一接触焊盘与所述第二接触焊盘之间的正偏置处,所述单向器件的正钳位电压由所述第一电压阻挡器件限定。

13.根据权利要求12所述的过电压保护器件,其中所述第一电压阻挡器件是开放基极双极晶体管,并且其中所述第二电压阻挡器件是pin二极管。

14.根据权利要求13所述的过电压保护器件,其中所述沟槽式连接件被布置为紧邻所述pin二极管的本征区域,使得所述pin二极管的正向电流跨所述沟槽的侧壁流动。

15.一种过电压保护器件,包括:

16.根据权利要求15所述的过电压保护器件,其中所述多个掺杂区域各自具有细长的几何形状并且彼此平行地延伸,其中所述沟槽式连接件在所述掺杂区域中的紧邻的掺杂区域之间交错。

17.根据权利要求16所述的过电压保护器件,其中所述多个掺杂区域和所述沟槽式连接件形成连接在所述第一接触焊盘与所述第二接触焊盘之间的pin二极管,并且其中所述半导体台面的在所述掺杂区域与所述掺杂侧壁区域之间的区域形成所述pin二极管的本征区域。

18.根据权利要求16所述的过电压保护器件,其中在所述第一电压阻挡器件的正向导通状态下,电流在所述半导体台面中从所述沟槽式连接件跨所述沟槽的侧壁在多个方向上流动。

19.根据权利要求15所述的过电压保护器件,其中所述第一接触焊盘设置在所述台面中的第一台面上,其中所述第二接触焊盘设置在所述台面中的第二台面上,其中所述掺杂区域和所述沟槽式连接件中的至少一些设置在所述台面中的第三台面中,所述第三台面在所述台面中的所述第一台面与所述台面中的所述第二台面之间。

20.根据权利要求15所述的过电压保护器件,其中所述掺杂区域和所述掺杂侧壁区域共同布置为形成在所述第一接触焊盘与所述第二接触焊盘之间的第二电压阻挡器件,其中所述第一电压阻挡器件和所述第二电压阻挡器件以反并联配置方式布置。

技术总结

本公开涉及具有沟槽接触部的过电压保护器件。一种过电压保护器件包括半导体本体、设置在半导体本体的上表面之上的第一接触焊盘和第二接触焊盘、形成在半导体本体中的沟槽式连接件,以及形成在半导体本体中的竖直电压阻挡器件,该半导体本体包括设置在半导体本体的上表面之下的衬底区域,其中沟槽式连接件包括形成在半导体本体的上表面中并且延伸到衬底区域的沟槽以及设置在沟槽内的金属电极,其中金属电极在第一接触焊盘与衬底区域之间形成导电连接,并且其中电压阻挡器件连接在第二接触焊盘与衬底区域之间。

技术研发人员:A·施门,I·格茨,E·泰莱特

受保护的技术使用者:英飞凌科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!