一种通过通孔刻蚀改善高阻区电阻的方法与流程

本发明涉及半导体,特别是涉及一种通过通孔刻蚀改善高阻区电阻的方法。

背景技术:

1、随着集成电路的日渐发展,对于开启电压有着越来越高的要求,而受限于集成电路结构及材质的限制,在栅极上做优化的空间已经不大,这时高阻工艺(tin)应运而生并起着分压的作用,可是随之带来的挑战是在通孔刻蚀时,由于高阻区域与其他区域存在高度差,导致高阻区域在通孔刻蚀时接触等离子体的时间过长,使tin表面受损粗糙,严重时甚至会击穿高阻区域,导致阻值异常,影响产品性能。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种通过通孔刻蚀改善高阻区电阻的方法,用于解决现有技术中通孔刻蚀导致高阻区tin表面受损,进而导致阻值,异常影响产品性能的问题。

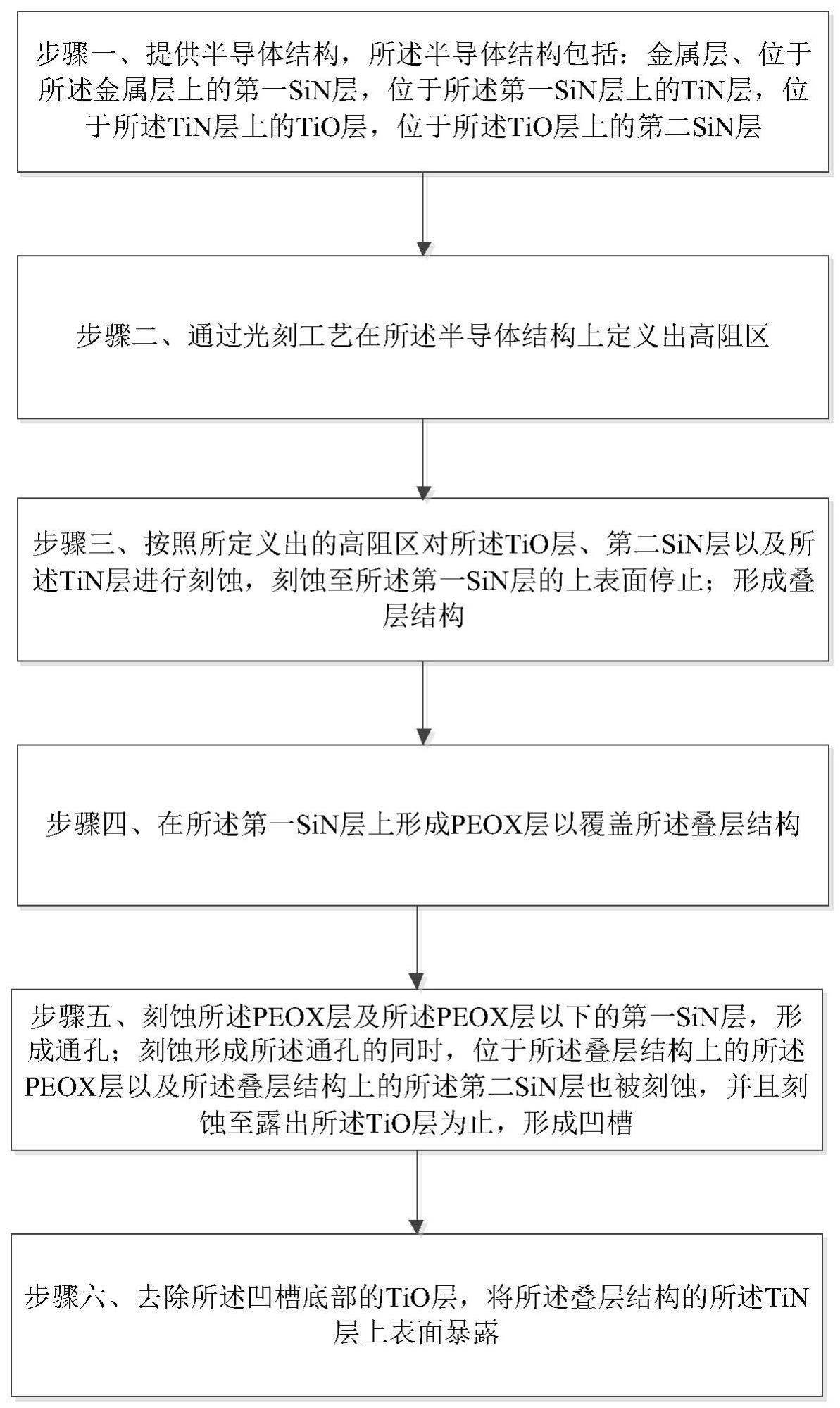

2、为实现上述目的及其他相关目的,本发明提供一种通过通孔刻蚀改善高阻区电阻的方法,至少包括:

3、步骤一、提供半导体结构,所述半导体结构包括:金属层、位于所述金属层上的第一sin层,位于所述第一sin层上的tin层,位于所述tin层上的tio层,位于所述tio层上的第二sin层;

4、步骤二、通过光刻工艺在所述半导体结构上定义出高阻区;

5、步骤三、按照所定义出的高阻区对所述tio层、第二sin层以及所述tin层进行刻蚀,刻蚀至所述第一sin层的上表面停止;形成叠层结构;

6、步骤四、在所述第一sin层上形成peox层以覆盖所述叠层结构;

7、步骤五、刻蚀所述peox层及所述peox层以下的第一sin层,形成通孔;刻蚀形成所述通孔的同时,位于所述叠层结构上的所述peox层以及所述叠层结构上的所述第二sin层也被刻蚀,并且刻蚀至露出所述tio层为止,形成凹槽;

8、步骤六、去除所述凹槽底部的tio层,将所述叠层结构的所述tin层上表面暴露。

9、优选地,步骤一中的所述金属层的材料为co。

10、优选地,步骤一中的所述tio层的厚度为

11、优选地,步骤一中的所述tio层作为通孔刻蚀的牺牲层和停止层。

12、优选地,步骤二中在所述半导体结构上定义出所述高阻区的方法为:在所述半导体结构的所述第二sin层上形成底部抗反射涂层;之后在所述底部抗反射涂层上旋涂光刻胶层;接着进行曝光和显影,被显影后的光刻胶层和底部抗反射涂层覆盖所述半导体区域为所述高阻区。

13、优选地,步骤六中通过湿法刻蚀去除所述凹槽底部的所述tio层。

14、优选地,步骤六中利用nh4oh作为湿法刻蚀剂以去除所述凹槽底部的tio层。

15、优选地,步骤六中的湿法刻蚀速率为

16、如上所述,本发明的通过通孔刻蚀改善高阻区电阻的方法,具有以下有益效果:本发明在传统工艺基础上,改变膜层结构,在tin上沉积一层50a的tio,作为通孔刻蚀时高阻区上的停止层和牺牲层,在通孔刻蚀结束后,通过湿法方式将这层牺牲层去除,通过改变高阻区域膜层结构,改善阻值。

技术特征:

1.一种通过通孔刻蚀改善高阻区电阻的方法,其特征在于,至少包括:

2.根据权利要求1所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤一中的所述金属层的材料为co。

3.根据权利要求1所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤一中的所述tio层的厚度为

4.根据权利要求1所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤一中的所述tio层作为通孔刻蚀的牺牲层和停止层。

5.根据权利要求1所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤二中在所述半导体结构上定义出所述高阻区的方法为:在所述半导体结构的所述第二sin层上形成底部抗反射涂层;之后在所述底部抗反射涂层上旋涂光刻胶层;接着进行曝光和显影,被显影后的光刻胶层和底部抗反射涂层覆盖所述半导体区域为所述高阻区。

6.根据权利要求1所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤六中通过湿法刻蚀去除所述凹槽底部的所述tio层。

7.根据权利要求6所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤六中利用nh4oh作为湿法刻蚀剂以去除所述凹槽底部的tio层。

8.根据权利要求7所述的通过通孔刻蚀改善高阻区电阻的方法,其特征在于:步骤六中的湿法刻蚀速率为

技术总结

本发明提供一种通过通孔刻蚀改善高阻区电阻的方法,半导体结构包括金属层、第一SiN层、TiN层、TiO层、第二SiN层;通过光刻定义出高阻区;按照定义出的高阻区对TiO层、第二SiN层及TiN层进行刻蚀,形成叠层结构;在第一SiN层上形成PEOX层以覆盖叠层结构;刻蚀PEOX层及PEOX层以下的第一SiN层形成通孔;刻蚀形成通孔的同时,位于叠层结构上的PEOX层以及叠层结构上的第二SiN层也被刻蚀形成凹槽;去除凹槽底部的TiO层,将叠层结构的TiN层上表面暴露。本发明在传统工艺基础上,改变膜层结构,在TiN上沉积一层50A的TiO,作为通孔刻蚀时高阻区上的停止层和牺牲层,在通孔刻蚀结束后,将牺牲层去除,通过改变高阻区域膜层结构,改善阻值。

技术研发人员:黄山

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!