CMOS结构及其制造方法与流程

本公开涉及具有背面配电网络(bspdn)的堆叠半导体器件及其制造方法的各种实施方式。

背景技术:

1、半导体器件具有各种不同的配置。两种类型的半导体器件包括非堆叠器件架构和堆叠器件架构。相关技术的非堆叠器件架构典型地包括nmos器件区、在nmos器件区之上的pmos器件区、在nmos器件区和pmos器件区之间的中段(mol)区、在pmos器件区之上的电源轨区(vdd)、以及在nmos器件区下面的电源轨区(gnd)。相关技术的堆叠器件架构典型地包括堆叠在nmos器件之上的pmos器件,并且pmos器件和nmos器件中的每个包括在相应器件下面的单独的电压源供应(vss)电源轨和在相应器件之上的vdd电源轨。此外,相关技术的堆叠器件架构典型地包括在堆叠nmos器件和pmos器件之上的正面配电网络(pdn)网格和正面信号布线线路。然而,在nmos器件和pmos器件之上提供pdn网格和信号布线线路两者导致布线拥塞,从而限制块面积缩放。

技术实现思路

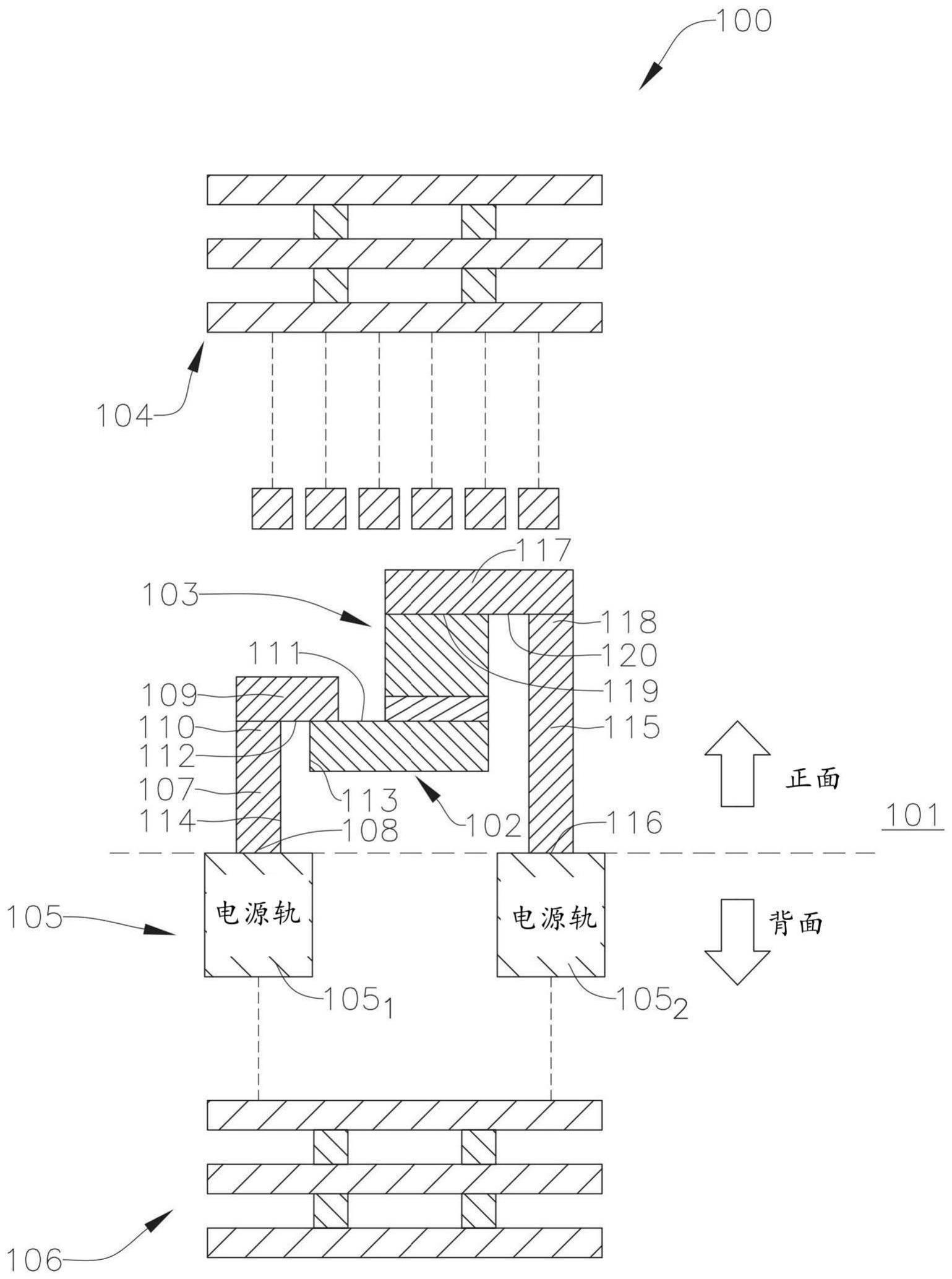

1、本公开涉及cmos结构的各种实施方式。在一个实施方式中,cmos结构包括晶片、在晶片的正面的第一半导体器件和堆叠在第一半导体器件上的第二半导体器件、联接到第一半导体器件和第二半导体器件的在晶片的背面的电源轨、联接到电源轨的在晶片的背面的背面配电网络(pdn)网格、以及联接到第一半导体器件和第二半导体器件并且在第一半导体器件和第二半导体器件之上的在晶片的正面的正面信号布线线路。

2、本公开还涉及制造cmos器件的方法的各种实施方式。在一个实施方式中,该方法包括在包括蚀刻停止层的硅基板上以块状材料形成用于下半导体器件和上半导体器件的沟道、形成从下半导体器件到蚀刻停止层的第一连接、形成从上半导体器件到蚀刻停止层的第二连接、后段形成联接到下半导体器件和上半导体器件的信号线、经由接合界面将载体晶片接合到信号线上、执行晶片翻转、去除硅基板的一部分和蚀刻停止层、形成连接到第一连接和第二连接的电源轨、以及形成联接到电源轨的背面配电网络网格使得背面配电网络网格和信号线在硅基板的相反侧。

3、提供该

技术实现要素:

以介绍下面在详细描述中进一步描述的构思的选择。该发明内容不旨在识别所要求保护的主题的关键或基本特征,也不旨在用于限制所要求保护的主题的范围。一个或更多个所描述的特征可以与一个或更多个其他所描述的特征组合以提供可工作的器件。

技术特征:

1.一种cmos结构,包括:

2.根据权利要求1所述的cmos结构,还包括:

3.根据权利要求2所述的cmos结构,其中所述第一电源通路与所述第一半导体器件的侧面相邻。

4.根据权利要求2所述的cmos结构,其中所述第一电源通路与所述第一半导体器件的侧面间隔开。

5.根据权利要求1所述的cmos结构,还包括:

6.根据权利要求5所述的cmos结构,其中所述第一电源通路包括在所述第一半导体器件下面的较窄部分和在所述第一半导体器件之上的较宽部分。

7.根据权利要求1所述的cmos结构,还包括:

8.根据权利要求1所述的cmos结构,还包括:

9.根据权利要求1所述的cmos结构,其中所述第一半导体器件从所述第二半导体器件横向偏移。

10.一种制造cmos结构的方法,所述方法包括:

11.根据权利要求10所述的方法,其中形成所述第一连接包括:

12.根据权利要求11所述的方法,其中形成所述第二连接包括:

13.根据权利要求10所述的方法,其中形成所述第一连接包括形成第一电源通路,所述第一电源通路在所述下半导体器件的上表面上并且从所述下半导体器件延伸到所述蚀刻停止层。

14.根据权利要求13所述的方法,其中所述第一电源通路包括在所述下半导体器件之上的较宽部分和在所述下半导体器件下面的较窄部分。

15.根据权利要求14所述的方法,其中形成所述第二连接包括:

16.根据权利要求10所述的方法,其中形成所述第一连接包括形成从所述下半导体器件的下表面直接延伸到所述蚀刻停止层的第一电源通路。

17.根据权利要求16所述的方法,其中形成所述第二连接包括:

18.根据权利要求10所述的方法,其中形成所述第一连接包括形成从所述下半导体器件的下表面直接延伸到所述蚀刻停止层的第一电源通路。

19.根据权利要求18所述的方法,其中形成所述第二连接包括形成从所述上半导体器件的下表面直接延伸到所述蚀刻停止层的第二电源通路。

技术总结

本公开涉及CMOS结构及其制造方法,该CMOS结构包括晶片、在晶片的正面的第一半导体器件和第二半导体器件、在晶片的背面的电源轨、在晶片的背面的背面配电网络(PDN)网格、以及在晶片的正面在第一半导体器件和第二半导体器件之上的正面信号布线线路。第二半导体器件堆叠在第一半导体器件上,背面PDN网格联接到电源轨,电源轨联接到第一半导体器件和第二半导体器件。

技术研发人员:朴玺韩,李昇映,黄寅灿

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!