半导体装置及其制造方法与流程

本公开实施例是有关于半导体技术,且特别是有关于半导体装置及其制造方法。

背景技术:

1、随着半导体产业追求更高装置密度、更高效能及更低成本的过程中进入了纳米技术制程节点,制造及设计方面的挑战导致了三维设计的发展,例如多栅极场效晶体管(field effect transistor,fet),多栅极场效晶体管包含鳍式场效晶体管(fin fet,finfet)及全绕式栅极(gate-all-around,gaa)场效晶体管。电流可能从鳍式场效晶体管或全绕式栅极场效晶体管的源极或漏极泄漏至鳍式场效晶体管或全绕式栅极场效晶体管下方的基底,且可能导致电力损失,并且还可能使基底和在基底中制造的电子装置升温。在整个基底区域中,使用绝缘层上覆硅(silicon on insulator,soi)基底来形成电流的阻障,以从基底的顶部移动到基底的底部,并防止/减少从鳍式场效晶体管或全绕式栅极场效晶体管的源极或漏极的漏电流。绝缘层上覆硅基底很昂贵,并且强烈推荐进行局部隔离,例如在源极或漏极下。

技术实现思路

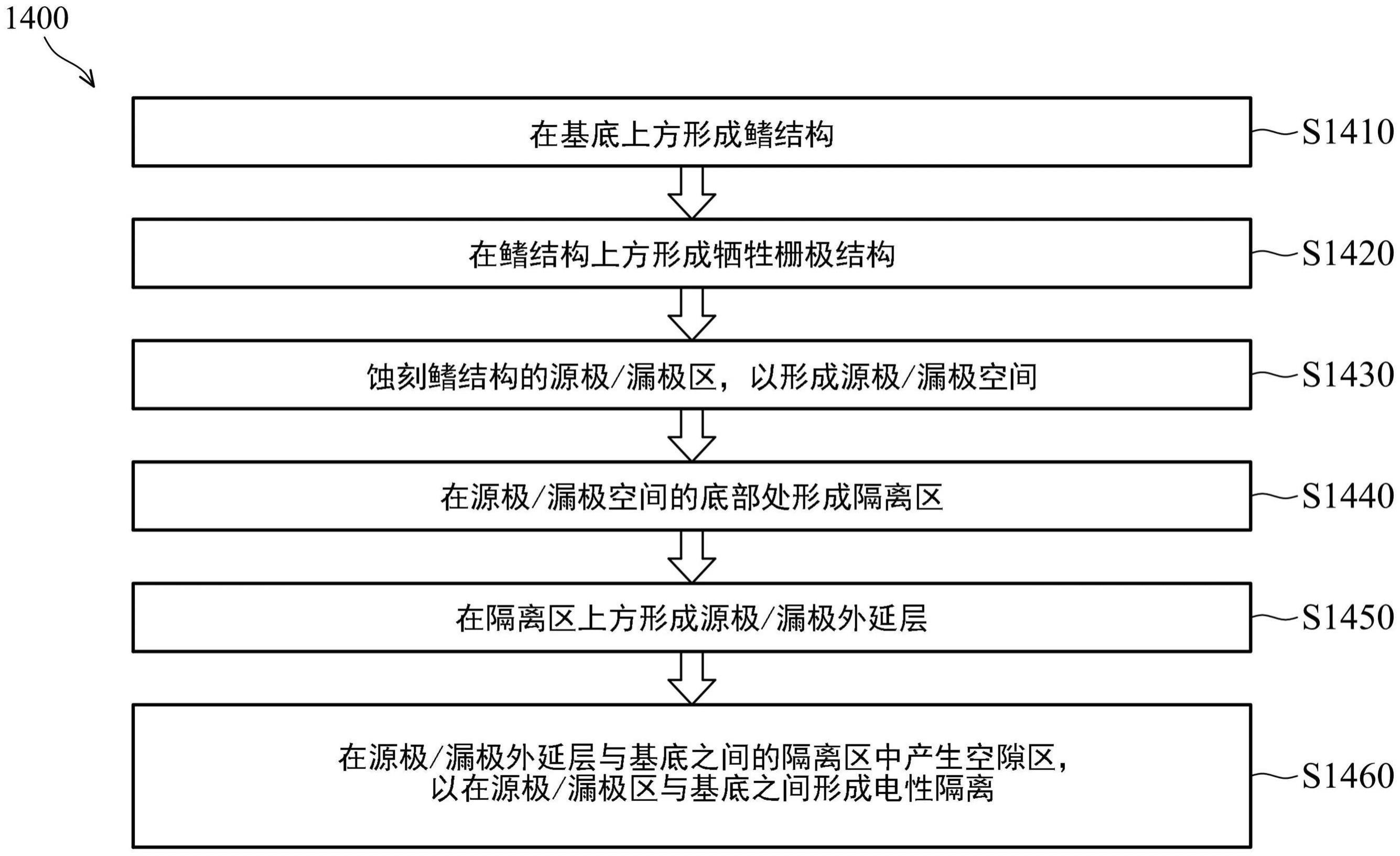

1、在一些实施例中,提供半导体装置的制造方法,此方法包含形成鳍结构,鳍结构具有交替堆叠于基底上方的多个第一半导体层及多个第二半导体层;在鳍结构上方形成牺牲栅极结构;蚀刻鳍结构未被牺牲栅极结构覆盖的源极/漏极区,进而形成源极/漏极空间;在源极/漏极空间的底部处形成隔离区;在源极/漏极空间中的隔离区上方形成源极/漏极外延层;以及在源极/漏极外延层与基底之间的隔离区中产生空隙区。

2、在一些实施例中,提供半导体装置的制造方法,此方法包含形成鳍结构,鳍结构具有交替堆叠的多个第一半导体层及多个第二半导体层;在鳍结构上方形成牺牲栅极结构;蚀刻鳍结构未被牺牲栅极结构覆盖的源极/漏极区,进而形成源极/漏极空间;通过横向蚀刻通过源极/漏极空间的多个第一半导体层,在多个第一半导体层与源极/漏极空间相交的每个第一半导体层的末端形成多个空腔;在多个第一半导体层的多个空腔中形成介电材料制成的内部间隙壁;在源极/漏极区的底部处形成电性隔离区,其中电性隔离区产生电性阻障;以及在源极/漏极空间中的电性隔离区上方形成掺杂源极/漏极外延层。

3、在另外一些实施例中,提供半导体装置,半导体装置包含多个半导体纳米结构,设置于基底上方;电性隔离区,包括设置于源极/漏极区中的该基底上方的空隙;源极/漏极外延层,接触多个半导体纳米结构,并设置于源极/漏极区中的电性隔离区上方,其中源极/漏极外延层设置于空隙上方;栅极介电层,设置于多个半导体纳米结构的每个通道区上并环绕多个半导体纳米结构的每个通道区;以及栅极电极层,设置于栅极介电层上,并环绕多个半导体纳米结构的每个通道区。

技术特征:

1.一种半导体装置的制造方法,包括:

2.如权利要求1所述的半导体装置的制造方法,其中形成该隔离区的步骤更包括:在该隔离区中形成一介电区,其中该空隙区产生于该源极/漏极外延层与该介电区之间。

3.如权利要求1所述的半导体装置的制造方法,其中形成该隔离区的步骤更包括:在该隔离区中形成一绝缘层,其中该空隙区产生于该源极/漏极外延层与该绝缘层之间。

4.如权利要求1所述的半导体装置的制造方法,更包括:

5.如权利要求4所述的半导体装置的制造方法,其中该隔离区包括该介电层及该空隙区。

6.如权利要求1所述的半导体装置的制造方法,其中形成该隔离区的步骤更包括:在该隔离区中的一未掺杂外延层上方形成一绝缘层,其中该空隙区产生于该源极/漏极外延层与该绝缘层之间。

7.如权利要求1所述的半导体装置的制造方法,其中形成该隔离区的步骤更包括:

8.一种半导体装置的制造方法,包括:

9.一种半导体装置,包括:

10.如权利要求9所述的半导体装置的制造方法,其中该空隙接触该源极/漏极外延层。

技术总结

本公开涉及半导体装置及其制造方法。在半导体装置的制造方法中,形成鳍结构,鳍结构具有交替堆叠于基底上方的第一半导体层及第二半导体层;在鳍结构上方形成牺牲栅极结构;蚀刻鳍结构未被牺牲栅极结构覆盖的源极/漏极区,进而形成源极/漏极空间;在源极/漏极空间的底部处形成隔离区;在源极/漏极空间中的隔离区上方形成源极/漏极外延层,以及在源极/漏极外延层与基底之间的隔离区中产生空隙区,使得源极/漏极区和基底之间产生电性隔离。

技术研发人员:李宗霖,林大文,叶致锴

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!