半导体器件的制备方法与流程

本发明涉及半导体,尤其涉及一种半导体器件的制备方法。

背景技术:

1、在半导体器件的制备工艺中,在衬底上形成栅极结构,在栅极结构两侧的衬底中分别形成源区和漏区,在将栅极结构、源区和漏区电性引出时,形成介质层覆盖栅极结构和衬底,然后刻蚀介质层形成栅极接触孔、源极接触孔和漏极接触孔。由于栅极结构的顶部高于衬底的表面,栅极接触孔和源极接触孔与漏极接触孔的深度不同,在同时刻蚀形成栅极接触孔、源极接触孔和漏极接触孔时,刻蚀量差异(尤其刻蚀量相差较大)容易造成栅极吃穿的问题。虽然在现有技术中会在栅极结构和衬底上形成阻挡层,阻挡层作为刻蚀停止层,来预防栅极吃穿的问题,但不能完全避免栅极吃穿的现象发生。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制备方法,能够有效避免因刻蚀量差异导致的栅极吃穿的问题。

2、为了达到上述目的,本发明提供了一种半导体器件的制备方法,包括:

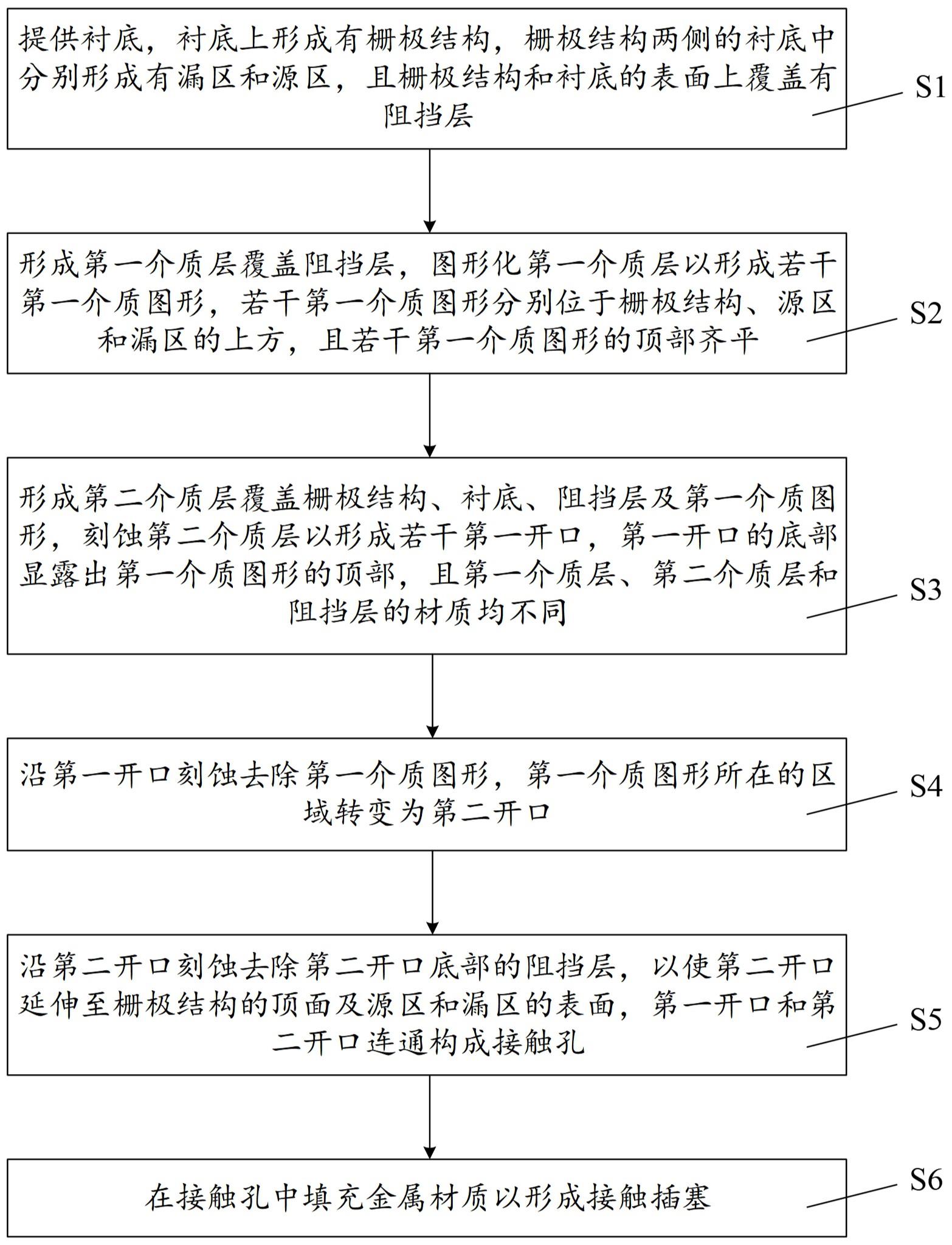

3、提供衬底,所述衬底上形成有栅极结构,所述栅极结构两侧的衬底中分别形成有漏区和源区,且所述栅极结构和所述衬底的表面上覆盖有阻挡层;

4、形成连接材料层覆盖所述阻挡层,图形化所述连接材料层以形成若干连接图形,若干所述连接图形分别位于所述栅极结构、所述源区和所述漏区的上方,且若干所述连接图形的顶部齐平;

5、形成介质层覆盖所述栅极结构、所述衬底、所述阻挡层及所述连接图形,刻蚀所述介质层以形成若干第一开口,所述第一开口的底部显露出所述连接图形的顶部,且所述连接材料层、所述介质层和所述阻挡层的材质均不同;

6、沿所述第一开口刻蚀去除所述连接图形,所述连接图形所在的区域转变为第二开口;

7、沿所述第二开口刻蚀去除所述第二开口底部的阻挡层,以使所述第二开口延伸至所述栅极结构的顶面及所述源区和所述漏区的表面,所述第一开口和所述第二开口连通构成接触孔;以及,

8、在所述接触孔中填充金属材质以形成接触插塞。

9、可选的,所述第一开口的底部与所述连接图形的顶部完全对准。

10、可选的,所述阻挡层的材质包括氮化硅,所述介质层的材质包括氧化硅。

11、可选的,所述连接材料层的材质包括多晶硅或无定型碳。

12、可选的,当所述连接材料层的材质为多晶硅时,采用湿法刻蚀工艺刻蚀去除所述连接图形。

13、可选的,所述湿法刻蚀工艺的刻蚀剂包括氨水。

14、可选的,当所述连接材料层的材质为无定型碳时,采用干法刻蚀工艺刻蚀去除所述连接图形。

15、可选的,所述干法刻蚀工艺的刻蚀气体包括氧气。

16、可选的,刻蚀所述介质层以形成若干第一开口、刻蚀去除所述连接图形以及刻蚀去除所述第二开口底部的阻挡层均在同一工艺腔内进行。

17、可选的,形成所述连接材料层覆盖所述阻挡层且覆盖至所述栅极结构的上方之后,执行研磨工艺以使所述连接材料层的顶部平坦。

18、在本发明提供的半导体器件的制备方法中,提供衬底,衬底上形成有栅极结构,栅极结构两侧的衬底中分别形成有漏区和源区,且栅极结构和衬底的表面上覆盖有阻挡层;形成连接材料层覆盖阻挡层,图形化连接材料层以形成若干连接图形,若干连接图形分别位于栅极结构、源区和漏区的上方,且若干连接图形的顶部齐平;形成介质层覆盖栅极结构、衬底、阻挡层及连接图形,刻蚀介质层以形成若干第一开口,第一开口的底部显露出所述连接图形的顶部,且连接材料层、介质层和阻挡层的材质均不同;沿第一开口刻蚀去除连接图形,连接图形所在的区域转变为第二开口;沿第二开口刻蚀去除第二开口底部的阻挡层,以使第二开口延伸至栅极结构的顶面及源区和漏区的表面,第一开口和第二开口连通构成接触孔;以及,在接触孔中填充金属材质以形成接触插塞。本发明中先形成若干连接图形,再形成第一开口显露出连接图形,由于若干连接图形的顶部齐平形成第一开口的刻蚀量相同;进而去除连接图形,由于连接材料层、介质层和阻挡层的材质均不同,可选择相对于介质层和阻挡层蚀刻选择比更大的材料作为连接材料层,或可选择采用非等离子体刻蚀工艺去除连接图形,避免对阻挡层产生过蚀刻的情况,即实现刻蚀去除连接图形时不会对介质层和阻挡层产生较大的影响;随后刻蚀去除第二开口底部的阻挡层,第一开口和第二开口连通构成接触孔,能够有效避免现有技术中因刻蚀量差异导致的栅极吃穿的问题。

技术特征:

1.一种半导体器件的制备方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制备方法,其特征在于,所述第一开口的底部与所述连接图形的顶部完全对准。

3.如权利要求1所述的半导体器件的制备方法,其特征在于,所述阻挡层的材质包括氮化硅,所述介质层的材质包括氧化硅。

4.如权利要求1或3所述的半导体器件的制备方法,其特征在于,所述连接材料层的材质包括多晶硅或无定型碳。

5.如权利要求4所述的半导体器件的制备方法,其特征在于,当所述连接材料层的材质为多晶硅时,采用湿法刻蚀工艺刻蚀去除所述连接图形。

6.如权利要求5所述的半导体器件的制备方法,其特征在于,所述湿法刻蚀工艺的刻蚀剂包括氨水。

7.如权利要求4所述的半导体器件的制备方法,其特征在于,当所述连接材料层的材质为无定型碳时,采用干法刻蚀工艺刻蚀去除所述连接图形。

8.如权利要求7所述的半导体器件的制备方法,其特征在于,所述干法刻蚀工艺的刻蚀气体包括氧气。

9.如权利要求8所述的半导体器件的制备方法,其特征在于,刻蚀所述介质层以形成若干第一开口、刻蚀去除所述连接图形以及刻蚀去除所述第二开口底部的阻挡层均在同一工艺腔内进行。

10.如权利要求1所述的半导体器件的制备方法,其特征在于,形成所述连接材料层覆盖所述阻挡层且覆盖至所述栅极结构的上方之后,执行研磨工艺以使所述连接材料层的顶部平坦。

技术总结

本发明提供了一种半导体器件的制备方法,包括:提供衬底,衬底上形成有栅极结构,栅极结构两侧的衬底中分别形成有漏区和源区,且栅极结构和衬底的表面上覆盖有阻挡层;形成连接材料层覆盖阻挡层,图形化连接材料层以形成若干连接图形,且若干连接图形的顶部齐平;形成介质层,刻蚀介质层以形成若干第一开口;沿第一开口刻蚀去除连接图形,连接图形所在的区域转变为第二开口;沿第二开口刻蚀去除第二开口底部的阻挡层,第一开口和第二开口连通构成接触孔;以及,在接触孔中填充金属材质以形成接触插塞。本发明能够有效避免因刻蚀量差异导致的栅极吃穿的问题。

技术研发人员:朱小锋

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!