半导体元件及其作方法与流程

本发明涉及一种制作半导体元件的方法,尤其是涉及一种于单扩散隔离(singlediffusion break,sdb)结构上制备高压元件的方法。

背景技术:

1、近年来,随着场效晶体管(field effect transistors,fets)元件尺寸持续地缩小,现有平面式(planar)场效晶体管元件的发展已面临制作工艺上的极限。为了克服制作工艺限制,以非平面(non-planar)的场效晶体管元件,例如鳍状场效晶体管(fin fieldeffect transistor,fin fet)元件来取代平面晶体管元件已成为目前的主流发展趋势。由于鳍状场效晶体管元件的立体结构可增加栅极与鳍状结构的接触面积,因此,可进一步增加栅极对于载流子沟道区域的控制,从而降低小尺寸元件面临的漏极引发能带降低(draininduced barrier lowering,dibl)效应,并可以抑制短沟道效应(short channel effect,sce)。再者,由于鳍状场效晶体管元件在同样的栅极长度下会具有更宽的沟道宽度,因而可获得加倍的漏极驱动电流。甚而,晶体管元件的临界电压(threshold voltage)也可通过调整栅极的功函数而加以调控。

2、在现行的鳍状场效晶体管元件制作工艺中,鳍状结构周围形成浅沟隔离后通常会以蚀刻方式去除部分鳍状结构与浅沟隔离形成凹槽,然后填入绝缘物以形成单扩散隔离结构并将鳍状结构分隔为两部分。然而现今单扩散隔离结构与金属栅极的制作工艺在搭配上仍存在许多问题,因此如何改良现有鳍状场效晶体管制作工艺与架构即为现今一重要课题。

技术实现思路

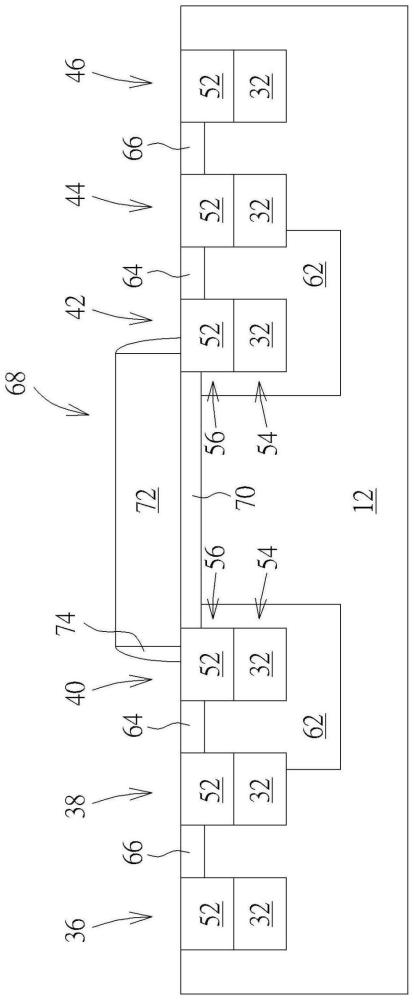

1、本发明一实施例揭露一种制作半导体元件的方法,其主要先形成一鳍状结构于基底上,然后形成一第一凹槽以及一第二凹槽于该鳍状结构内,形成一第一介电层于该第一凹槽以及该第二凹槽内,去除部分该第一介电层,形成一第二介电层于该第一凹槽以及该第二凹槽内以形成一第一单扩散隔离结构以及一第二单扩散隔离结构,再形成一栅极结构于该鳍状结构、该第一单扩散隔离结构以及一第二单扩散隔离结构上。

2、本发明另一实施例揭露一种半导体元件,其主要包含一鳍状结构设于基底上,第一单扩散隔离结构以及第二单扩散隔离结构设于基底内以及一栅极结构设于鳍状结构、第一单扩散隔离结构以及第二单扩散隔离结构上。其中各第一单扩散隔离结构以及第二单扩散隔离结构包含一下半部与一上半部且该下半部以及该上半部包含不同材料。

技术特征:

1.一种制作半导体元件的方法,其特征在于,包含:

2.如权利要求1所述的方法,还包含:

3.如权利要求2所述的方法,还包含形成第五单扩散隔离结构以及第六单扩散隔离结构于该第三单扩散隔离结构以及该第四单扩散隔离结构两侧。

4.如权利要求2所述的方法,其中该第一单扩散隔离结构深度大于该第三单扩散隔离结构深度。

5.如权利要求1所述的方法,还包含:

6.如权利要求5所述的方法,还包含形成第五单扩散隔离结构以及第六单扩散隔离结构于该第三单扩散隔离结构以及该第四单扩散隔离结构两侧。

7.如权利要求5所述的方法,其中该第一单扩散隔离结构深度大于该第三单扩散隔离结构深度。

8.如权利要求1所述的方法,其中该第一介电层以及该第二介电层包含不同材料。

9.如权利要求1所述的方法,其中该第一介电层包含氧化硅。

10.如权利要求1所述的方法,其中该第二介电层包含氮化硅。

11.一种半导体元件,其特征在于,包含:

12.如权利要求11所述的半导体元件,还包含:

13.如权利要求12所述的半导体元件,还包含第五单扩散隔离结构以及第六单扩散隔离结构,设于该第三单扩散隔离结构以及该第四单扩散隔离结构两侧。

14.如权利要求12所述的半导体元件,其中该第一单扩散隔离结构深度大于该第三单扩散隔离结构深度。

15.如权利要求11所述的半导体元件,还包含:

16.如权利要求15所述的半导体元件,还包含第五单扩散隔离结构以及第六单扩散隔离结构,设于该第三单扩散隔离结构以及该第四单扩散隔离结构两侧。

17.如权利要求15所述的半导体元件,其中该第一单扩散隔离结构深度大于该第三单扩散隔离结构深度。

18.如权利要求11所述的半导体元件,其中该下半部包含氧化硅。

19.如权利要求11所述的半导体元件,其中该上半部包含氮化硅。

技术总结

本发明公开一种半导体元件及其作方法,其中该制作半导体元件的方法为,主要先形成一鳍状结构于基底上,然后形成一第一凹槽以及一第二凹槽于该鳍状结构内,形成一第一介电层于该第一凹槽以及该第二凹槽内,去除部分该第一介电层,形成一第二介电层于该第一凹槽以及该第二凹槽内以形成一第一单扩散隔离结构以及一第二单扩散隔离结构,再形成一栅极结构于该鳍状结构、该第一单扩散隔离结构以及一第二单扩散隔离结构上。

技术研发人员:罗广钰,陆俊岑,张仲甫,吴智善,林毓翔,张韡浩

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/9/23

- 还没有人留言评论。精彩留言会获得点赞!