具有复合基板的衬底、半导体器件及衬底的制备方法与流程

本公开属于半导体,特别涉及一种具有复合基板的衬底、半导体器件及衬底的制备方法。

背景技术:

1、衬底是半导体器件的重要组成部分之一,用于为外延层的生长提供基础。

2、在相关技术中,对于三代半导体的衬底来说,通常有gan-on-si的形式、gan-on-sic的形式、gan-on-gan的形式等。

3、然而,在这些衬底形式中,均不利于制备大尺寸工程复合衬底。

技术实现思路

1、本公开实施例提供了一种具有复合基板的衬底、半导体器件及衬底的制备方法,能够有效的解决晶格失配的问题。所述技术方案如下:

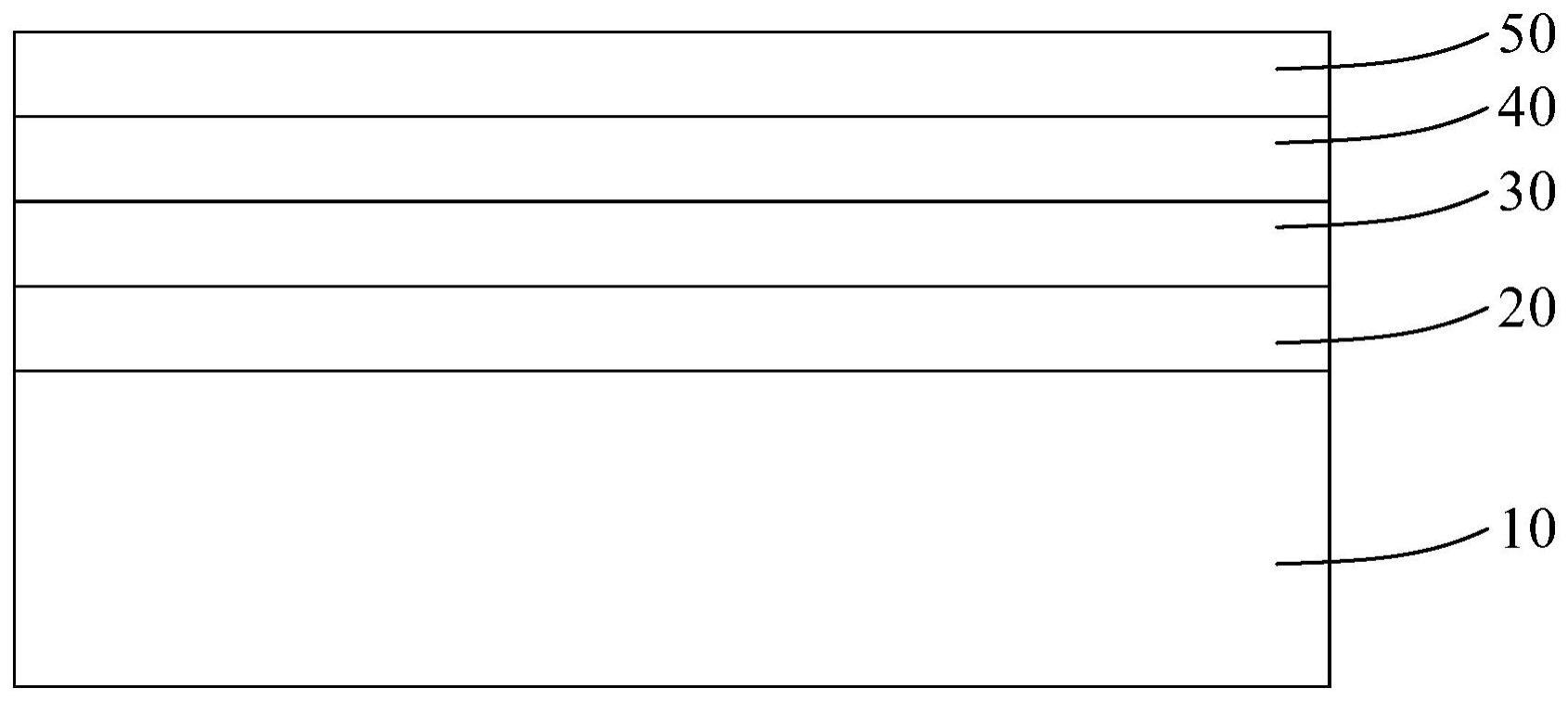

2、第一方面,本公开实施例提供了一种衬底,包括复合基板;

3、所述复合基板包括基板主体和zno层,所述zno层位于所述基板主体的一面。

4、在本公开的一种实现方式中,所述zno层包括多个zno颗粒;

5、多个所述zno颗粒敷设在所述基板主体的一面,以形成贴合在所述基板主体上的薄膜。

6、在本公开的另一种实现方式中,所述zno层的厚度为所述复合基板的厚度的1%~5%。

7、在本公开的又一种实现方式中,所述衬底还包括sio2绝缘层;

8、所述sio2绝缘层位于所述zno层背向所述基板主体的一面,所述sio2绝缘层的厚度为50~300nm。

9、在本公开的又一种实现方式中,所述衬底还包括si应力调控层;

10、所述si应力调控层位于所述sio2绝缘层背向所述复合基板的一面,所述si应力调控层的厚度为200~500nm。

11、在本公开的又一种实现方式中,所述衬底还包括aln缓冲层;

12、所述aln缓冲层位于所述si应力调控层背向所述复合基板的一面,所述aln缓冲层的厚度为100~300nm。

13、在本公开的又一种实现方式中,所述衬底还包括aln/gan超晶格层;

14、所述aln/gan超晶格层位于所述aln缓冲层背向所述复合基板的一面,所述aln/gan超晶格层的厚度为50~200nm。

15、第二方面,本公开实施例提供了一种半导体器件,包括第一方面所述的衬底。

16、第三方面,本公开实施例提供了一种衬底的制备方法,包括:

17、提供一基板主体;

18、在所述基板主体的一面制备zno层。

19、在本公开的又一种实现方式中,制备所述zno层包括:

20、将制备温度设置为1000~1300℃,制备压力设置为100~300mbar,制备环境设置为小于1pa的真空环境。

21、本公开实施例提供的技术方案带来的有益效果是:

22、由于本公开实施例提供的衬底包括复合基板,而复合基板包括基板主体和zno层。其中,基板主体能够起到稳固的支承作用,保证了复合基板的结构稳定性,从而使得衬底能够稳定的支承外延层,为外延层的生长提供可靠的基础。zno层则利用zno的自身特性,提高了复合基板的整体延展性,有效的减少了衬底的翘曲,有利于制备大尺寸工程复合衬底。

23、也就是说,通过将基板主体和zno层进行复合,使得复合基板既能够具有较强的支承稳定性,又能够具有较强的整体延展性。

技术特征:

1.一种衬底,其特征在于,包括复合基板(10);

2.根据权利要求1所述的衬底,其特征在于,所述zno层(120)包括多个zno颗粒(121);

3.根据权利要求1所述的衬底,其特征在于,所述zno层(120)的厚度为所述复合基板(10)的厚度的1%~5%。

4.根据权利要求1所述的衬底,其特征在于,所述衬底还包括sio2绝缘层(20);

5.根据权利要求4所述的衬底,其特征在于,所述衬底还包括si应力调控层(30);

6.根据权利要求5所述的衬底,其特征在于,所述衬底还包括aln缓冲层(40);

7.根据权利要求6所述的衬底,其特征在于,所述衬底还包括aln/gan超晶格层(50);

8.一种半导体器件,其特征在于,包括权利要求1至7任一项所述的衬底。

9.一种衬底的制备方法,其特征在于,包括:

10.根据权利要求9所述的制备方法,其特征在于,制备所述zno层(120)包括:

技术总结

本公开公开了一种具有复合基板的衬底、半导体器件及衬底的制备方法,属于半导体技术领域。该衬底包括复合基板;复合基板包括基板主体和ZnO层,ZnO层位于基板主体的一面。本公开能够有效的解决晶格失配的问题。

技术研发人员:葛永晖,肖云飞,陆香花,张奕,梅劲

受保护的技术使用者:华灿光电(浙江)有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!