一种三维堆叠芯片的封装结构及其封装方法与流程

本发明涉及半导体集成电路封装,尤其涉及一种三维堆叠芯片的封装结构及其封装方法。

背景技术:

1、目前,芯片堆叠的结构有多种,现有对芯片进行堆叠封装时,需要将两个芯片分别独立进行封装,然后将独立封装后的两个封装体叠加起来,最后得到封装成品。现有将两个封装体直接叠加起来的结构,成品总厚度是两个封装后芯片的厚度,最后得到的封装体的厚度较厚,难以满足市场中手机、电脑等终端客户薄型化的需求。此外,现有封装结构中两个封装体是通过锡球进行连接的,如果将锡球间距调整到很小,则封装成本会大幅上升。

技术实现思路

1、针对背景技术提出的问题,本发明的目的在于提出一种三维堆叠芯片的封装结构,能够降低封装体的厚度,提高io 密度,有效降低成本,解决了现有三维封装体堆叠后厚度较厚,难以满足市场薄型化的需求,且封装成本高的技术问题。

2、本发明的另一目的在于提出一种三维堆叠芯片的封装方法,能够封装得到所述三维堆叠芯片的封装结构,有效降低封装体的厚度,降低封装成本,解决现有封装方法制作的三维封装体堆叠后厚度较厚、封装成本高的技术问题。

3、为达此目的,本发明采用以下技术方案:

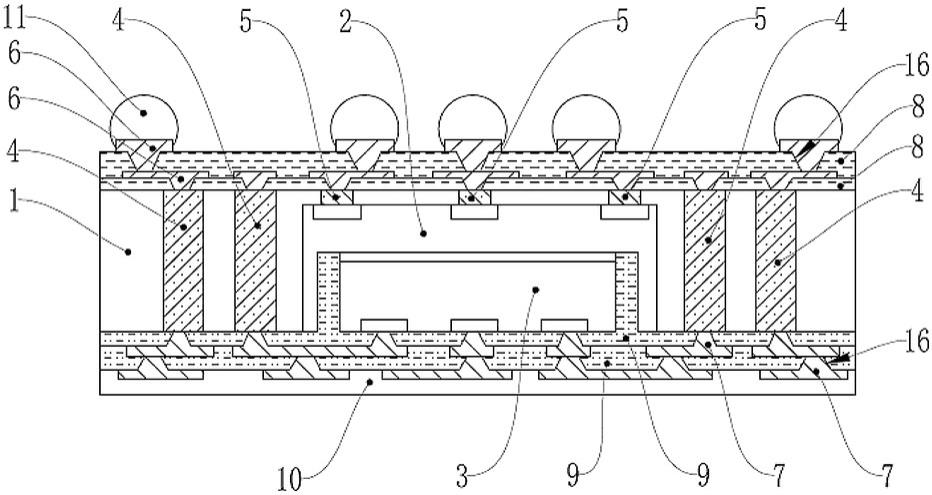

4、一种三维堆叠芯片的封装结构,包括封装体、第一芯片、第二芯片、第一导通连接件、第二导通连接件、至少一层第一再布线层和至少一层第二再布线层;

5、所述封装体包封所述第一芯片,所述第一导通连接件和所述第二导通连接件均设置于所述封装体中,所述第二导通连接件的一端与所述第一芯片的引脚连接,所述第二导通连接件的另一端与所述第一再布线层连接;

6、所述第一芯片的远离所述第二导通连接件的一端设有凹槽,所述第二芯片嵌设于所述凹槽内,且所述第二芯片的引脚位于所述第二芯片的远离所述第二导通连接件的一侧,所述第二芯片的引脚与所述第二再布线层连接,所述第一导通连接件的一端与所述第一再布线层连接,所述第一导通连接件的另一端与所述第二再布线层连接。

7、更进一步说明,所述凹槽延伸至所述封装体。

8、更进一步说明,还包括至少一层第一绝缘层和至少一层第二绝缘层;

9、所述第一绝缘层覆盖于所述封装体的表面,且位于所述第一再布线层与所述封装体之间;

10、所述第二绝缘层覆盖于所述封装体的表面,且填充于所述凹槽内,所述第二绝缘层位于所述第二再布线层与所述封装体之间。

11、更进一步说明,所述第一再布线层、所述第二再布线层、所述第一绝缘层和所述第二绝缘层分别设置有两层;

12、第一层所述第一绝缘层覆盖于所述封装体的表面,且第一层所述第一绝缘层位于第一层所述第一再布线层与所述封装体之间,第二层所述第一绝缘层覆盖于第一层所述第一再布线层的表面,且第二层所述第一绝缘层位于第二层所述第一再布线层与第一层所述第一再布线层之间;

13、第一层所述第二绝缘层覆盖于所述封装体的表面并填充于所述凹槽内,且第一层所述第二绝缘层位于第一层所述第二再布线层与所述封装体之间,第二层所述第二绝缘层覆盖于第一层所述第二再布线层的表面,且第二层所述第二绝缘层位于第二层所述第二再布线层与第一层所述第二再布线层之间。

14、更进一步说明,还包括防护层,所述防护层设置于所述第二再布线层的远离所述第一再布线层的一侧。

15、更进一步说明,还包括锡球,所述第一再布线层的表面设置有所述锡球,所述锡球与所述第一再布线层电连接;

16、或者所述第一再布线层和所述第二再布线层的表面分别设置有所述锡球,所述锡球与对应的所述第一再布线层和所述第二再布线层电连接。

17、一种三维堆叠芯片的封装方法,用于封装所述的三维堆叠芯片,包括以下步骤:

18、步骤s1、封装体制作:在第一芯片的引脚电镀第二导通连接件,用所述封装体包封所述第一导通连接件、第一芯片和第二导通连接件;

19、步骤s2、第一再布线层制作:在所述封装体的靠近所述第二导通连接件的一侧制作第一再布线层;

20、步骤s3、凹槽制作:在所述第一芯片制作凹槽,所述凹槽仅在所述第一芯片内,或者所述凹槽延伸至所述封装体;

21、步骤s4、三维堆叠芯片贴片:将第二芯片固定在所述凹槽内;

22、步骤s5、第二再布线层制作:在所述封装体的远离所述第一再布线层的一侧制作第二再布线层,得到一种三维堆叠芯片的封装结构。

23、更进一步说明,所述步骤s1封装体制作包括以下步骤:

24、步骤s11、可剥离层制作:在第一载体上制作第一可剥离层;

25、步骤s12、第一导通连接件制作:在所述第一可剥离层上制作所述第一导通连接件;

26、步骤s13、第一芯片预处理:在所述第一芯片的引脚电镀所述第二导通连接件,形成单颗芯片;

27、步骤s14、贴片和塑封:将所述第一芯片远离自身引脚的一端贴合于所述第一剥离层上,通过塑封和压膜使所述封装体包封所述第一芯片;

28、步骤s15、正面研磨:对塑封后的所述第一芯片进行正面研磨,露出所述第一导通连接件和所述第二导通连接件。

29、更进一步说明,所述步骤s2和所述步骤s3之间还包括以下步骤:

30、步骤s21、锡球制作:在所述第一再布线层上制作锡球;

31、步骤s22、锡球面保护:在第二载体上制作第二可剥离层,将所述第二可剥离层贴合在锡球的表面;

32、步骤s23、第一载体解键合:对所述第一载体进行解键合,使封装主体与所述第一载体分离;

33、所述步骤s5中,在所述封装体的远离所述第一再布线层的一侧制作第二再布线层之后,还包括对所述第二载体进行解键合,使封装主体与所述第二载体分离。

34、更进一步说明,所述步骤s5中,在所述封装体的远离所述第一再布线层的一侧制作第二再布线层之后,还包括在所述第二再布线层的表面制作防护层。

35、与现有技术相比,本发明的实施例具有以下有益效果:

36、本发明三维堆叠芯片的封装结构通过将第二芯片嵌入到第一芯片的凹槽内,成品厚度约为一个封装体的厚度,可以降低封装体厚度,满足手机、电脑等终端客户薄型化的需求。此外,通过设置第一再布线层和第二再布线层,实现第一芯片和第二芯片的连接的引出,第一再布线层和第二再布线层能够提高引脚(io)密度,在提高io密度的同时,降低成本。

37、本发明三维堆叠芯片的封装结构,通过将三维堆叠的第二芯片嵌入凹槽内,能够降低封装体的厚度,提高io 密度,三维堆叠芯片的引脚通过再布线(rdl)引出,不需要锡球或者微凸点(microbump),有效降低成本,解决了现有三维封装体堆叠后厚度较厚,难以满足市场薄型化的需求,且封装成本高的技术问题。

技术特征:

1.一种三维堆叠芯片的封装结构,其特征在于,包括封装体、第一芯片、第二芯片、第一导通连接件、第二导通连接件、至少一层第一再布线层和至少一层第二再布线层;

2.根据权利要求1所述的三维堆叠芯片的封装结构,其特征在于,所述凹槽延伸至所述封装体。

3.根据权利要求1所述的三维堆叠芯片的封装结构,其特征在于,还包括至少一层第一绝缘层和至少一层第二绝缘层;

4.根据权利要求3所述的三维堆叠芯片的封装结构,其特征在于,所述第一再布线层、所述第二再布线层、所述第一绝缘层和所述第二绝缘层分别设置有两层;

5.根据权利要求1所述的三维堆叠芯片的封装结构,其特征在于,还包括防护层,所述防护层设置于所述第二再布线层的远离所述第一再布线层的一侧。

6.根据权利要求1所述的三维堆叠芯片的封装结构,其特征在于,还包括锡球,所述第一再布线层的表面设置有所述锡球,所述锡球与所述第一再布线层电连接;

7.一种三维堆叠芯片的封装方法,其特征在于,用于封装如权利要求1~6任意一项所述的三维堆叠芯片,包括以下步骤:

8.根据权利要求7所述的三维堆叠芯片的封装方法,其特征在于,所述步骤s1封装体制作包括以下步骤:

9.根据权利要求8所述的三维堆叠芯片的封装方法,其特征在于,所述步骤s2和所述步骤s3之间还包括以下步骤:

10.根据权利要求7所述的三维堆叠芯片的封装方法,其特征在于,所述步骤s5中,在所述封装体的远离所述第一再布线层的一侧制作第二再布线层之后,还包括在所述第二再布线层的表面制作防护层。

技术总结

本发明涉及半导体集成电路封装技术领域,尤其涉及一种三维堆叠芯片的封装结构及其封装方法。一种三维堆叠芯片的封装结构,包括封装体、第一芯片、第二芯片、第一导通连接件、第二导通连接件、至少一层第一再布线层和至少一层第二再布线层;所述封装体包封所述第一芯片,所述第一导通连接件和所述第二导通连接件均设置于所述封装体中,所述第二导通连接件的一端与所述第一芯片的引脚连接,所述第二导通连接件的另一端与所述第一再布线层连接。所述三维堆叠芯片的封装结构,能够降低封装体的厚度,提高IO密度,有效降低成本,解决了现有三维封装体堆叠后厚度较厚,难以满足市场薄型化的需求,且封装成本高的技术问题。

技术研发人员:黄真瑞,殷美庆

受保护的技术使用者:广东赛昉科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!