一种基于低栅极电荷的N沟道增强型MOSFET器件及制造方法与流程

本发明属于半导体器件设计及制造领域,特别是涉及一种基于低栅极电荷的n沟道增强型mosfet器件及制造方法。

背景技术:

1、mosfet全名为金属-氧化物半导体场效应晶体管,n沟道增强型mos管是mosfet中的一种,其在一块掺杂浓度较低的p型硅衬底上,制作两个高掺杂浓度的n+区,并用金属铝引出两个电极,分别作漏极d和源极s。然后在半导体表面覆盖一层很薄的二氧化硅(sio2)绝缘层,在漏极、源极间的绝缘层上再装上一个铝电极,作为栅极。通过控制栅极的电压能够实现控制源极端子和漏极端子之间的电压和电流,具有开关速度快、输入阻抗高、热稳定性好等特点,主要应用范围涵盖通信、消费电子、汽车电子、工业控制、电源管理等中低压高频领域。

2、n型mosfet的工作原理是在其栅极通入高电平,使得栅极和硅基底之间产生正向电场,硅基底的电荷被吸引并聚集于栅极附近,从而使两个n沟道之间形成可供电子流通的通路。在该过程中,导通(驱动)mosfet而注入到栅极电极的电荷量称作栅极电荷(qg),总栅极电荷值较大,则导通mosfet所需的电容充电时间变长,开关损耗增加,总栅极电荷值较大数值越小,开关损耗越小。

技术实现思路

1、为了解决现有技术中因注入到栅极电极的电荷量较大,则导通mosfet所需的电容充电时间变长,开关损耗增加,总栅极电荷值较大数值越小,开关损耗越小的技术问题,本发明提供一种基于低栅极电荷的n沟道增强型mosfet器件及制造方法。

2、第一方面

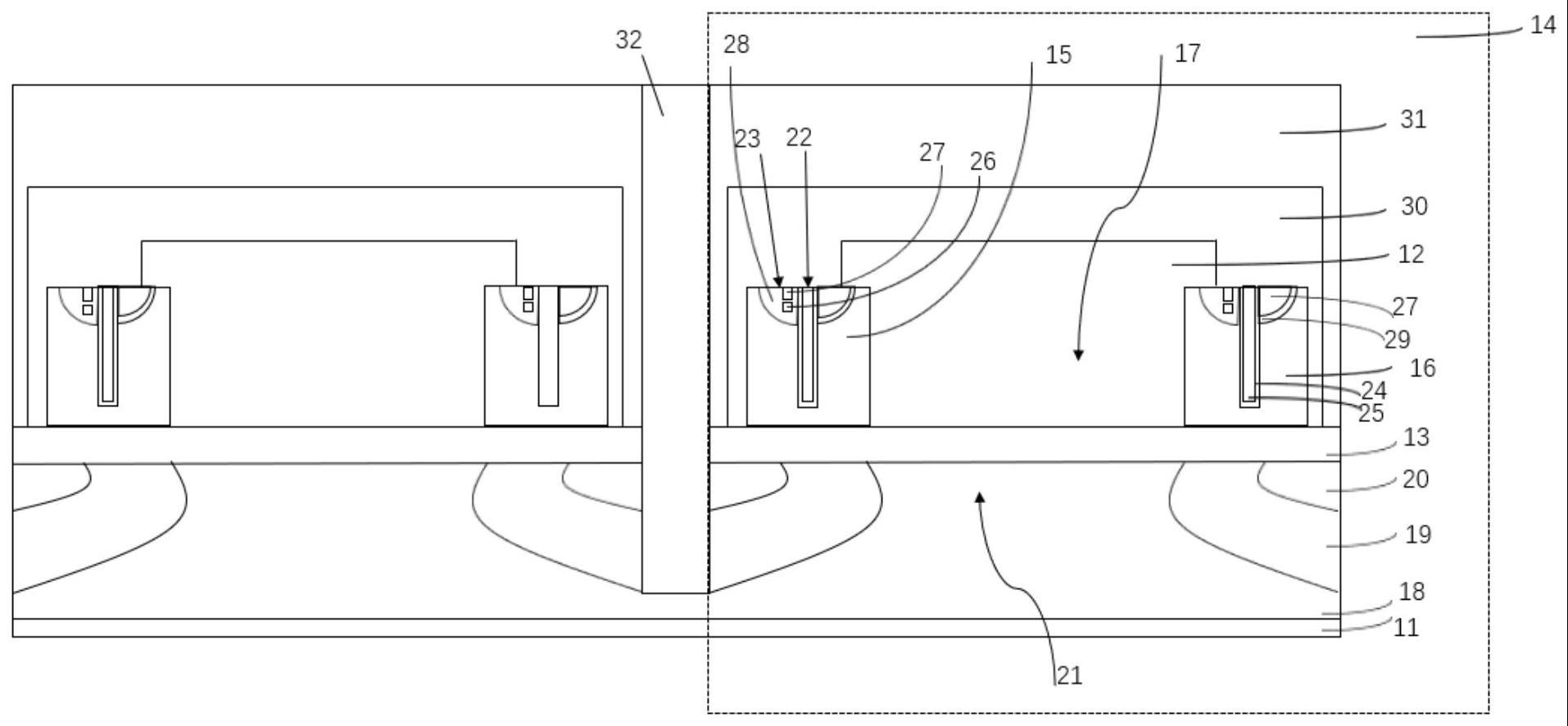

3、本发明提供一种基于低栅极电荷的n沟道增强型mosfet器件,n沟道增强型mosfet器件包括元胞区和终端保护区,所述终端保护区包围所述元胞区,包括:

4、半导体衬底,以及在半导体衬底上生长出的外延层;

5、元胞区,设置于外延层中,元胞区包括至少两个并列设置的器件单胞,器件单胞包括第一栅极区和第二栅极区,第一栅极区和第二栅极区并列设置,且第一栅极区和第二栅极区之间具有缝隙,第一栅极区和第二栅极区朝向半导体衬底的一侧设置有衬底氧化层,在衬底氧化层与半导体衬底之间的外延层具体包括n型外延层,p型外延层以及n型重掺杂源区,n型外延层具有凸起,且凸起的位于缝隙在所述半导体衬底方向上的投影内,p型外延层设置于凸起的两侧,n型重掺杂源区位于p型外延层和衬底氧化层之间;

6、氧化介质设置于缝隙处,第一栅极区内包括第一沟槽和至少两个第二沟槽,至少两个第二沟槽分别设置于第一沟槽的两侧,第一沟槽内壁覆盖有源极介质层,且内部填充有源极多晶硅;至少两个第二沟槽中的任一沟槽靠近槽底的一侧设置有多晶硅屏蔽场板,靠近槽口的一侧设置有多晶硅栅,且填充有氧化层,且氧化层包裹多晶硅屏蔽场板和多晶硅栅极,至少两个第二沟槽中的其他沟槽内壁覆盖有栅介质层,且内部填充有多晶硅栅;

7、隔离介质氧化层,设置于衬底氧化层背离半导体衬底的一侧,且覆盖第一栅极区、第二栅极区和氧化层上;

8、金属层,覆盖于隔离介质氧化层背离半导体衬底的一侧。

9、可选地,至少两个第二沟槽的槽底为弧形,所述弧形为半径为r的圆弧形,且所述至少两个第二沟槽的其他沟槽的多晶硅栅的掺杂浓度与所述半径成反比。

10、可选地,至少两个并列设置的器件单胞之间具有n掺杂深阱部,深阱部使至少两个并列设置的器件单胞相互隔离。

11、可选地,至少两个第二沟槽中的其他沟槽内还包括多晶硅屏蔽场板,从槽口向槽底延伸,在多晶硅屏蔽场板的两侧设置有多晶硅栅,多晶硅栅从槽口向槽底延伸,且多晶硅栅的延伸长度小于多晶硅屏蔽场板的延伸长度,栅介质层环绕多晶硅栅和多晶硅屏蔽场板。

12、可选地,半导体衬底为硅衬底。

13、可选地,源极介质层为氧化层。

14、第二方面

15、本发明提供一种基于低栅极电荷的n沟道增强型mosfet器件的制造方法,包括如下步骤:

16、步骤一:获取半导体衬底,并在半导体衬底上生长出的外延层,外延层包括n型外延层,在外延层上分为元胞区和终端保护区,终端保护区包围元胞区;

17、步骤二:在外延层背离半导体衬底的一侧淀积硬掩膜层,并选择性地掩蔽和刻蚀硬掩膜层,在外延层上刻蚀出至少四个硬掩膜窗口,相邻两个硬掩膜窗口之间具有n型外延层凸起;

18、步骤三:在硬掩膜窗口中注入p型杂质离子,形成p型外延层;

19、步骤四:在p型外延层一侧淀积硬掩膜层,并选择性地掩蔽和刻蚀硬掩膜层,在p型外延层刻蚀出掩膜窗口;

20、步骤五:在掩膜窗口中注入n型重掺杂离子,形成n性重掺杂源区;

21、步骤六:覆盖衬底氧化层,并在衬底氧化层上设置第一栅极区和第二栅极区,第一栅极区和第二栅极区并列设置,且第一栅极区和第二栅极区之间具有缝隙,缝隙中沉积有氧化介质;

22、步骤七:提供隔离氧化层,使隔离氧化层覆盖第一栅极区、第二栅极区和氧化介质;

23、步骤八:分别在第一栅极区和第二栅极区上刻蚀出第一沟槽和至少两个第二沟槽,至少两个第二沟槽分别设置于第一沟槽的两侧,且第一沟槽的深度比至少两个第二沟槽的深度深;

24、步骤九:提供源极介质层以覆盖第一沟槽的内壁,并在第一沟槽中提供有源极多晶硅;

25、步骤十:提供氧化层以覆盖至少两个第二沟槽中的任一沟槽的内壁,并在至少两个第二沟槽中的任一沟槽靠近槽底的一侧沉积多晶硅屏蔽场板,在靠近槽口的一侧沉积有多晶硅栅,且氧化层包裹多晶硅屏蔽场板和的多晶硅栅极;

26、步骤十一:提供栅介质层以覆盖至少两个第二沟槽中的其他沟槽的内壁,并在至少两个第二沟槽中的其他沟槽中提供多晶硅栅;

27、步骤十二:提供金属层,金属层覆盖于隔离介质氧化层背离半导体衬底的一侧。

28、可选地,在步骤三中,注入计量为1e15至8e15原子数/平方厘米。

29、可选地,在步骤十之后还包括:步骤十三:在至少两个第二沟槽中的其他沟槽内通过刻蚀掩膜形成三个掩膜窗口,在三个掩膜窗口的中间窗口中填充多晶硅屏蔽场板,且槽口向槽底延伸;在三个掩膜窗口的其他两个窗口中填充多晶硅栅,多晶硅栅从槽口向槽底延伸,且多晶硅栅的延伸长度小于多晶硅屏蔽场板的延伸长度,在第二沟槽中填充栅介质层,栅介质层环绕多晶硅栅和多晶硅屏蔽场板。

30、与现有技术相比,本发明至少具有以下有益效果:

31、在本发明中,通过增加屏蔽多晶硅有效降低了寄生电容,提高了高频性能且降低了开关损耗,且在栅极结构通过设置第一栅极区和第二栅极区,从而去除了第一栅极区和第二栅极区之间与场效应无关且不对开启起作用的多晶硅条,因此可以降低栅极电荷qg。

技术特征:

1.一种基于低栅极电荷的n沟道增强型mosfet器件,所述n沟道增强型mosfet器件包括元胞区和终端保护区,所述终端保护区包围所述元胞区,其特征在于,包括:

2.根据权利要求1所述的n沟道增强型mosfet器件,其特征在于,所述至少两个第二沟槽的槽壁为弧形,所述弧形为半径为r的圆弧形,且所述至少两个第二沟槽的其他沟槽的多晶硅栅的掺杂浓度与所述半径成反比。

3.根据权利要求1所述的n沟道增强型mosfet器件,其特征在于,所述至少两个并列设置的器件单胞之间具有n掺杂深阱部,所述深阱部使所述至少两个并列设置的器件单胞相互隔离。

4.根据权利要求1所述的n沟道增强型mosfet器件,其特征在于,所述至少两个第二沟槽中的其他沟槽内还包括多晶硅屏蔽场板,所述从所述槽口向所述槽底延伸,在所述多晶硅屏蔽场板的两侧设置有所述多晶硅栅,所述多晶硅栅从所述槽口向所述槽底延伸,且所述多晶硅栅的延伸长度小于所述多晶硅屏蔽场板的延伸长度,所述栅介质层环绕所述多晶硅栅和所述多晶硅屏蔽场板。

5.根据权利要求1所述的n沟道增强型mosfet器件,其特征在于,所述半导体衬底为硅衬底。

6.根据权利要求5所述的n沟道增强型mosfet器件,其特征在于,所述源极介质层为氧化层。

7.一种基于低栅极电荷的n沟道增强型mosfet器件的制造方法,其特征在于,包括如下步骤:

8.根据权利要求7所述的制造方法,其特征在于,在所述步骤三中,注入计量为1e15至8e15原子数/平方厘米。

9.根据权利要求7所述的制造方法,其特征在于,在所述步骤十一之后还包括:步骤十三:在所述至少两个第二沟槽中的其他沟槽内通过刻蚀掩膜形成三个掩膜窗口,在所述三个掩膜窗口的中间窗口中填充多晶硅屏蔽场板,且所述槽口向所述槽底延伸;在所述三个掩膜窗口的其他两个窗口中填充所述多晶硅栅,所述多晶硅栅从所述槽口向所述槽底延伸,且所述多晶硅栅的延伸长度小于所述多晶硅屏蔽场板的延伸长度,在所述第二沟槽中填充所述栅介质层,所述栅介质层环绕所述多晶硅栅和所述多晶硅屏蔽场板。

技术总结

本发明公开了一种基于低栅极电荷的N沟道增强型MOSFET器件及制造方法,属于半导体器件设计及制造领域,包括半导体衬底,以及在半导体衬底上生长出的外延层;至少两个并列设置的器件单胞,器件单胞包括第一栅极区和第二栅极区,第一栅极区和第二栅极区之间具有缝隙,外延层的N型外延层具有凸起,且凸起的位于缝隙在半导体衬底方向上的投影内,P型外延层设置于凸起的两侧,N型重掺杂源区位于P型外延层和衬底氧化层之间;氧化介质设置于缝隙处。本方案能够解决现有技术中因注入到栅极电极的电荷量较大,则导通MOSFET所需的电容充电时间变长,开关损耗增加,总栅极电荷值较大数值越小,开关损耗越小的技术问题。

技术研发人员:涂长招,王力,涂金福,严康,李敏

受保护的技术使用者:福建康博电子技术股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!