一种具有L型漏极的鳍式LDMOS器件

本发明属于半导体,涉及一种具有l型漏极的鳍式ldmos器件。

背景技术:

1、功率半导体器件作为消费电子、工业控制电路、驱动电路等芯片的核心元器件,是实现节能减排的基石与关键环节。soi技术可通过在功率半导体器件中引入介质层来实现功率集成电路的介质隔离。相比于体硅技术,soi技术集成度更高、寄生电容极更小和隔离性能更好,soi技术可以提高集成电路的可靠性,在未来制造高集成度、高可靠性、高速度和低功耗芯片的过程中将成为关键性技术,特别是对功率集成电路。基于绝缘体上硅技术的ldmos器件与其他的大多数新型有源器件如hemt、hbt等相比,拥有更好的cmos工艺兼容性以及方便集成的特点,且本身具有高功率、高增益、高线性度、高开关特性,以及有良好的隔离性能、优越的抗辐照能力和可靠性,故受到行业工作者的广泛关注。soi ldmos主要应用于:智能功率集成电路(smart power integrated ciruit,spic)、射频集成电路(radiofrequency integrated circuit,rfic)、高压集成电路(high voltage integratedcircuit,hvic)。

2、soi横向功率器件的耐压能力由横向击穿电压与纵向击穿电压较小者决定。一般增大器件的横向长度和降低漂移区的掺杂浓度,可以提高器件的横向耐压能力,但同时会导致器件的导通电阻增大,从而使器件的正向导通损耗增大。然而,如果埋氧层与顶层硅的厚度太厚,会导致器件的制造工艺难度增大和器件自热现象加重,以及散热等问题,因此,soi器件的埋氧层与顶层硅不能太厚。但当soi器件的埋氧层与顶层硅太薄时,又会导致器件的纵向耐压能力降低,因为埋氧层会阻止器件的耗尽区扩展到衬底,从而使衬底不会进行耐压。soi横向功率器件的主要矛盾是比导通电阻ron,sp与击穿电压bv具有ron,sp∝bv2.5的关系,降低比导通电阻,同时会导致器件的击穿电压减小;提高器件的击穿电压,同时会使增大器件的比导通电阻。因此,为了解决这一矛盾关系,亟需一种新的ldmos器件。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种具有l型漏极的鳍式ldmos器件,通过使用pnp结构的延伸超结槽栅与漂移区相互耗尽来保证较大的击穿电压的同时,延伸槽栅形成的电荷积累效应和l型漏极可以大幅降低器件的比导通电阻ron,sp,从而降低器件的导通损耗,最终提高了器件的baliga优值fom,fom是一个重要的性能指标,用于衡量soi横向功率器件的综合性能指标,fom=bv2/ron,sp。

2、为达到上述目的,本发明提供如下技术方案:

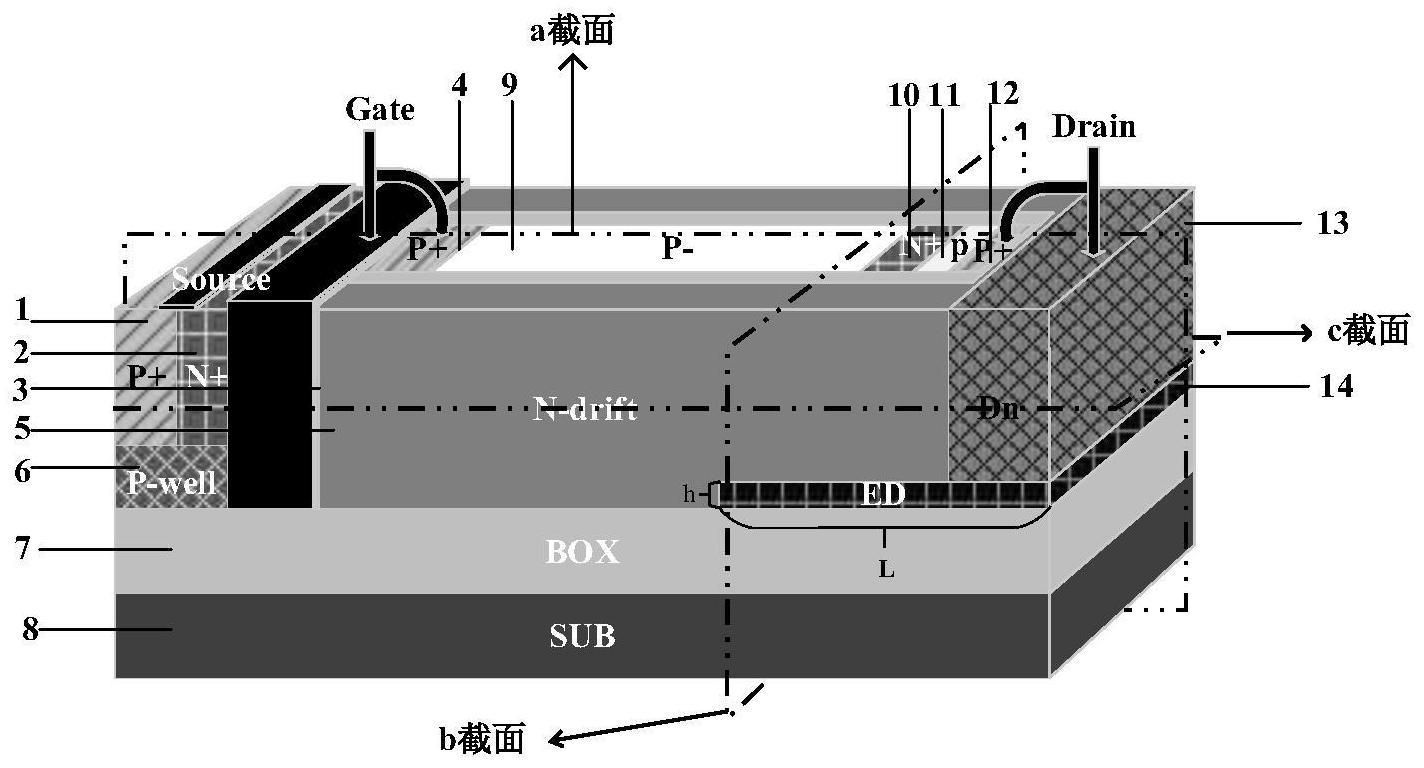

3、一种具有l型漏极的鳍式ldmos器件,该器件包括延伸超结槽栅区和ldmos导电区,以及用于分离所述延伸超结槽栅区和ldmos导电区的二氧化硅隔离层3。ldmos导电区位于二氧化硅隔离层3外侧,延伸超结槽栅区位于二氧化硅隔离层3内侧。

4、可选地,ldmos导电区包括源极p+区1、源极n+区2、p-well6、漂移区5、漏极n+区13和延伸漏极ed14。其中所述源极p+区1、源极n+区2和p-well6位于器件的一端,且依次邻接;漏极n+区13位于器件的另一端。漂移区5位于器件中部,分别与p-well6和漏极n+区13邻接,且包围二氧化硅隔离层3。延伸漏极ed14位于漏极n+区13下方,并嵌入漂移区5。其中漏极n+区13和延伸漏极ed14短接在一起,共同组成一个l型漏极结构。

5、可选地,延伸超结槽栅区包括被二氧化硅隔离层3包围的槽栅p+栅极接触区4、槽栅p-区9、槽栅n+区10、槽栅p区11和槽栅p+漏极接触区12。其中槽栅p+栅极接触区4分别与二氧化硅隔离层3和槽栅p-区9邻接;槽栅p-区9另与槽栅n+区10邻接;槽栅n+区10另与槽栅p区11邻接;槽栅p区11另与槽栅p+漏极接触区12邻接;槽栅p+漏极接触区12另与二氧化硅隔离层3邻接。

6、可选地,该器件还包括埋氧层7和p型衬底8。其中埋氧层7位于延伸超结槽栅区和ldmos导电区下方;p型衬底8位于所述埋氧层7下方。

7、优选地,该器件适用于横向二极管或ligbt。

8、优选地,二氧化硅隔离层3的厚度可根据实际需要改变。延伸漏极ed(14)的掺杂浓度、高度和长度可根据需要改变。槽栅p-区(9)的掺杂浓度也可根据实际需要改变。

9、优选地,漏极n+区13的尺寸为高4.6μm、长1μm、宽2.2μm,掺杂浓度为1×1019cm-3;延伸漏极ed14的尺寸为高0.4μm、长9μm、宽2.2μm,掺杂浓度为7×1016cm-3

10、本发明的有益效果在于:本发明在传统的ldmos器件的基础上,在漂移区内侧引入延伸超结槽栅结构,同时通过二氧化硅隔离层将延伸超结槽栅区和ldmos导电区分离。本发明在正向导通时可形成低阻通道,获得极小的比导通电阻ron,sp;在关断时,可获得较高的击穿电压bv,因此解决了传统ldmos的比导通电阻和击穿电压之间存在的矛盾关系,并打破了硅极限,极大地提高了器件的baliga优值fom。

11、本发明的其他优点、目标和特征在某种程度上将在随后的说明书中进行阐述,并且在某种程度上,基于对下文的考察研究对本领域技术人员而言将是显而易见的,或者可以从本发明的实践中得到教导。本发明的目标和其他优点可以通过下面的说明书来实现和获得。

技术特征:

1.一种具有l型漏极的鳍式ldmos器件,其特征在于:该器件包括延伸超结槽栅区和ldmos导电区,以及用于分离所述延伸超结槽栅区和ldmos导电区的二氧化硅隔离层(3);所述ldmos导电区位于二氧化硅隔离层(3)外侧,所述延伸超结槽栅区位于二氧化硅隔离层(3)内侧。

2.根据权利要求1所述的鳍式ldmos器件,其特征在于:所述ldmos导电区包括源极p+区(1)、源极n+区(2)、p-well(6)、漂移区(5)、漏极n+区(13)和延伸漏极ed(14);所述源极p+区(1)、源极n+区(2)和p-well(6)位于器件的一端,且依次邻接;所述漏极n+区(13)位于器件的另一端;所述漂移区(5)位于器件中部,分别与所述p-well(6)和漏极n+区(13)邻接,且包围所述二氧化硅隔离层(3);所述延伸漏极ed(14)位于所述漏极n+区(13)下方,并嵌入所述漂移区(5)。

3.根据权利要求2所述的鳍式ldmos器件,其特征在于:所述漏极n+区(13)和延伸漏极ed(14)短接形成一l型漏极结构。

4.根据权利要求1所述的鳍式ldmos器件,其特征在于:所述延伸超结槽栅区包括被所述二氧化硅隔离层(3)包围的槽栅p+栅极接触区(4)、槽栅p-区(9)、槽栅n+区(10)、槽栅p区(11)和槽栅p+漏极接触区(12);所述槽栅p+栅极接触区(4)分别与所述二氧化硅隔离层(3)和槽栅p-区(9)邻接;所述槽栅p-区(9)另与所述槽栅n+区(10)邻接;所述槽栅n+区(10)另与所述槽栅p区(11)邻接;槽栅p区(11)另与所述槽栅p+漏极接触区(12)邻接;所述槽栅p+漏极接触区(12)另与所述二氧化硅隔离层(3)邻接。

5.根据权利要求1所述的鳍式ldmos器件,其特征在于:该器件还包括埋氧层(7)和p型衬底(8);所述埋氧层(7)位于延伸超结槽栅区和ldmos导电区下方;所述p型衬底(8)位于所述埋氧层(7)下方。

6.根据权利要求1~5任一项所述的鳍式ldmos器件,其特征在于:该器件适用于横向二极管或ligbt。

7.根据权利要求1所述的鳍式ldmos器件,其特征在于:所述二氧化硅隔离层(3)的厚度根据需求改变。

8.根据权利要求2所述的鳍式ldmos器件,其特征在于:所述延伸漏极ed(14)的掺杂浓度、高度和长度根据需要改变。

9.根据权利要求4所述的鳍式ldmos器件,其特征在于:所述槽栅p-区(9)的掺杂浓度根据需要改变。

技术总结

本发明涉及一种具有L型漏极的鳍式LDMOS器件,属于半导体技术领域。该器件结构特征在于其漏极采用重掺杂L型结构,延伸至二氧化硅埋层;其漂移区由中间的延伸超结槽栅区和LDMOS导电区组成,并利用二氧化硅隔离层将延伸超结槽栅区与LDMOS导电区分离。延伸超结槽栅区由槽栅P+区、槽栅P‑区、槽栅N+区、槽栅P区、槽栅P+区组成;LDMOS导电区由源极P+区、源极N+区、P‑well区、漂移区、漏极和延伸漏极ED组成。本发明在保证获得较高的击穿电压下,能够大幅降低器件的比导通电阻和增大器件的跨导,最终提高器件的Baliga优值FOM,并打破了硅极限。

技术研发人员:陈伟中,段祖兵,何玉婷

受保护的技术使用者:重庆邮电大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!