栅极隔离区域和鳍隔离区域及其形成方法与流程

本公开涉及栅极隔离区域和鳍隔离区域及其形成方法。

背景技术:

1、集成电路(ic)材料和设计的技术进步已经产生了一代又一代的ic,其中每一代都比前几代拥有更小和更复杂的电路。在ic演进的过程中,功能密度(例如,每芯片面积的互连器件的数量)普遍增加,而几何尺寸则减小。这种按比例缩小的过程通常通过提高生产效率并降低相关成本来提供好处。

2、这种按比例缩小也增加了加工和制造ic的复杂性,并且为了实现这些进步,ic加工和制造也需要类似的发展。例如,鳍式场效应晶体管(finfet)已经被引入来取代平面晶体管。finfet的结构和制造finfet的方法正在开发之中。

3、finfet的形成通常包括形成长半导体鳍和长栅极堆叠,然后形成隔离区域,以将长半导体鳍和长栅极堆叠切割为较短的部分,使得较短的部分可以用作finfet的鳍和栅极堆叠。

技术实现思路

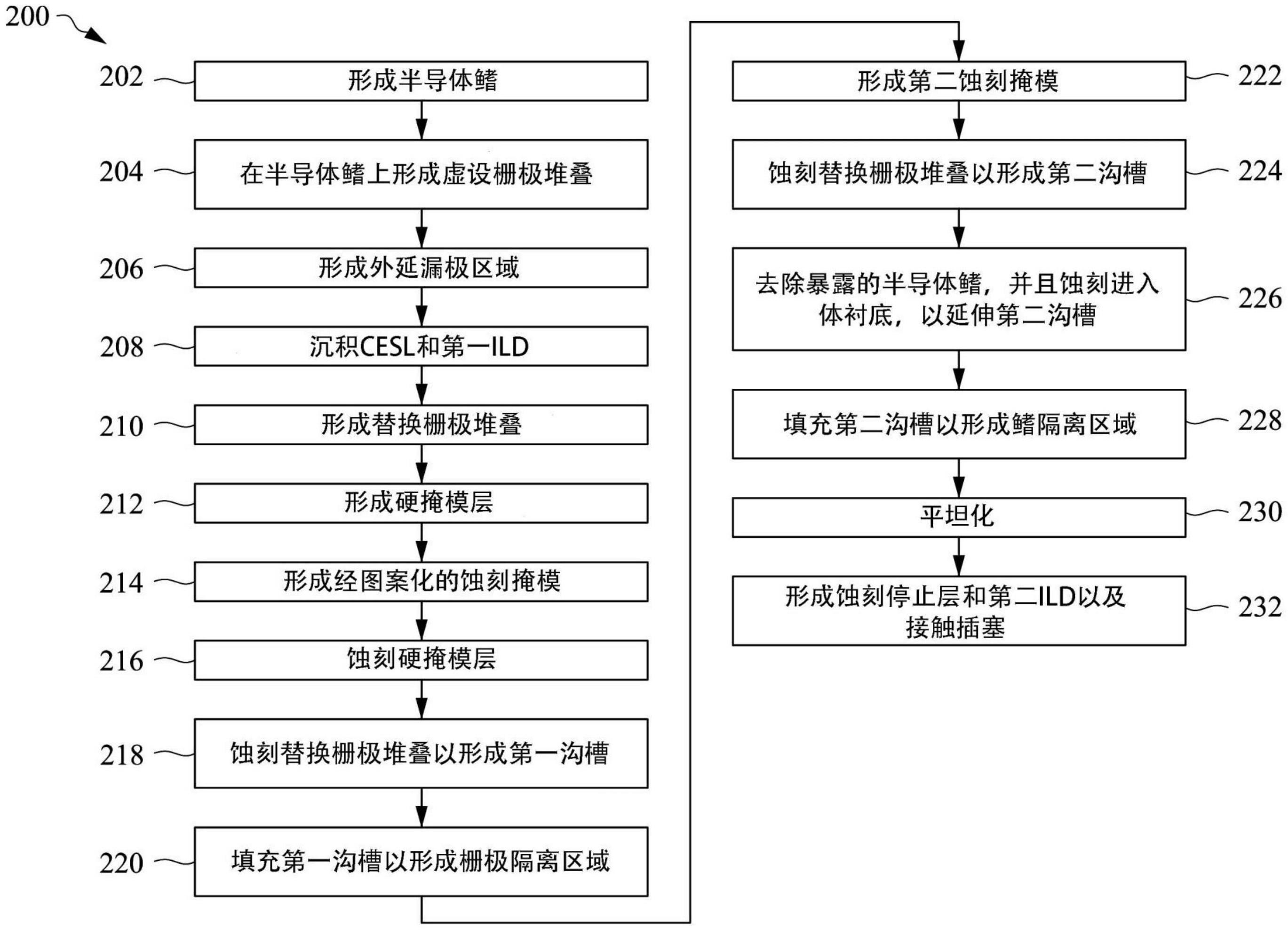

1、根据本公开的第一实施例,提供了一种制造半导体器件的方法,包括:在半导体区域上形成栅极堆叠,其中,所述半导体区域在体半导体衬底之上;蚀刻所述栅极堆叠以形成第一沟槽,其中,所述第一沟槽将所述栅极堆叠分离为第一栅极堆叠部分和第二栅极堆叠部分;形成填充所述第一沟槽的栅极隔离区域,其中,所述栅极隔离区域包括:氮化硅衬里;以及氧化硅填充区域,与所述氮化硅衬里的第一底部部分重叠;蚀刻所述栅极堆叠以形成第二沟槽,其中,突出的半导体鳍暴露于所述第二沟槽;蚀刻所述突出的半导体鳍以将所述第二沟槽延伸到所述体半导体衬底中;以及形成填充所述第二沟槽的鳍隔离区域,其中,所述鳍隔离区域包括:氧化硅衬里;以及氮化硅填充区域,与所述氧化硅衬里的第二底部部分重叠

2、根据本公开的第二实施例,提供了一种半导体结构,包括:第一栅极堆叠,在半导体区域上,其中,所述第一栅极堆叠包括第一栅极堆叠部分和第二栅极堆叠部分;栅极隔离区域,在所述第一栅极堆叠部分和所述第二栅极堆叠部分之间,其中,所述栅极隔离区域包括:第一电介质衬里;以及第一填充区域,与所述第一电介质衬里的第一底部部分重叠;以及鳍隔离区域,穿过第二栅极堆叠,并且穿过所述第二栅极堆叠下方的浅沟槽隔离区域,其中,所述鳍隔离区域包括:第二电介质衬里,其中,所述第一电介质衬里具有与所述第二电介质衬里不同的氮原子百分比;以及第二填充区域,与所述第二电介质衬里的第二底部部分重叠,其中,所述第一填充区域具有与所述第二填充区域不同的氧原子百分比。

3、据本公开的第三实施例,提供了一种半导体结构,包括:栅极堆叠,在半导体区域上,其中,所述栅极堆叠具有第一纵向方向;源极区域和漏极区域,在所述栅极堆叠的相反侧;栅极隔离区域,与所述栅极堆叠的末端接触,其中,所述栅极隔离区域具有垂直于所述第一纵向方向的第二纵向方向,并且其中,所述栅极隔离区域包括:氮化硅衬里;以及氧化硅填充区域,与所述氮化硅衬里的第一底部部分重叠;以及鳍隔离区域,具有平行于所述第一纵向方向的第三纵向方向,其中,所述栅极堆叠和所述鳍隔离区域与所述栅极隔离区域的相反侧壁接触,并且其中,所述鳍隔离区域包括:氧化硅衬里;以及氮化硅填充区域,与所述氧化硅衬里的第二底部部分重叠。

技术特征:

1.一种制造半导体结构的方法,包括:

2.根据权利要求1所述的方法,其中,所述栅极隔离区域中的氮化硅衬里包括第一侧壁,该第一侧壁与所述鳍隔离区域中的氧化硅衬里的第二侧壁接触。

3.根据权利要求1所述的方法,其中,在形成所述第二沟槽时,去除所述栅极隔离区域中的氮化硅衬里的竖直部分,并且其中,所述栅极隔离区域中的氧化硅填充区域与所述鳍隔离区域中的氧化硅衬里接触以形成竖直界面。

4.根据权利要求1所述的方法,其中,在形成所述第一沟槽时,同时蚀刻多个栅极堆叠,其中,所述多个栅极堆叠包括所述栅极堆叠。

5.根据权利要求1所述的方法,其中,蚀刻所述栅极堆叠以形成所述第一沟槽包括:

6.根据权利要求5所述的方法,还包括:在蚀刻所述栅极堆叠以形成所述第二沟槽之前,蚀刻穿过所述多个硬掩模层。

7.根据权利要求5所述的方法,其中,所述多个硬掩模层包括:

8.根据权利要求1所述的方法,其中,所述第一沟槽穿过浅沟槽隔离区域,并且所述第一沟槽停止于所述体半导体衬底。

9.一种半导体结构,包括:

10.一种半导体结构,包括:

技术总结

本公开涉及栅极隔离区域和鳍隔离区域及其形成方法。一种方法,包括:在半导体区域上形成栅极堆叠;蚀刻栅极堆叠以形成第一沟槽,该第一沟槽将栅极堆叠分离为第一栅极堆叠部分和第二栅极堆叠部分;以及形成填充第一沟槽的栅极隔离区域。栅极隔离区域包括:氮化硅衬里;以及氧化硅填充区域,与氮化硅衬里的第一底部部分重叠。该方法还包括:蚀刻栅极堆叠以形成第二沟槽并且暴露突出的半导体鳍;以及蚀刻突出的半导体鳍以将第二沟槽延伸到体半导体衬底中。形成鳍隔离区域以填充第二沟槽。鳍隔离区域包括:氧化硅衬里;以及氮化硅填充区域,与氧化硅衬里的第二底部部分重叠。

技术研发人员:卢柏全,江欣哲,黄泰钧,徐志安

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!