半导体器件的制作方法与流程

本发明属于集成电路制造,具体涉及一种半导体器件的制作方法。

背景技术:

1、半导体器件的制作方法,包括:提供衬底,衬底上形成有介质层,介质层中嵌设有金属层;刻蚀介质层形成暴露出金属层的开孔。在蚀刻形成开孔的过程中,半导体器件晶圆在刻蚀反应腔里的电浆环境中,高浓度带电正电离子经由电弧对半导体器件晶圆表面容易蓄积电荷或在导电部位放电产生高热熔毁半导体器件晶圆表面。这种放电不仅造成半导体器件晶圆表面的熔毁,半导体器件晶圆内部电路也被熔毁。一旦发生弧光放电,半导体器件晶圆基本上是零良率或非常低的良率。

2、在生产过程中,这种发生了弧光放电的半导体器件晶圆需要报废。正常生产过程中,这种报废在可接受范围内,但是遇到某些特定的产品,发生弧光放电的几率从千分之一到百分之一,这种情况对生产来说影响非常大,需要解决。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制作方法,本发明通过对蚀刻菜单(参数)的重新设计,把开孔蚀刻第二介质层的主蚀刻步骤由一次刻蚀改成两次刻蚀,第二次刻蚀降低功率并通过调整气体比率让开孔的形貌和仅通过一次刻蚀形成的形貌相同。第二次刻蚀降低功率,大幅度减少了弧光放电报废晶圆的几率。

2、本发明提供一种半导体器件的制作方法,包括:

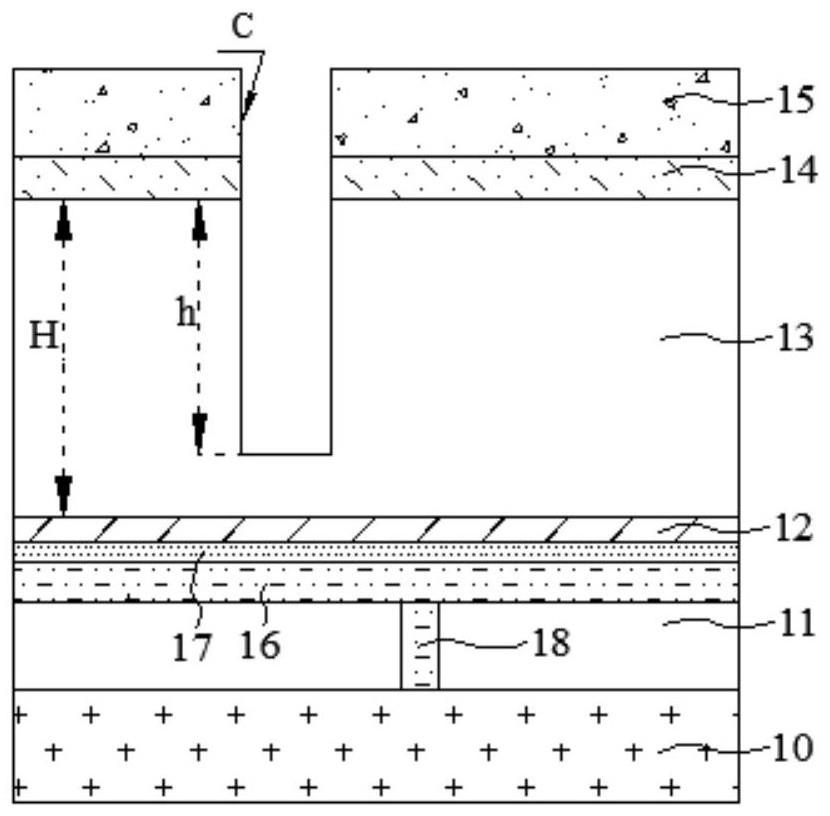

3、提供衬底,所述衬底上依次形成有第一介质层、金属层、第二介质层和图形化的光阻层,所述图形化的光阻层中形成有窗口;

4、第一次刻蚀所述窗口下方的预设厚度的所述第二介质层,

5、第二次刻蚀所述窗口下方的剩余厚度的所述第二介质层形成开孔,

6、其中,所述第二次刻蚀的功率小于所述第一次刻蚀的功率;所述第二次刻蚀的刻蚀气体包含o2和c4f8,所述o2和c4f8二者的比率范围为:50%~90%。

7、进一步的,所述第一次刻蚀采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为10mtorr~100mtorr,功率为100瓦~2000瓦,反应时间为10秒~300秒,刻蚀气体包含c4f8、o2、co和ar。

8、进一步的,所述第二次刻蚀采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为7mtorr~12mtorr,功率为100瓦~600瓦,反应时间为10秒~300秒,刻蚀气体包含co和ar。

9、进一步的,所述预设厚度为所述第二介质层总厚度的50%~90%。

10、进一步的,所述提供衬底还包括:在所述金属层与所述第二介质层之间依次形成有阻挡层和隔离层;所述第二次刻蚀剩余厚度的所述第二介质层暴露出所述隔离层。

11、进一步的,所述第二次刻蚀之后还包括:

12、刻蚀所述隔离层暴露出所述阻挡层;

13、刻蚀所述窗口下方部分厚度的所述阻挡层,形成所述开孔。

14、进一步的,刻蚀所述窗口下方的部分厚度的所述阻挡层采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为10毫托~100毫托,功率为100瓦~500瓦,反应时间为10秒~300秒,刻蚀气体包含c4f8、o2、co和ar。

15、进一步的,所述第二次刻蚀中,刻蚀气体对所述第二介质层与所述隔离层的刻蚀选择比大于8:1。

16、进一步的,所述提供衬底还包括:在所述第一介质层中形成插塞,所述金属层通过所述插塞与所述衬底连接。

17、进一步的,所述制作方法还包括:在所述第二介质层和所述图形化的光阻层之间形成底部抗反射层,刻蚀所述窗口暴露出的所述底部抗反射层至暴露出所述第二介质层。

18、与现有技术相比,本发明具有如下有益效果:

19、本发明提供一种半导体器件的制作方法,包括:提供衬底,所述衬底上依次形成有第一介质层、金属层、第二介质层和图形化的光阻层,所述图形化的光阻层中形成有窗口;第一次刻蚀所述窗口下方的预设厚度的所述第二介质层,第二次刻蚀所述窗口下方的剩余厚度的所述第二介质层形成开孔,其中,所述第二次刻蚀的功率小于所述第一次刻蚀的功率;第二次刻蚀的刻蚀气体包含o2和c4f8,o2和c4f8二者的比率范围为:50%~90%。本发明通过对蚀刻菜单(参数)的重新设计,把开孔蚀刻第二介质层的主蚀刻步骤由一次刻蚀改成两次刻蚀,第二次刻蚀降低功率并通过调整气体比率让开孔的形貌和仅通过一次刻蚀形成的形貌相同。第二次刻蚀降低功率,大幅度减少了弧光放电报废晶圆的几率。

20、进一步的,在所述金属层与所述第二介质层之间形成有阻挡层;所述第二次刻蚀之后还包括:刻蚀所述窗口下方部分厚度的所述阻挡层,形成所述开孔。第二次刻蚀降低功率,同样时间下刻蚀阻挡层的厚度减小,剩余阻挡层的的厚度变大,导致电阻偏高;在降低第二次刻蚀功率的基础上,增加一步刻蚀阻挡层的步骤,刻蚀去除部分厚度的阻挡层,增加了阻挡层的刻蚀时间,使最终金属层的电阻降低,解决降低第二次刻蚀功率造成的电阻偏高的问题。

技术特征:

1.一种半导体器件的制作方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制作方法,其特征在于,所述第一次刻蚀采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为10mtorr~100mtorr,功率为100瓦~2000瓦,反应时间为10秒~300秒,刻蚀气体包含c4f8、o2、co和ar。

3.如权利要求1所述的半导体器件的制作方法,其特征在于,所述第二次刻蚀采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为7mtorr~12mtorr,功率为100瓦~600瓦,反应时间为10秒~300秒,刻蚀气体还包含co和ar。

4.如权利要求1所述的半导体器件的制作方法,其特征在于,所述预设厚度为所述第二介质层总厚度的50%~90%。

5.如权利要求1所述的半导体器件的制作方法,其特征在于,所述提供衬底还包括:在所述金属层与所述第二介质层之间依次形成有阻挡层和隔离层;所述第二次刻蚀剩余厚度的所述第二介质层暴露出所述隔离层。

6.如权利要求5所述的半导体器件的制作方法,其特征在于,所述第二次刻蚀之后还包括:

7.如权利要求6所述的半导体器件的制作方法,其特征在于,刻蚀所述窗口下方的部分厚度的所述阻挡层采用干法等离子体刻蚀,工艺参数包括:反应腔内压力为10毫托~100毫托,功率为100瓦~500瓦,反应时间为10秒~300秒,刻蚀气体包含c4f8、o2、co和ar。

8.如权利要求6所述的半导体器件的制作方法,其特征在于,所述第二次刻蚀中,刻蚀气体对所述第二介质层与所述隔离层的刻蚀选择比大于8:1。

9.如权利要求1至8任意一项所述的半导体器件的制作方法,其特征在于,所述提供衬底还包括:在所述第一介质层中形成插塞,所述金属层通过所述插塞与所述衬底连接。

10.如权利要求1至8任意一项所述的半导体器件的制作方法,其特征在于,所述制作方法还包括:在所述第二介质层和所述图形化的光阻层之间形成底部抗反射层,刻蚀所述窗口暴露出的所述底部抗反射层至暴露出所述第二介质层。

技术总结

本发明提供一种半导体器件的制作方法,包括:提供衬底,衬底上依次形成有第一介质层、金属层、第二介质层和图形化的光阻层,图形化的光阻层中形成有窗口;第一次刻蚀窗口下方的预设厚度的第二介质层,第二次刻蚀窗口下方的剩余厚度的第二介质层形成开孔,其中,第二次刻蚀的功率小于第一次刻蚀的功率;第二次刻蚀的刻蚀气体包含O<subgt;2</subgt;和C<subgt;4</subgt;F<subgt;8</subgt;,O<subgt;2</subgt;和C<subgt;4</subgt;F<subgt;8</subgt;二者的比率范围为:50%~90%。本发明通过对蚀刻菜单(参数)的重新设计,把开孔蚀刻第二介质层的主蚀刻步骤由一次刻蚀改成两次刻蚀,第二次刻蚀降低功率并通过调整气体比率让开孔的形貌和仅通过一次刻蚀形成的形貌相同。第二次刻蚀降低功率,大幅度减少了弧光放电报废晶圆的几率。

技术研发人员:周广伟,汤莉娟,华良

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!