半导体器件及其制备方法与流程

本发明涉及半导体,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、在半导体器件的制备过程中,需要控制栅极材料层的底部关键尺寸(cd,criticaldimension)与顶部cd相同,因此,需要刻蚀掉u型沟槽(u-trench)结构的顶部和底部的栅极材料层。然而,在实际工艺中,在刻蚀底部栅极材料层的同时会刻蚀u-trench侧壁上的栅极材料层,导致栅极材料层出现侧向刻蚀的现象。

技术实现思路

1、本申请提供一种半导体器件及其制备方法,能够解决半导体器件的制备过程中,栅极材料层出现侧向刻蚀的问题。

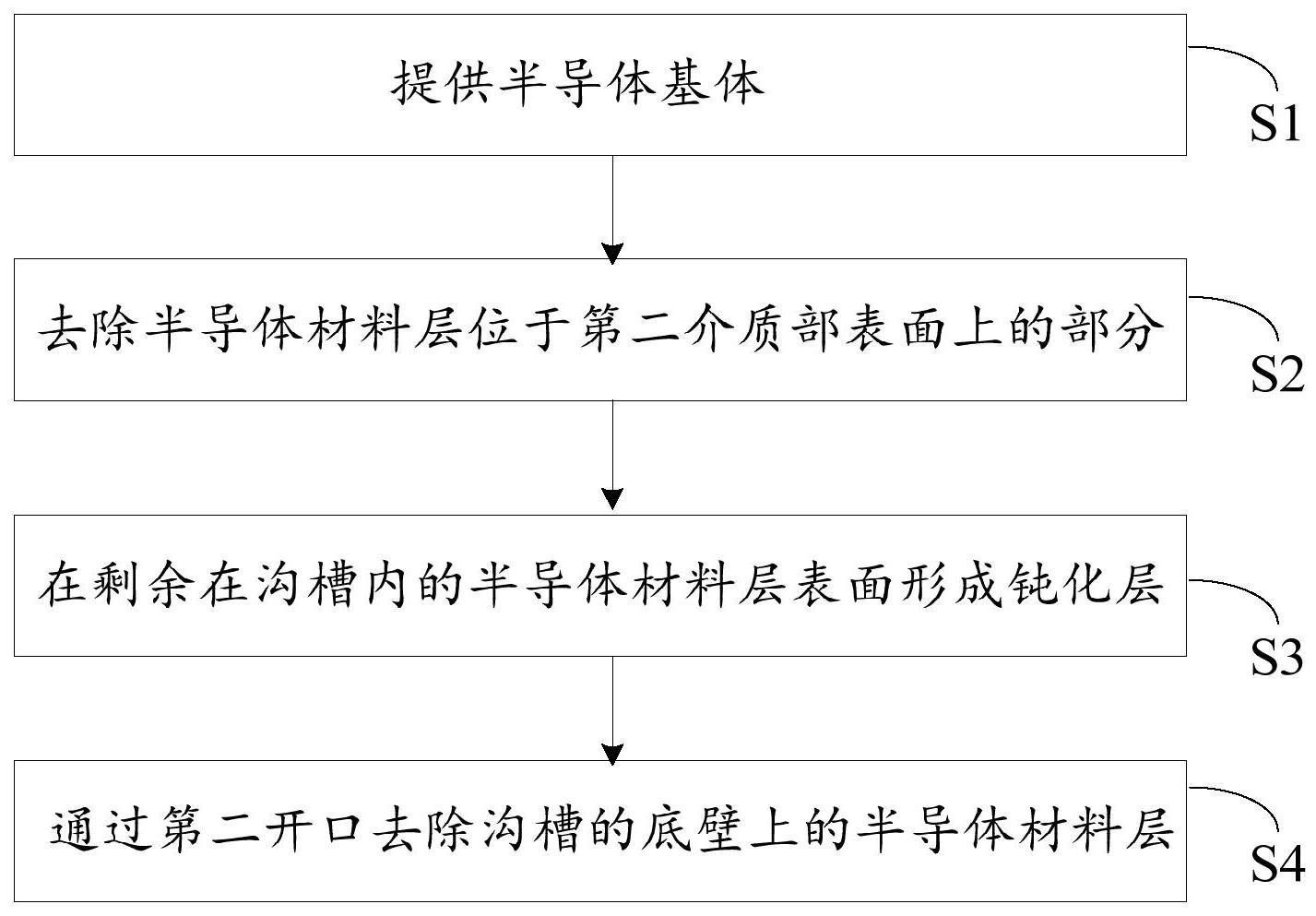

2、为解决上述技术问题,本申请第一方面提供一种半导体器件的制备方法。该方法包括提供半导体基体;所述半导体基体包括衬底、介质层以及半导体材料层;其中,所述衬底上开设有沟槽,所述介质层包括第一介质部和第二介质部;所述第一介质部覆盖在所述沟槽的内壁面上,并界定形成第一开口;所述第二介质部覆盖在所述衬底的上表面,并界定形成第二开口,且所述第二开口的宽度小于所述第一开口的宽度;所述半导体材料层覆盖所述介质层,并在对应所述第二开口的位置界定形成第三开口;

3、去除所述半导体材料层位于所述第二介质部表面上的部分;

4、在剩余在所述沟槽内的所述半导体材料层表面形成钝化层;以及

5、通过所述第二开口去除所述沟槽的底壁上的所述半导体材料层。

6、其中,所述去除所述半导体材料层位于所述第二介质部表面上的部分的步骤,包括:

7、采用第一次干法刻蚀制程去除所述半导体材料层位于所述第二介质部背离所述衬底的一侧表面上的部分,并去除所述半导体材料层位于所述第二介质部的侧壁的内壁面上的部分。

8、其中,采用所述第一次干法刻蚀制程去除所述半导体材料层位于所述第二介质部背离所述衬底的一侧表面上的部分的同时,去除所述沟槽的底壁上通过所述第三开口露出的所述半导体材料层。

9、其中,所述方法满足以下条件中的至少一种:

10、所述第一次干法刻蚀制程中,所述半导体材料层的材料与所述介质层的材料的刻蚀选择比不小于15:1;

11、所述第一次干法刻蚀制程使用的刻蚀气体包括氯气、氧气、溴化氢;所述氯气、氧气、溴化氢的流量比(5-10):(10-20):(1-4)。

12、其中,在剩余在所述沟槽内的所述半导体材料层表面形成钝化层的步骤,包括:

13、对剩余在所述沟槽内的所述半导体材料层的表面进行钝化处理,以使剩余的所述半导体材料层的部分转化成钝化层;或者,

14、在剩余在所述沟槽内的所述半导体材料层的表面设置所述钝化层。

15、其中,所述对剩余在所述沟槽内的所述半导体材料层的表面进行钝化处理的步骤,包括:

16、通入钝化气体对剩余在所述沟槽内的所述半导体材料层背离所述第一介质部的一侧表面进行钝化处理。

17、其中,所述钝化气体的流量大于等于5000sccm且小于等于9000sccm;和/或,用于固定所述半导体基体的第一固定元件的温度大于等于200℃且小于等于350℃。

18、其中,所述半导体基体上的所述半导体材料层的厚度大于等于3000埃且小于等于5500埃;和/或

19、所述钝化层的厚度大于80埃。

20、其中,所述通过所述第二开口去除所述沟槽的底壁上的所述半导体材料层的步骤,包括:

21、采用第二次干法刻蚀制程去除所述沟槽的底壁上的通过所述第二开口露出的所述半导体材料层。

22、其中,所述第二次干法刻蚀制程所在的刻蚀腔内的压力大于等于8mt且小于等于60mt;和/或,用于固定所述半导体基体的第二固定元件的温度大于等于30℃且小于等于70℃。

23、其中,在通过所述第二开口去除所述沟槽的底壁上的所述半导体材料层的步骤之后,还包括:

24、延长20%-30%的所述第二次干法刻蚀制程的工艺时间。

25、其中,所述半导体材料层为栅极材料层,且所述栅极材料层的材料包括多晶硅;和/或所述钝化层的材料包括氧化硅和/或氮化硅。

26、为解决上述技术问题,本申请第二方面提供一种半导体器件。该半导体器件包括:

27、半导体基体,包括衬底、介质层以及栅极;其中,所述衬底上开设有沟槽,所述介质层包括第一介质部和第二介质部;所述第一介质部覆盖在所述沟槽的内壁面上;所述第二介质部覆盖在所述衬底的表面,并界定形成第二开口;所述栅极覆盖所述第一介质部去除所述第二开口在所述衬底上的投影区域后剩余的部分。

28、其中,还包括:

29、钝化层,形成于所述栅极背离所述第一介质部的一侧表面。

30、其中,所述半导体器件满足以下a-c中至少一个特征:

31、a.所述栅极的材料包括多晶硅;所述钝化层的材料包括氧化硅和/或氮化硅;

32、b.所述栅极的厚度大于等于3000埃且小于等于5500埃;

33、c.所述钝化层的厚度大于80埃。

34、本申请一些实施例提供的半导体器件的制备方法,包括提供半导体基体;半导体基体包括衬底、介质层以及半导体材料层;其中,衬底上开设有沟槽,介质层包括第一介质部和第二介质部;第一介质部覆盖在沟槽的内壁面上,并界定形成第一开口;第二介质部覆盖在衬底的上表面,并界定形成第二开口;所述第二开口的宽度小于第一开口的宽度;半导体材料层覆盖介质层,并在对应第二开口的位置界定形成第三开口;然后去除半导体材料层位于第二介质部表面上的部分;在剩余在沟槽内的半导体材料层表面形成钝化层;通过第二开口去除沟槽的底壁上的半导体材料层。该方法通过在去除沟槽底壁上的半导体材料层的步骤之前,先在剩余在沟槽内的半导体材料层表面形成钝化层,以利用该钝化层对半导体材料层的表面进行保护,防止在刻蚀沟槽底壁上的半导体材料层的过程中,因等离子体(plasma)在弧形区域聚集导致半导体材料层出现侧向刻蚀的现象;有效保证了后续制备工艺的正常进行,提高了产品良率。

技术特征:

1.一种半导体器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体器件的制备方法,其特征在于,

3.根据权利要求2所述的半导体器件的制备方法,其特征在于,

4.根据权利要求2或3所述的半导体器件的制备方法,其特征在于,所述方法满足以下条件中的至少一种:

5.根据权利要求1-3任一项所述的半导体器件的制备方法,其特征在于,在剩余在所述沟槽内的所述半导体材料层表面形成钝化层的步骤,包括:

6.根据权利要求5所述的半导体器件的制备方法,其特征在于,

7.根据权利要求6所述的半导体器件的制备方法,其特征在于,

8.根据权利要求1所述的半导体器件的制备方法,其特征在于,

9.根据权利要求1所述的半导体器件的制备方法,其特征在于,

10.根据权利要求9所述的半导体器件的制备方法,其特征在于,

11.根据权利要求9所述的半导体器件的制备方法,其特征在于,

12.根据权利要求1所述的半导体器件的制备方法,其特征在于,

13.一种半导体器件,其特征在于,包括:

14.根据权利要求13所述的半导体器件,其特征在于,还包括:

15.根据权利要求14所述的半导体器件,其特征在于,所述半导体器件满足以下a-c中至少一个特征:

技术总结

本申请提供一种半导体器件及其制备方法。该方法包括提供半导体基体;半导体基体包括衬底、介质层以及半导体材料层;其中,衬底上开设有沟槽,介质层包括第一介质部和第二介质部;第一介质部覆盖在沟槽的内壁面上,并界定形成第一开口;第二介质部覆盖在衬底的上表面,并界定形成第二开口;第二开口的宽度小于第一开口的宽度;半导体材料层覆盖介质层,并在对应第二开口的位置界定形成第三开口;去除半导体材料层位于第二介质部表面上的部分;在剩余在沟槽内的半导体材料层表面形成钝化层;以及通过第二开口去除沟槽的底壁上的半导体材料层。该方法能防止半导体材料层出现侧向刻蚀的现象,保证了后续工艺的正常进行。

技术研发人员:史航,谢岩,宋保英

受保护的技术使用者:武汉新芯集成电路制造有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!