集成结势垒肖特基二极管的沟槽型MOSFET器件及制造方法与流程

本申请涉及功率半导体制造,尤其涉及集成结势垒肖特基二极管的沟槽型mosfet器件及制造方法。

背景技术:

1、碳化硅晶体中存在基晶面位错(bpd),在一定条件下,基晶面位错(bpd)可以转化为堆垛层错(sf)。当碳化硅功率mosfet器件中的体二极管导通时,在双极型运行下,电子-空穴的复合会使堆垛层错(sf)继续扩展,发生双极性退化。这一现象使得碳化硅功率mosfet的导通压电阻增大,阻断模式下的漏电流增大,体二极管的导通压降增大,从而降低器件的可靠性。

2、在实际的电路应用中,为了避免双极性退化,设计者一般使用外部反向并联肖特基二极管来抑制功率mosfet器件中的体二极管。然而,出于成本的考虑,我们可以将结势垒肖特基二极管嵌入到功率mosfet器件中的每个元胞单元,同时整个器件共用同一个的终端结构,这样一来,可以减小总芯片尺寸。

3、而对于元胞内部集成结势垒肖特基二极管的碳化硅沟槽型功率mosfet器件,结势垒肖特基结构和mosfet结构共同占用器件的有源区部分,因此二者存在折中与权衡的矛盾关系。若二者失衡,则会导致较大的mosfet导通损耗,或使得结势垒肖特基二极管的电流导通能力较弱,降低器件的综合电性能。

技术实现思路

1、本申请实施例提供了集成结势垒肖特基二极管的沟槽型mosfet器件及制造方法,用于解决如下技术问题:结势垒肖特基结构和mosfet结构共同占用器件的有源区部分,若二者失衡,会导致较大的mosfet导通损耗,或使得结势垒肖特基二极管的电流导通能力较弱,降低器件的实用性。

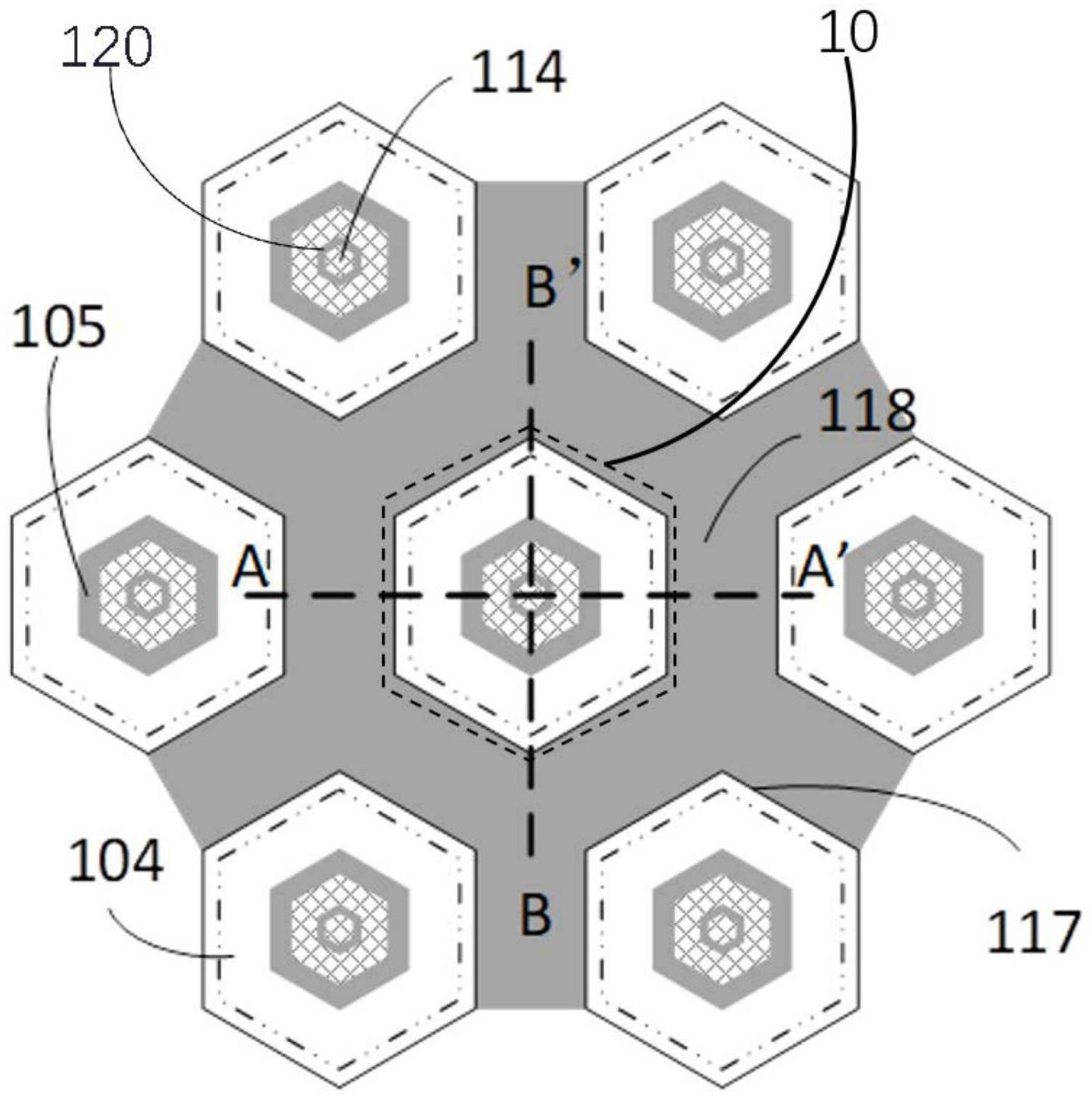

2、一方面,本申请实施例提供了集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述器件包括:外延层与位于所述外延层顶部的mosfet结构;其中,所述外延层为n型区域;所述mosfet结构包括:若干个形状与结构均相同的元胞、第一高掺杂p型区域、沟槽;各元胞均包括阱区、源极区域、第二高掺杂p型区域、包含预设数量个第三高掺杂p型区域的结势垒肖特基区域、jfet区域;其中:所述阱区为p型区域,所述源极区域为n型区域;所述第三高掺杂p型区域包括环状第三高掺杂p型区域与岛状第三高掺杂p型区域;所述阱区位于所述外延层的顶部表面,与所述外延层形成第一pn结;所述源极区域与所述第二高掺杂p型区域均位于所述阱区内背离所述外延层的一侧表面,所述阱区与所述源极区域形成第二pn结,所述源极区域环绕所述第二高掺杂p型区域;所述结势垒肖特基区域位于所述阱区与所述源极区域的内侧环绕区域内,预设数量个第三高掺杂p型区域在所述结势垒肖特基区域内等间距排列;所述沟槽位于各元胞之间,元胞之间的沟槽截面呈u型,所述沟槽的底部拐角处为圆角;所述第一高掺杂p型区域包裹所述沟槽的底部;所述第一高掺杂p型区域与所述外延层第三pn结;所述阱区与相邻的所述第一高掺杂p型区域之间形成结型场效应管jfet区域。

3、在本申请的一种实现方式中,所述jfet区域的宽度的取值范围与所述结势垒肖特基区域中第三高掺杂p型区域的间距的取值范围均在相同的预设区间内;其中,所述预设区间为[0.8μm~5μm],所述预设数量的范围为1~10。

4、在本申请的一种实现方式中,所述mosfet结构还包括:欧姆接触金属、肖特基接触金属;所述欧姆接触金属覆盖于所述第二高掺杂p型区域和部分所述源极区域的顶部,并在接触位置同时与所述第二高掺杂p型区域以及部分所述源极区域形成欧姆接触,以抑制mosfet器件内部的寄生双极晶体管效应;所述肖特基接触金属覆盖于所述结势垒肖特基区域的顶部,并在接触位置形成肖特基接触。

5、在本申请的一种实现方式中,所述mosfet结构还包括:绝缘栅极氧化层与栅极导电多晶硅;所述绝缘栅极氧化层覆盖于所述沟槽的内壁;所述栅极导电多晶硅填充于所述沟槽。

6、在本申请的一种实现方式中,所述mosfet结构还包括:绝缘介质层;所述绝缘介质层覆盖于填充后的所述沟槽顶部与各元胞的部分源极区域顶部。

7、在本申请的一种实现方式中,所述mosfet结构还包括:源极电极;所述源极电极覆盖于欧姆接触金属及肖特基接触金属上;所述绝缘介质层将所述栅极导电多晶硅与所述源极金属分隔开。

8、在本申请的一种实现方式中,所述器件还包括:碳化硅衬底、漏极电极;所述碳化硅衬底的顶部与所述外延层的底部接触;其中,所述碳化硅衬底为n型区域;所述漏极电极覆盖于所述碳化硅衬底的底部。

9、在本申请的一种实现方式中,所述碳化硅衬底中的离子掺杂浓度大于所述外延层中的离子掺杂浓度;所述jfet区域与所述结势垒肖特基区域中的离子掺杂浓度大于或等于所述外延层的离子掺杂浓度。

10、在本申请的一种实现方式中,所述元胞的形状为圆形或多边形。

11、另一方面,本申请实施例还提供了集成结势垒肖特基二极管的沟槽型mosfet器件制造方法,其特征在于,所述制造方法包括如下步骤:s1.形成碳化硅衬底,并在碳化硅衬底的一面形成外延层;s2.在外延层的表面形成加强型第一导电类型的肖特基区域;s3.在外延层的表面形成多个第二导电类型的阱区;其中,第一导电类型为n型,第二导电类型为p型;s4.在含有第二导电类型的阱区内部形成多个高掺杂的第一导电类型的源极区域;s5.在外延层的表面形成多个沟槽结构;s6.在沟槽的侧壁形成加强型第一导电类型的jfet区域;s7.在沟槽底部形成多个第一高掺杂p型区域,在平台表面形成多个第二高掺杂p型区域和第二导电类型的第三高掺杂p型区域;s8.在沟槽的底部和侧壁形成绝缘栅极氧化层;s9.在沟槽内部的形成栅极导电多晶硅,填满沟槽,并且其高度接近与外延层平台齐平的位置;s10.在器件的表面形成多个绝缘介质层;s11.在器件表面的高掺杂第一导电类型的源极区域和第二高掺杂p型区域上方形成欧姆接触金属;s12.在器件表面的加强型肖特基区域上方形成肖特基接触金属;s13.在器件的顶部形成源极电极;s14.在碳化硅衬底的另一面形成漏极电极。

12、本申请实施例提供的集成结势垒肖特基二极管的沟槽型mosfet器件及制造方法,将结势垒肖特基二极管集成于沟槽型功率mosfet的元胞结构中,通过圆形或多边形元胞的布局,实现了结势垒肖特基二极管和沟槽型功率mosfet二者性能的折中与权衡,提高了器件的综合电性能。

技术特征:

1.集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述器件包括:

2.根据权利要求1所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,

3.根据权利要求1所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述mosfet结构还包括:欧姆接触金属、肖特基接触金属;

4.根据权利要求1所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述mosfet结构还包括:绝缘栅极氧化层与栅极导电多晶硅;

5.根据权利要求4所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述mosfet结构还包括:绝缘介质层;

6.根据权利要求5所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述mosfet结构还包括:源极电极;

7.根据权利要求1所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述器件还包括:碳化硅衬底、漏极电极;

8.根据权利要求7所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,

9.根据权利要求1所述的集成结势垒肖特基二极管的沟槽型mosfet器件,其特征在于,所述元胞的形状为圆形或多边形。

10.集成结势垒肖特基二极管的沟槽型mosfet器件制造方法,其特征在于,所述制造方法包括如下步骤:

技术总结

本申请公开了集成结势垒肖特基二极管的沟槽型MOSFET器件及制造方法。器件包括:外延层与位于外延层顶部的MOSFET结构;MOSFET结构包括:若干个元胞、第一高掺杂P型区域、沟槽;元胞包括阱区、源极区域、第二高掺杂P型区域、包含预设数量个第三高掺杂P型区域的结势垒肖特基区域、JFET区域;阱区与外延层形成第一PN结;源极区域与阱区形成第二PN结;阱区与第二高掺杂P型区域环绕结势垒肖特基区域;沟槽位于各元胞之间,第一高掺杂P型区域包裹沟槽底部;第一高掺杂P型区域与外延层形成第三PN结;阱区与相邻的第一高掺杂P型区域形成JFET区域。本申请通过上述器件解决了结势垒肖特基结构和MOSFET结构共同占用器件的有源区部分时无法兼顾二者导通特性的问题。

技术研发人员:于霄恬

受保护的技术使用者:海科(嘉兴)电力科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!