半导体封装及其制造方法与流程

本申请大体上涉及半导体技术,且更具体地,涉及半导体封装及其制作方法。

背景技术:

1、由于消费者想要其电子设备体积更小、速度更快、性能更高,并将越来越多的功能封装到单个装置中,半导体行业一直面临着复杂集成的挑战。为了解决此问题,引入了基于小芯片(chiplet-based)的封装以形成芯片上系统(system-on-chip,soc)。在基于小芯片的封装中,多个小芯片经连接以产生单个复杂集成电路。基于小芯片的封装提供优于传统的单片式soc的若干益处,包括性能改进、功耗降低且设计灵活性提高。然而,基于小芯片的封装中的小芯片通过封装工艺互连,导致集成密度低且性能低。

2、因此,需要具有更高集成密度和改进性能的基于小芯片的封装。

技术实现思路

1、本申请的目标为提供一种具有更高集成密度和/或改进性能的半导体封装。

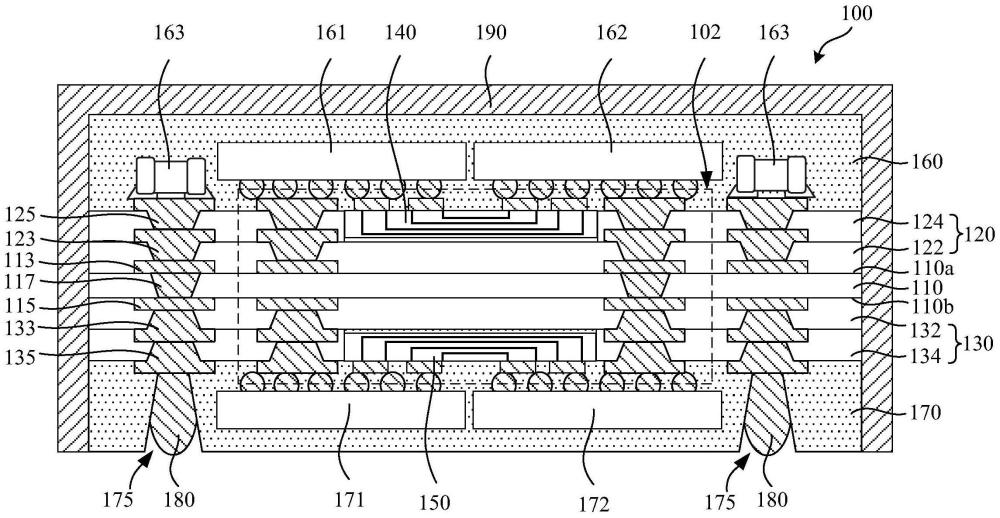

2、根据本申请的实施例的一方面,提供一种半导体封装。所述半导体封装可包括:基底,其具有第一表面和与所述第一表面相对的第二表面;第一绝缘层,其设置于所述基底的所述第一表面上且具有第一凹槽部分;第一半导体中介层,其设置于所述第一绝缘层的所述第一凹槽部分中,所述第一半导体中介层包括第一半导体层和形成于所述第一半导体层上的多个第一布线图案;第一电子元件,其与所述第一半导体中介层的第一部分重叠且与所述第一半导体中介层的所述第一布线图案电连接;以及第二电子元件,其与所述第一半导体中介层的第二部分重叠且与所述第一半导体中介层的所述第一布线图案电连接。

3、根据本申请的实施例的另一方面,提供一种用于制造半导体封装的方法。所述方法可包括:提供基底,所述基底具有第一表面和与所述第一表面相对的第二表面;在所述基底的所述第一表面上形成第一绝缘层,所述第一绝缘层具有形成于其中的第一凹槽部分;将第一半导体中介层嵌入到所述第一绝缘层的所述第一凹槽部分中,所述第一半导体中介层包括第一半导体层和形成于所述第一半导体层上的多个第一布线图案;将第一电子元件安装于所述第一半导体中介层上,所述第一电子元件与所述第一半导体中介层的第一部分重叠且与所述第一半导体中介层的所述第一布线图案电连接;以及将第二电子元件安装于所述第一半导体中介层上,所述第二电子元件与所述第一半导体中介层的第二部分重叠且与所述第一半导体中介层的所述第一布线图案电连接。

4、应理解,以上一般描述和以下详细描述两者仅是示例性和解释性的并且并不限制本发明。此外,并入在本说明书中且构成本说明书的一部分的附图说明了本发明的实施例,并且与描述一起用以解释本发明的原理。

技术特征:

1.一种半导体封装,其特征在于,所述半导体封装包括:

2.根据权利要求1所述的半导体封装,其特征在于,所述第一绝缘层包括第一绝缘子层和形成于所述第一绝缘子层上的第二绝缘子层,且所述第一绝缘层的所述第一凹槽部分包括形成于所述第二绝缘子层中的第一窗口。

3.根据权利要求1所述的半导体封装,其特征在于,所述半导体封装进一步包括:

4.根据权利要求1所述的半导体封装,其特征在于,所述半导体封装进一步包括:

5.根据权利要求1所述的半导体封装,其特征在于,所述半导体封装进一步包括:

6.根据权利要求5所述的半导体封装,其特征在于,所述第二绝缘层包括第三绝缘子层和形成于所述第三绝缘子层上的第四绝缘子层,且所述第二绝缘层的所述第二凹槽部分包括形成于所述第四绝缘子层中的第二窗口。

7.根据权利要求5所述的半导体封装,其特征在于,所述半导体封装进一步包括:

8.根据权利要求5所述的半导体封装,其特征在于,所述半导体封装进一步包括:

9.根据权利要求8所述的半导体封装,其特征在于,所述导电凸块包括焊料凸块、铜柱,或电功能柱导电结构。

10.一种用于制造半导体封装的方法,其特征在于,所述方法包括:

11.根据权利要求10所述的方法,其特征在于,在所述基底的所述第一表面上形成所述第一绝缘层包括:

12.根据权利要求10所述的方法,其特征在于,将所述第一半导体中介层嵌入到所述第一绝缘层的所述第一凹槽部分中包括:

13.根据权利要求10所述的方法,其特征在于,所述方法进一步包括:

14.根据权利要求10所述的方法,其特征在于,所述方法进一步包括:

15.根据权利要求14所述的方法,其特征在于,在所述基底的所述第二表面上形成所述第二绝缘层包括:

16.根据权利要求14所述的方法,其特征在于,将所述第二半导体中介层嵌入到所述第二绝缘层的所述第二凹槽部分中包括:

17.根据权利要求14所述的方法,其特征在于,所述方法进一步包括:

18.根据权利要求17所述的方法,其特征在于,所述导电凸块包括焊料凸块、铜柱,或电功能柱导电结构。

技术总结

本申请提供了一种半导体封装和一种用于制造所述半导体封装的方法。所述半导体封装可包括:基底,其具有第一表面和与所述第一表面相对的第二表面;第一绝缘层,其设置于所述基底的所述第一表面上且具有第一凹槽部分;第一半导体中介层,其设置于所述第一绝缘层的所述第一凹槽部分中,所述第一半导体中介层包括第一半导体层和形成于所述第一半导体层上的多个第一布线图案;第一电子元件,其与所述第一半导体中介层的第一部分重叠且与所述第一半导体中介层的所述第一布线图案电连接;以及第二电子元件,其与所述第一半导体中介层的第二部分重叠且与所述第一半导体中介层的所述第一布线图案电连接。

技术研发人员:李泰雨,李喜秀,明恩喜

受保护的技术使用者:星科金朋私人有限公司

技术研发日:

技术公布日:2024/11/7

- 还没有人留言评论。精彩留言会获得点赞!