电介质组合物和层叠陶瓷电子部件的制作方法

本发明涉及电介质组合物和包含该电介质组合物的层叠陶瓷电子部件。

背景技术:

1、在组装于电子设备的电子电路或电源电路中,搭载有多个利用电介质表现的介电特性的层叠陶瓷电容器这样的电子部件。作为在这样的电子部件中利用的电介质材料,已知有专利文献1所示的(ca、sr)(zr、ti、hf)o3系的电介质组合物。

2、专利文献1所公开的电介质组合物,其由温度引起的静电电容的变化小,具有由eia标准(电子工业联盟标准:electronic industries alliance standard)规定的c0g特性。因此,该电介质组合物适合用于温度补偿用的层叠陶瓷电子部件等。但是,可知在包含该电介质组合物的层叠陶瓷电子部件中,若使电介质层的层间厚度变薄,则容易产生脉冲耐压不良。

3、现有技术文献

4、专利文献

5、专利文献1:日本专利第4678022号

技术实现思路

1、发明所要解决的技术问题

2、本发明是鉴于这样的实际情况而完成的,其目的在于提供一种与以往相比不易产生脉冲耐压不良的电介质组合物、以及包含该电介质组合物的层叠陶瓷电子部件。

3、用于解决技术问题的技术方案

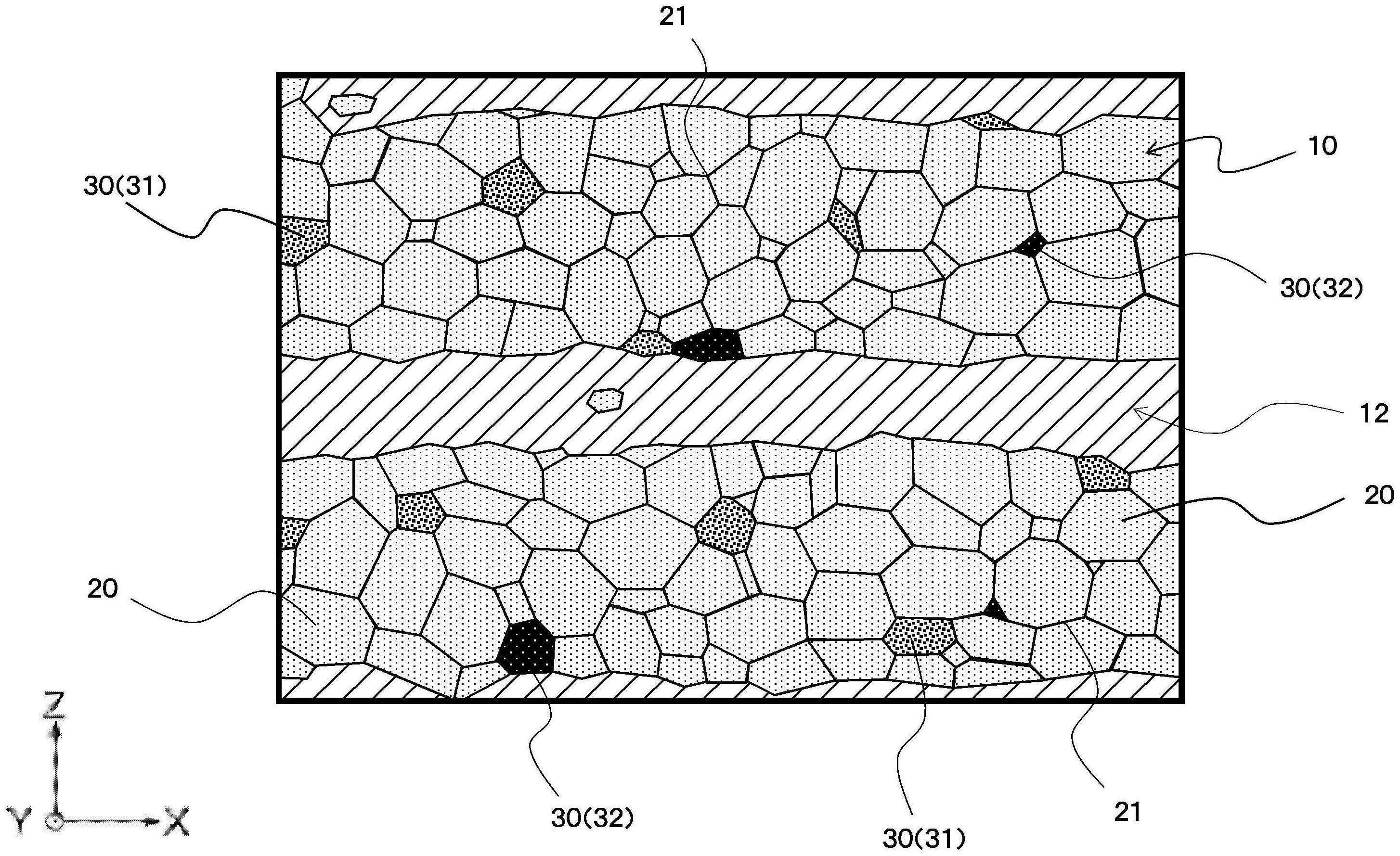

4、为了实现上述目的,本发明所涉及的电介质组合物包含:含有由组成式〔(caxsr(1-x))o〕m〔(tiyhfzzr(1-y-z))o2〕表示的主成分的电介质颗粒;位于上述电介质颗粒之间的晶界相;和至少包含ca、si和o(氧)的偏析相,上述组成式满足1.020<m,将上述偏析相中还含有mn的上述偏析相作为第一偏析相,将上述偏析相中实质上不含mn的上述偏析相作为第二偏析相,将电介质组合物的规定的截面积所含的上述第一偏析相的个数设为n1,将电介质组合物的规定的截面积所含的上述第二偏析相的个数设为n2,满足0.23<(n1/(n1+n2))≤1.00。

5、本发明的发明人进行了深入研究,结果发现,通过使电介质组合物具有上述特征,与以往相比能够降低脉冲耐压的不良率。

6、将上述第一偏析相中的mn的含有率以mno换算计设为mmn(摩尔%),将上述第一偏析相中的si的含有率以sio2换算计设为msi(摩尔%),优选上述第一偏析相满足0.38<(mmn/msi)≤1.30。

7、优选上述晶界相中的mn浓度比上述电介质颗粒的内部的mn浓度高,上述电介质颗粒具有mn浓度从晶界向颗粒中央降低的浓度梯度,实质上不具有al的浓度梯度。

8、本发明所涉及的层叠陶瓷电子部件具有陶瓷层和内部电极层,上述陶瓷层包含上述的电介质组合物,上述内部电极层与上述陶瓷层相接,将上述陶瓷层中的mn的含有率设为cd(摩尔%),将上述内部电极层中的mn的含有率设为cie(摩尔%),满足(cie/cd)<1.51。

9、通过层叠陶瓷电子部件具有上述的特征,与以往相比能够降低脉冲耐压的不良率。另外,该层叠陶瓷电子部件具有c0g特性,能够适合用作温度补偿用的电子部件。

技术特征:

1.一种电介质组合物,其包含:

2.根据权利要求1所述的电介质组合物,其中,

3.根据权利要求1或2所述的电介质组合物,其中,

4.一种层叠陶瓷电子部件,其具有陶瓷层和内部电极层,

技术总结

本发明的电介质组合物包含:含有由组成式〔(Ca<subgt;x</subgt;Sr<subgt;(1‑x)</subgt;)O〕<subgt;m</subgt;〔(Ti<subgt;y</subgt;Hf<subgt;z</subgt;Zr<subgt;(1‑y‑z)</subgt;)O<subgt;2</subgt;〕表示的主成分(1.020<m)的电介质颗粒;位于电介质颗粒之间的晶界相;和至少含有Ca、Si和O(氧)的偏析相。将偏析相中还含有Mn的偏析相作为第一偏析相,将偏析相中实质上不含Mn的偏析相作为第二偏析相。另外,将电介质组合物的规定的截面积所含的第一偏析相的个数设为N1,将电介质组合物的规定的截面积所含的第二偏析相的个数设为N2,电介质组合物满足0.23<(N1/(N1+N2))≤1.00。

技术研发人员:末田有一郎,相泽健吾,熊谷将太,庄司刚士,菅原智,樽谷政俊,山田笃志,熊谷学

受保护的技术使用者:TDK株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!