一种沟槽型碳化硅MOSFET器件及其制备方法与流程

本发明涉及一种半导体器件,尤其是一种沟槽型碳化硅mosfet器件及其制备方法。

背景技术:

1、碳化硅(silicon carbide)材料作为第三代宽禁带半导体材料的代表之一,与现有的硅材料相比,具有禁带宽度宽、临界击穿电场高、饱和漂移速度高等优势,以sic材料制备的mosfet器件,与相同耐压水平的硅基mosfet相比,又具有导通电阻低,尺寸小,开关速度快等优势,使其在大功率、高温及高频电力电子领域具有广阔的应用前景。

2、碳化硅功率mosfet器件结构的发展从ldmos(横向平面双扩散mosfet),vvmos(v型槽mosfet)到平面vdmos(垂直双扩散mosfet),再到沟槽型mosfet(trench mosfet)。ldmos结构简单,但扩散区和沟道区在器件表面,芯片面积利用率不高。vvmos是在芯片的背面形成漏极,所以扩散区和沟道区位于垂直方向,因此可以大大提高芯片的导通电流,但是vvmos的缺点是v型槽尖刺会导致电场集中而降低击穿电压特性。碳化硅沟槽mosfet与vdmos器件相比,导电沟道位于垂直方向,消除了平面vdmos的寄生jfet电阻,减小了元胞尺寸,提高了元胞密度,从而使得电流密度显著提高,大幅度降低了器件的导通电阻。

3、目前传统的沟槽型碳化硅mosfet器件结构如图2所示,其中主流的碳化硅沟槽栅结构都通过减小元胞尺寸的方式,提高电流密度,从而降低器件的导通电阻,但是随着元胞尺寸的减小,刻蚀沟槽的难度随之增加,这种方法也开始逐渐遇到了瓶颈。

技术实现思路

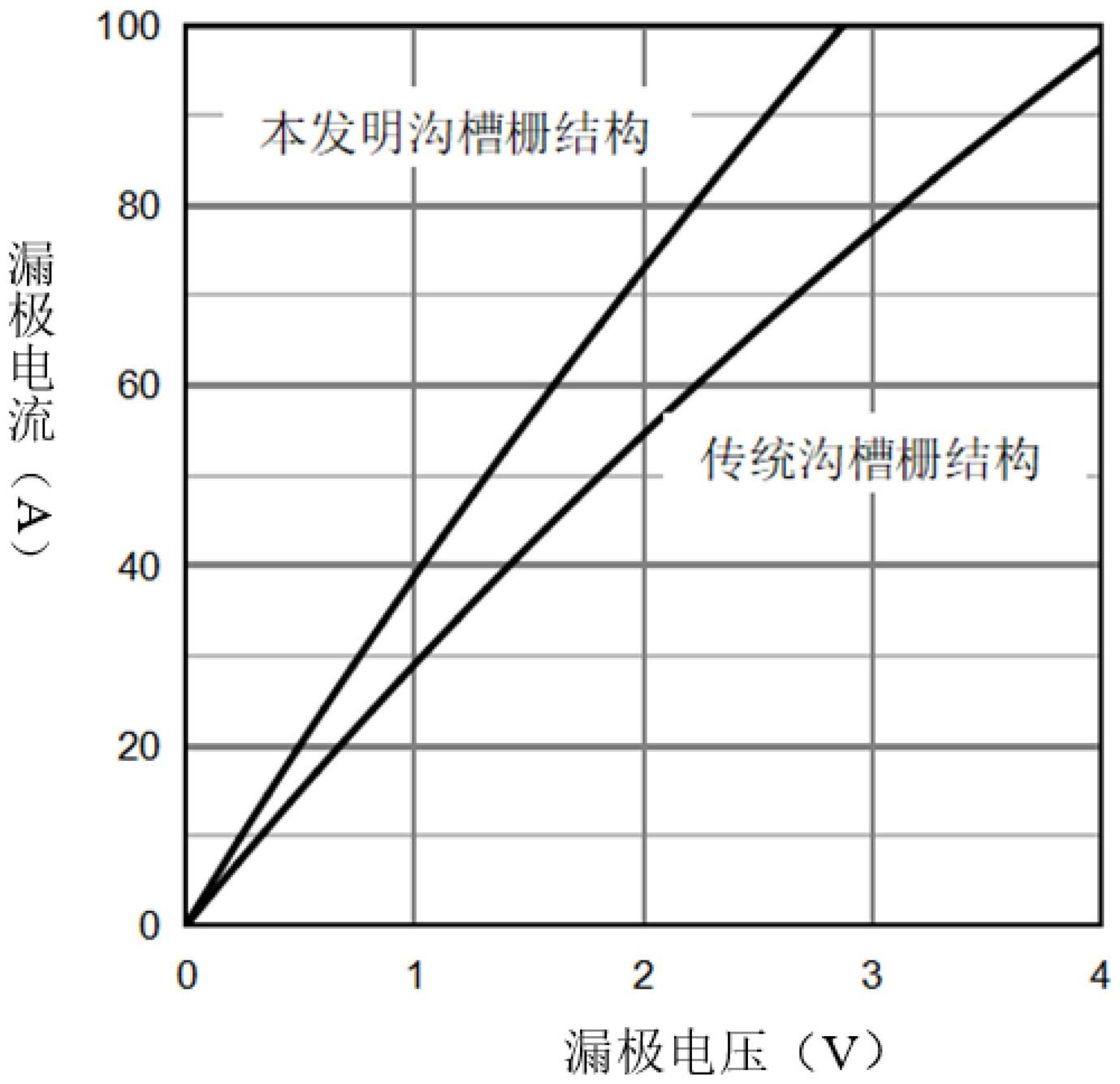

1、本发明的目的是提供一种沟槽型碳化硅mosfet器件及其制备方法,本结构在器件反向耐压状态时,栅极接地电位或者负电位,此时的p型屏蔽区与源极相连,能够保护栅极沟槽中的栅氧化层,提高器件的击穿电压,同时p型屏蔽区下方的处于n型外延层中的p型埋层区能够增加器件的横向耗尽,使得可以使用较高掺杂的n型外延层,大幅度降低器件的特征导通电阻,该结构与传统结构元胞相比,同样存在两条导电沟道。

2、为实现以上技术目的,本发明的技术方案是:

3、第一方面,本发明实施例提供了一种沟槽型碳化硅mosfet器件,包括漏极金属及所述漏极金属上方的n型衬底,在所述n型衬底上方依次为n型外延层、n型jfet区、p型体区以及n型源区和源极金属,其中n型外延层作为器件的漂移区,在所述n型外延层远离所述n型衬底的一端设有纵向沟槽,所述纵向沟槽贯穿所述n型源区以及p型体区,上端位于源极金属的内部,下端延伸至n型jfet区中,在所述纵向沟槽内部设有沟槽栅多晶硅,且所述沟槽栅多晶硅的上表面被栅极介质层覆盖,下表面和侧面被沟槽栅氧化层包裹;相邻两个纵向沟槽之间间隔设置p型屏蔽区,所述p型屏蔽区部分包裹所述纵向沟槽的表面,并且所述p型屏蔽区的上表面通过源极金属与n型源区相连接,所述p型屏蔽区的正下方设置有p型埋层区,所述p型埋层区穿过所述n型jfet区进入所述n型外延层中;

4、所述p型屏蔽区部分包裹所述纵向沟槽的外侧面和底部,所述p型屏蔽区的上端连接源极金属,下端延伸至n型jfet区内部;

5、所述p型埋层区上表面连接所述p型屏蔽区,下表面深入所述n型外延层中。

6、进一步地,相邻两个纵向沟槽构成一个元胞结构,其中元胞结构中存在两个栅极,除被p型屏蔽区所包裹的纵向沟槽两侧外还存在两条导电沟道。

7、进一步地,所述p型埋层区的掺杂浓度小于所述p型屏蔽区的掺杂浓度。

8、第二方面,本发明实施例提供了沟槽型碳化硅mosfet器件的制备方法,应用于第一方面所述的沟槽型碳化硅mosfet器件,包括以下步骤:

9、步骤一:选取n型衬底作为高浓度n型漏极,并生长n型外延层;

10、步骤二:在所述n型外延层远离n型衬底的一端注入施主离子形成n型jfet区;

11、步骤三:在所述n型外延层上,利用掩膜层选择性高能注入受主离子形成p型埋层区,并选择性注入受主离子形成p型体区;

12、步骤四:在所述n型外延层顶部,利用掩膜层选择性注入受主离子形成p型屏蔽区;

13、步骤五:在所述n型外延层顶部,利用掩膜层选择性刻蚀出纵向沟槽,所述纵向沟槽穿过p型体区延伸至n型jfet区中,并且纵向沟槽的深度小于所述p型屏蔽区的深度;

14、步骤六:在所述纵向沟槽内生长氧化层作为沟槽栅氧化层,并在所述纵向沟槽内淀积多晶硅形成沟槽栅多晶硅,去除多余的氧化层和多晶硅;

15、步骤七:在所述n型外延层表面淀积二氧化硅层,利用掩膜层选择性注入施主离子形成n型源区,接着选择性刻蚀,保留部分二氧化硅层形成栅极介质层;

16、步骤八:在所述n型外延层上表面和下表面分别淀积金属,形成源极金属和漏极金属。

17、第三方面,本发明实施例提供了一种沟槽型碳化硅mosfet器件的制备方法,应用于第一方面所述的沟槽型碳化硅mosfet器件,包括如下步骤:

18、步骤s1:选取n型衬底作为高浓度n型漏极,接着生长第一层n型外延层;

19、步骤s2:在所述第一层n型外延层上,利用掩膜层,选择性注入受主离子形成p型埋层区;

20、步骤s3:在所述第一层n型外延层顶部,通过外延生长的方法形成n型jfet区或者继续生长第二层外延层,用离子注入的方法注入施主离子形成n型jfet区;

21、步骤s4:在所述n型jfet区顶部,通过外延生长或者注入受主离子的方法形成p型体区;

22、步骤s5-s9同第二方面中的步骤四-步骤八。

23、与现有技术相比,本发明的主要优点如下:

24、本发明沟槽型碳化硅mosfet器件中的p型屏蔽区在器件反向耐压时对器件的栅极有良好的屏蔽作用,提高了栅氧可靠性,使得器件的击穿电压得到提高,同时器件结构中的p型埋层区通过离子注入的形式形成,设置于p型屏蔽区下方以及纵向沟槽的下方,伸入到n型外延层中,增加了n型外延层的横向耗尽,使得在设计器件时可以选用较高浓度的n型外延层,显著降低了器件的导通电阻。

技术特征:

1.一种沟槽型碳化硅mosfet器件,其特征在于,包括漏极金属(12)及所述漏极金属(12)上方的n型衬底(11),在所述n型衬底(11)上方依次为n型外延层(10)、n型jfet区(08)、p型体区(04)以及n型源区(03)和源极金属(01),其中n型外延层(10)作为器件的漂移区,在所述n型外延层(10)远离所述n型衬底(11)的一端设有纵向沟槽(07),所述纵向沟槽(07)贯穿所述n型源区(03)以及p型体区(04),上端位于源极金属(01)的内部,下端延伸至n型jfet区(08)中,在所述纵向沟槽(07)内部设有沟槽栅多晶硅(05),且所述沟槽栅多晶硅(05)的上表面被栅极介质层(02a)覆盖,下表面和侧面被沟槽栅氧化层(02b)包裹;相邻两个纵向沟槽(07)之间间隔设置p型屏蔽区(06),所述p型屏蔽区(06)部分包裹所述纵向沟槽(07)的表面,并且所述p型屏蔽区(06)的上表面通过源极金属(01)与n型源区(03)相连接,所述p型屏蔽区(06)的正下方设置有p型埋层区(09),所述p型埋层区(09)穿过所述n型jfet区(08)进入所述n型外延层(10)中;

2.根据权利要求1所述的沟槽型碳化硅mosfet器件,其特征在于,相邻两个纵向沟槽(07)构成一个元胞结构,其中元胞结构中存在两个栅极,除被p型屏蔽区(06)所包裹的纵向沟槽(07)两侧外还存在两条导电沟道。

3.根据权利要求1所述的沟槽型碳化硅mosfet器件,其特征在于,所述p型埋层区(09)的掺杂浓度小于所述p型屏蔽区(06)的掺杂浓度。

4.一种沟槽型碳化硅mosfet器件的制备方法,其特征在于,应用于如权利要求1所述的沟槽型碳化硅mosfet器件,包括以下步骤:

5.一种沟槽型碳化硅mosfet器件的制备方法,应用于如权利要求1所述的沟槽型碳化硅mosfet器件,其特征在于,包括如下步骤:

技术总结

本发明提供一种沟槽型碳化硅MOSFET器件及其制备方法,器件包括漏极金属及其上方的N型衬底、N型外延层、N型JFET区、P型体区、N型源区和源极金属,在N型外延层的一端设有纵向沟槽,纵向沟槽的上端位于源极金属的内部,下端延伸至N型JFET区中,在纵向沟槽内部设有沟槽栅多晶硅,且沟槽栅多晶硅的上表面被栅极介质层覆盖,下表面和侧面被沟槽栅氧化层包裹;相邻两个纵向沟槽之间间隔设置P型屏蔽区,P型屏蔽区部分包裹纵向沟槽的表面,并且P型屏蔽区的上表面通过源极金属与N型源区相连接,P型屏蔽区的正下方设置有P型埋层区,P型埋层区N型JFET区进入N型外延层中。本发明沟槽型碳化硅器件的导通电阻大大降低。

技术研发人员:朱袁正,杨卓,朱晨凯,黄薛佺,叶鹏

受保护的技术使用者:无锡新洁能股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!