一种半导体测试结构及其测试方法与流程

本发明涉及集成电路制造,尤其涉及一种可以检测金属硅化物残留和多晶硅连续性的半导体测试结构及其测试方法。

背景技术:

1、在半导体制造工艺中,为了降低接触电阻,广泛地应用金属硅化物(salicide)形成工艺。金属硅化物的形成过程为:首先在晶圆(wafer)表面沉积金属(镍、钛、钴等任一种),然后进行快速热退火;在恰当的工艺参数下,金属只与单晶硅(silicon)和多晶硅(poly silicon)反应,而不会与二氧化硅、氮化硅等硅化物发生反应,因此只有裸露的单晶硅衬底和多晶硅栅极的表面会生成金属硅化物,而在侧墙(spacer)上不会生成金属硅化物。但是,在不恰当的工艺参数下,金属硅化物可能覆盖在侧墙之上。热退火后会进行金属去除工艺,以除去未反应的多余金属,此时可能会有金属或金属硅化物残留在侧墙上,不能去除干净。若侧墙上存在金属或金属硅化物残留,则会造成栅极与有源区之间的短路,对电路造成影响。然而,目前检测侧墙上金属硅化物残留的技术甚少。

2、图1为现有技术中金属硅化物残留测试结构的剖面图。如图1所示,所述测试结构包括:形成于衬底(sub)10上的有源区(aa)11,形成于有源区11上的栅极结构12,形成于该栅极结构12侧壁的侧墙(spacer)13,以及形成于有源区11与栅极结构12表面的金属硅化物(salicide)14,金属硅化物14通过金属线19连接至相应的衬垫pad11~pad13。该栅极结构12包括多晶硅栅极121以及位于多晶硅栅极121与有源区11之间的栅氧化层(oxide)122。在半导体技术领域,将晶圆上做有源器件的区域称为有源区。

3、具体的,形成于有源区11表面的金属硅化物通过金属线19连接至衬垫pad12~pad13,形成于栅极结构12表面的金属硅化物14通过金属线19连接至衬垫pad11。测试时,通过在衬垫pad11和衬垫pad12之间施加电压,如果测得该两衬垫之间的电流值大于0,则说明该栅极结构12左侧(以用户正面图纸定义左、右方向)侧墙13上存在金属硅化物残留,此时该栅极结构12表面的金属硅化物、左侧侧墙13上残留的金属硅化物、以及有源区11表面的金属硅化物形成了电流通路,使得该两衬垫之间的电流值大于0;通过在衬垫pad11和衬垫pad13之间施加电压,如果测得该两衬垫之间的电流值大于0,则说明该栅极结构12右侧侧墙13上存在金属硅化物残留。反之,如果参与测试的两个衬垫之间的电流值等于0,则说明该两个衬垫之间的侧墙上不存在金属硅化物残留。

4、图2为现有技术中金属硅化物残留测试结构的俯视示意图。由图2可以看出,实际上栅极结构12的左、右、前、后(以用户正面图纸定义左、右、前、后方向)均存在侧墙13,这些部位的侧墙上均有可能存在金属硅化物残留。但是采用如图1所示现有技术的金属硅化物残留测试结构只能检测栅极结构12的左、右侧墙上是否存在金属硅化物残留,无法检测前、后侧墙上是否存在金属硅化物残留。此外,现有技术中金属硅化物残留测试结构对工艺制程不够敏感,不能有效捕捉工艺中存在的问题。

技术实现思路

1、本发明所要解决的技术问题是,提供一种半导体测试结构及其测试方法,可以有效检测栅极四周的侧墙上是否存在金属硅化物残留,还可以检测栅极的多晶硅连续性。

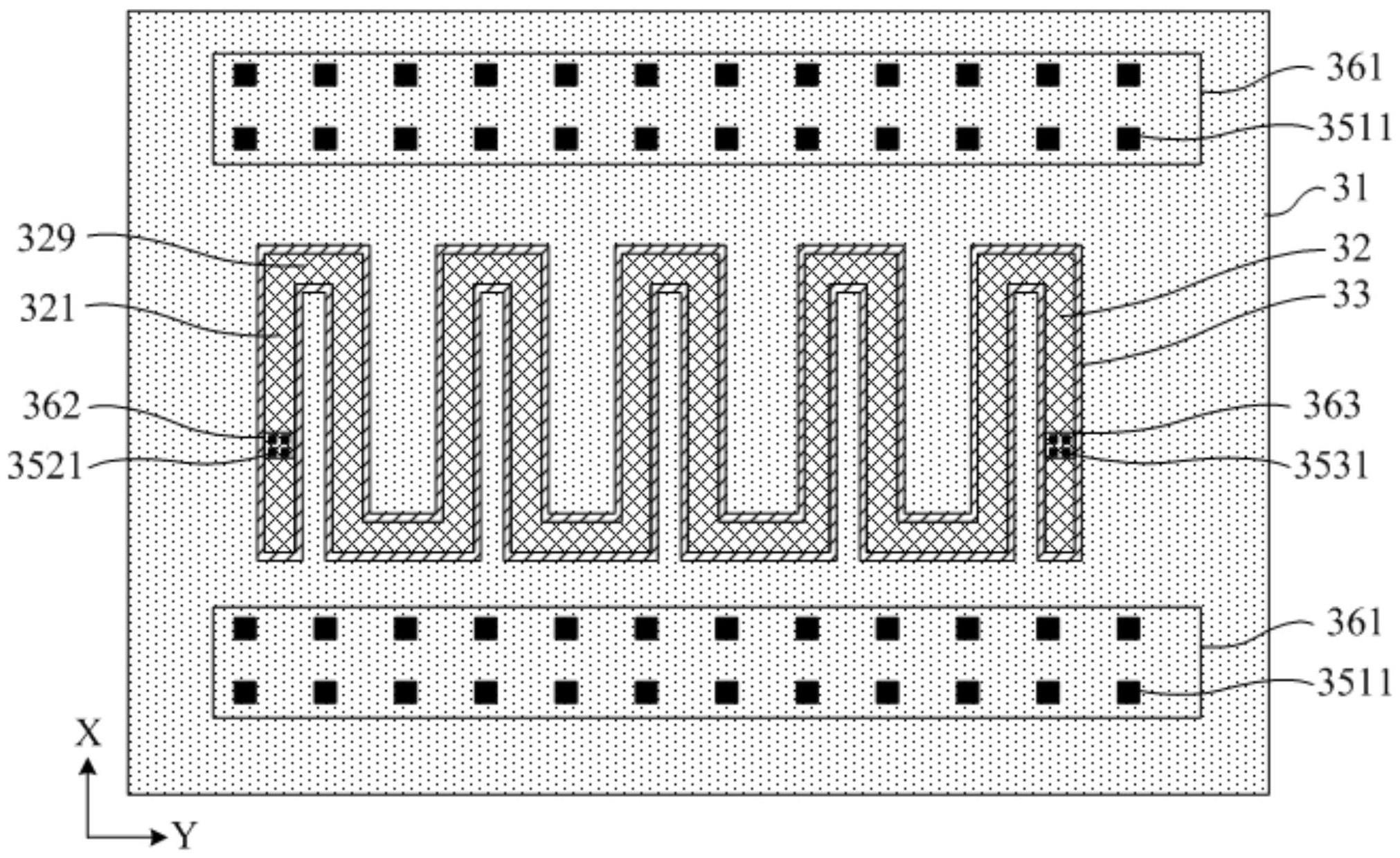

2、为解决上述问题,本发明一实施例提供了一种半导体测试结构,包括:衬底;有源区,形成于所述衬底上;多晶硅连接结构,形成于所述有源区上,所述多晶硅连接结构包括沿第一方向延伸、沿第二方向间隔分布的多个多晶硅结构,在所述第二方向上、相邻两个所述多晶硅结构通过多晶硅互连;侧墙,形成于所述有源区上且包覆所述多晶硅连接结构的所有侧壁;金属硅化物层,所述金属硅化物层包括覆盖所述有源区的第一金属硅化物,以及覆盖所述多晶硅连接结构的第二金属硅化物;金属互连结构组,所述金属互连结构组包括与所述第一金属硅化物相连的第一金属互连结构,以及与所述第二金属硅化物相连的第二金属互连结构;以及测试衬垫组,所述测试衬垫组包括与所述第一金属互连结构连接的第一衬垫,以及与所述第二金属互连结构连接的第二衬垫。

3、在一些实施例中,所述金属互连结构组还包括第三金属互连结构,所述第二金属互连结构与覆盖于所述多晶硅连接结构的首部的所述多晶硅结构上或该多晶硅结构的延伸部上的第二金属硅化物相连,所述第三金属互连结构与覆盖于所述多晶硅连接结构的尾部的多晶硅结构上或该多晶硅结构的延伸部上的第二金属硅化物相连;所述测试衬垫组还包括与所述第三金属互连结构连接的第三衬垫;其中,通过在所述第二衬垫上施加测试电压,检测所述第一衬垫上的第一电流以判断所述侧墙上是否存在金属硅化物残留,检测所述第三衬垫上的第三电流以检测所述多晶硅连接结构的多晶硅连续性以及所述金属硅化物层的形成质量。

4、为解决上述问题,本发明一实施例还提供了一种半导体测试结构的测试方法,包括:提供一半导体测试结构,所述半导体测试结构包括:衬底、有源区、多晶硅连接结构、侧墙、金属硅化物层、金属互连结构组以及测试衬垫组;所述有源区形成于所述衬底上,所述多晶硅连接结构形成于所述有源区上,所述多晶硅连接结构包括沿第一方向延伸、沿第二方向间隔分布的多个多晶硅结构,在所述第二方向上、相邻两个所述多晶硅结构通过多晶硅互连,所述侧墙形成于所述有源区上且包覆所述多晶硅连接结构的所有侧壁,所述金属硅化物层包括覆盖所述有源区的第一金属硅化物以及覆盖所述多晶硅连接结构的第二金属硅化物,所述金属互连结构组包括与所述第一金属硅化物相连的第一金属互连结构以及与所述第二金属硅化物相连的第二金属互连结构,所述测试衬垫组包括与所述第一金属互连结构连接的第一衬垫,以及与所述第二金属互连结构连接的第二衬垫;在所述第二衬垫上施加测试电压;检测所述第一衬垫上的第一电流,若所述第一电流大于0,则判定所述侧墙上存在金属硅化物残留。

5、在一些实施例中,当所述金属互连结构组还包括第三金属互连结构,所述第二金属互连结构与覆盖于所述多晶硅连接结构的首部的所述多晶硅结构上的第二金属硅化物相连,所述第三金属互连结构与覆盖于所述多晶硅连接结构的尾部的多晶硅结构上的第二金属硅化物相连;所述测试衬垫组还包括与所述第三金属互连结构连接的第三衬垫时;所述方法进一步包括:检测所述第三衬垫上的第三电流,若所述第三电流等于0、则判定所述多晶硅连接结构的多晶硅连续性受到损坏,若所述第三电流超出预设电流值范围、则判定所述金属硅化物层的形成质量出现问题。

6、以上技术方案,通过在有源区上形成多晶硅连接结构、并与多晶硅连接结构的四周均形成侧墙,再通过相应的金属互连结构以及测试衬垫,能够同时检测侧墙上的金属硅化物的残留、多晶硅连续性问题以及金属硅化物的形成质量问题。由于多晶硅连接结构全部位于有源区之上,因此能够同时检测多晶硅连接结构四周的侧墙上的金属硅化物残留;同时,由于多晶硅连接结构覆盖面积更大,因此对于工艺制程更加敏感,能够更好的捕捉工艺中发生的问题。

技术特征:

1.一种半导体测试结构,其特征在于,包括:

2.根据权利要求1所述的半导体测试结构,其特征在于,所述多晶硅连接结构为连续的蛇形多晶硅连接结构,所述第一方向垂直于所述第二方向或所述第一方向与所述第二方向之间具有夹角。

3.根据权利要求1所述的半导体测试结构,其特征在于,所述多晶硅结构包括:多晶硅层以及位于所述多晶硅层与所述有源区之间的氧化物层。

4.根据权利要求1所述的半导体测试结构,其特征在于,所述金属互连结构组还包括第三金属互连结构,所述第二金属互连结构与覆盖于所述多晶硅连接结构的首部的所述多晶硅结构上或该多晶硅结构的延伸部上的第二金属硅化物相连,所述第三金属互连结构与覆盖于所述多晶硅连接结构的尾部的多晶硅结构上或该多晶硅结构的延伸部上的第二金属硅化物相连;

5.根据权利要求4所述的半导体测试结构,其特征在于,

6.根据权利要求1所述的半导体测试结构,其特征在于,所述第一金属互连结构包括多个第一接触插塞,覆盖于所述多晶硅连接结构沿所述第二方向两侧的第一金属硅化物以及相邻两个所述多晶硅结构之间的所述有源区上的第一金属硅化物分别连接有所述第一接触插塞。

7.根据权利要求1所述的半导体测试结构,其特征在于,

8.根据权利要求1所述的半导体测试结构,其特征在于,所述衬底包括测试区及器件区,所述半导体测试结构形成于所述衬底的测试区上,所述器件区上形成有栅极结构,所述栅极结构与所述多晶硅连接结构采用相同制备工艺制备,且所述多晶硅结构的宽度和相邻两所述多晶硅结构之间的间距采用设计规则中的最小值。

9.一种半导体测试结构的测试方法,其特征在于,包括:

10.根据权利要求9所述的方法,其特征在于,当所述金属互连结构组还包括第三金属互连结构,所述第二金属互连结构与覆盖于所述多晶硅连接结构的首部的所述多晶硅结构上的第二金属硅化物相连,所述第三金属互连结构与覆盖于所述多晶硅连接结构的尾部的多晶硅结构上的第二金属硅化物相连;所述测试衬垫组还包括与所述第三金属互连结构连接的第三衬垫时;所述方法进一步包括:

技术总结

本发明公开了一种半导体测试结构及其测试方法。本发明通过在有源区上形成多晶硅连接结构、并与多晶硅连接结构的四周均形成侧墙,再通过相应的金属互连结构以及测试衬垫,能够同时检测侧墙上的金属硅化物的残留、多晶硅连续性问题以及金属硅化物的形成质量问题。由于多晶硅连接结构全部位于有源区之上,因此能够同时检测多晶硅连接结构四周的侧墙上的金属硅化物残留;同时,由于多晶硅连接结构覆盖面积更大,因此对于工艺制程更加敏感,能够更好的捕捉工艺中发生的问题。

技术研发人员:王春雨,叶亮,常建光

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!